多相滤波数字信道化的FPGA 实现

侯 聪

(中国西南电子技术研究所, 成都610036)

1 引 言

理想的电子战接收机应具备宽输入带宽、高灵敏度和分辨率、大动态范围以及多信号并行处理能力。通信领域软件无线电的成功应用[1],结合高性能的数字信号处理器件,提供了一种适应现代电子战需求的宽带数字信道化接收机模式。

多相滤波数字信道化技术[1-3]能满足数字信号处理中全频段、全概率覆盖、多信道并行接收的需求,并且多相滤波先抽取再滤波的结构,使得运算量和运算速率大大降低,便于硬件实现。

本文基于多相滤波结构,结合信道化接收机均匀DFT 滤波结构,采用50%信道重叠的方法,实现了全频段、全概率覆盖、全子信道并行接收的数字信道化功能。基于Xilinx Virtex4sx35 系列FPGA 实现的方法有较好的实用行,并且其思路在类似的设计中有较强的通用性。

2 多相滤波数字信道化结构

2.1 基于多相滤波结构的数字信道化

多相滤波结构是从抽取滤波转换而来,其根本原理是将传统抽取滤波先滤波、再抽取的处理过程,通过数学推导,等效变换为先抽取再滤波的过程,大大降低了计算量。

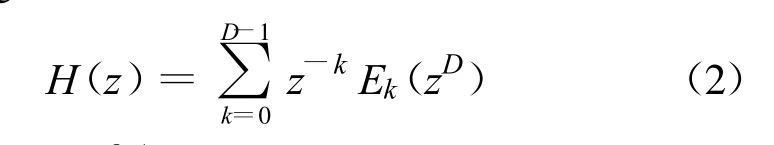

设FIR 滤波器转移函数为

式中,N 为滤波器长度。如果将冲激响应h(n)按以下列排列方式分成D 组,设N 为D 的整数倍,即N/D =Q,Q 为整数,对转移函数做分解组合:

图1 多相滤波结构Fig.1 Structure of polyphase filter

根据多相滤波结构和其推导方法,可以进一步延伸,将传统数字下变频先混频、再滤波、后抽取的结构,等效为先抽取、再滤波、后混频的多相下变频结构。

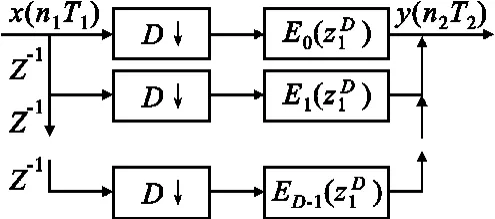

数字信道化的实现,可以等效视作对目标带宽进行若干个不同混频频率的数字下变频后,得到若个子信道的结果。如果设计所有子信道带宽相同,则每个子信道完成数字下变频时,可以使用相同的低通滤波器,仅仅混频序列的系数不同。因此,得到数字信道化的等效结构如图2 所示。

图2 基于多相滤波的数字信道化等效结构Fig.2 Equivalent structure of digital channel based on polyphase filter

图2 中,各分相下变频器的混频系数存在一定的数学关系,通过数学推导,可以将K 路分相下变频器等效为一个K 点的IFFT,得到数字信道化最终的等效高效结构。该结构实现了对输入信号同时进行D 路数字下变频,每路下变频的滤波带宽相同,抽取倍数均为D,混频频率为n ×f/D(其中n =0,1, …,D-1,f 为输入信号采样率)。

2.2 50%重叠的子信道划分

由于算法推算的条件限制和滤波器矩形系数的限制,多相滤波结构的数字信道化后,相邻子信道之间存在间隙,导致全频段接收时存在一定盲区的问题。为了解决接收盲区的问题,可以采用50%重叠的信道划分方式,在原来信道划分方式中两相邻子信道的通带间隙处,再增加一组子信道,增加的子信道中心频率在原两相邻子信道中心频率的二分之一处,并且新增子信道的低通滤波器也与原划分方式中的低通滤波器相同。这样划分后的相邻子信道滤波器通带部分相互覆盖,实现了信道化后的子信道通带覆盖整个处理带宽。

50%重叠的子信道划分实际可看作两组数字信道化的结果,区别在于两组信道化的混频频率相差二分之一子信道带宽。实现时,可以采用预处理加多相滤波的方式完成数字信道化。这样仅仅需要调整预处理部分的混频频率,就可以使用相同的多相滤波结构完成两组数字信道化。

3 多相滤波数字信道化的FPGA 实现

3.1 信道化主要指标和FPGA 实现流程

本文采用XILINX 公司的Virtex4sx35 系列FPGA实现了上述多相滤波数字信道化,使用的主要开发工具为ISE 和Chip Scope。

本设计实现的是短波宽带数字信道化在一片FPGA 内完成, 主要指标有:输入数据采样率16.384 MHz,输入带宽4 MHz,抽取倍数128、256、512可选(本设计中多相滤波的分支滤波阶数为20,在512 倍抽取下,其原型滤波器阶数为10 240,并行输出子信道数量为1 024),相邻子信道抑止大于等于80 dBm。

根据前文的分析和思路, 数字信道化在FPGA中实现的流程如图3 所示。FPGA 内完成数字信道化的主要功能,分为两路并行实现,多相滤波结果经过FFT 后,最终得到数字信道化结果,并且信道化后各子信道结果以串行方式输出,两路信道化后的子信道达到50%重叠的效果。通过外部的设置,可以改变预处理的混频频率、多相滤波的抽取倍数、多相滤波的原型滤波器系数、FFT 运算点数等参数。

图3 数字信道化在FPGA 中实现的流程图Fig.3 The flowchart of digital channel in FPGA

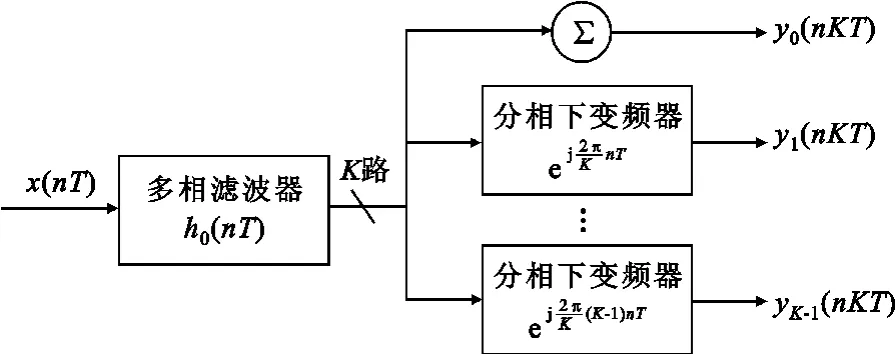

3.2 预处理的实现

本设计中预处理采用传统下变频方式完成,实现混频、滤波、2 倍抽取功能。实现结构如图4 所示,其中DDS 模块和低通滤波器都采用Core Generator 生成的IP 核实现。

图4 预处理实现结构Fig.4 Structure of pretreatment

3.3 多相滤波结构的实现

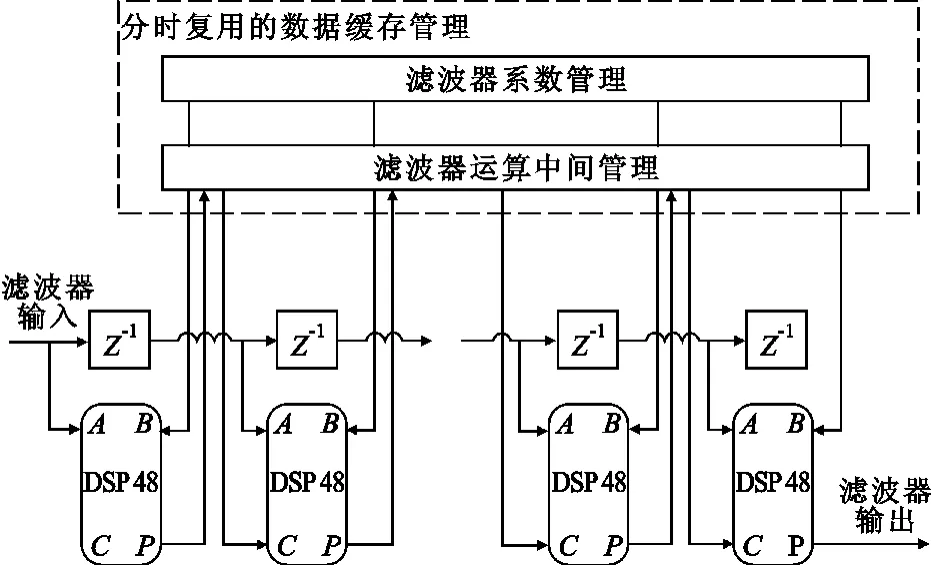

多相滤波结构的实现是FPGA 内实现数字信道化的核心。本设计根据多相滤波算法的特点,结合FPGA 流水线工作方式和FPGA 设计中时间面积互换的原则,采用分时复用的方式实现多相滤波,即构造多相滤波中一个分支的滤波器结构,利用多相滤波中抽取的特点,对该滤波器结构进行分时复用,仅用一个分支的滤波器结构实现所有分支的滤波运算,进而实现整个多相滤波结构。整个多相滤波结构主要分为滤波器结构的搭建以及数据缓存管理两部分,其结构如图5 所示。

图5 多相滤波结构的FPGA 实现Fig.5 Imp lementation of polyphase filter structure in FPGA

滤波器结构的搭建主要使用Virtex4 系列FPGA内的硬件资源DSP48,利用DSP48 可以轻松实现P=A×B +C 的功能,因此将若干DSP48 级连即可实现滤波器运算结构。

数据缓存主要使用FPGA 内的硬件资源Block RAM 实现。其设计目的在于,在分时复用的过程中管理每个DSP48 的输入输出数据,在多相滤波实现结构中,每个DSP48 需要3 个数据缓存区,一个对应滤波器系数,一个对应运算中间数据输入,一个对应运算中间数据输出。由于滤波器通过DSP48 级连实现,因此上一级DSP48 的数据输出缓存和下一级的数据输入缓存可以共用;再根据多相滤波算法和分时复用的设计思路,在每个缓存区内,地址编号就代表了多相滤波结构中的分支编号。

如果需要实现的多相滤波结构分支滤波器阶数为20,最大抽取倍数512,则通过上述方法实现一个多相滤波结构,需要的硬件资源大致有:DSP48 共20个,Block RAM(32×512)共40 个。

3.4 硬件资源统计

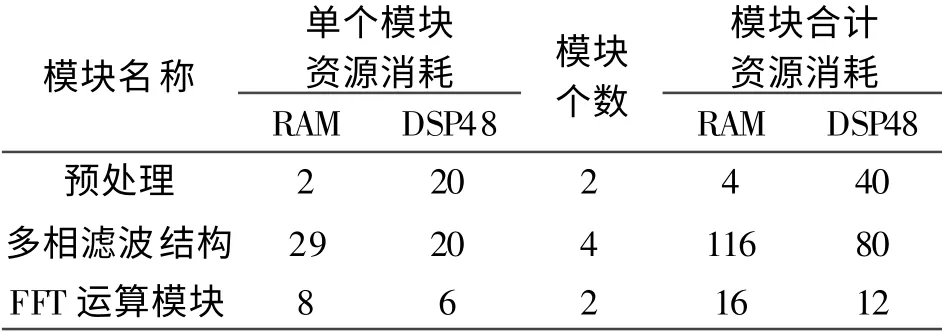

根据前面的设计分析,实现完整的全覆盖数字信道化需要两套预处理+多相滤波数字信道化。将数字信道化实现中的各模块资源消耗和模块数量统计,如表1 所示,可见,在一块Virtex4sx35 系列FPGA中能够实现上述数字信道化设计。

表1 FPGA 内资源消耗Table 1 Resources consump tion in FPGA

4 系统的调试

在FPGA 中实现数字信道化,不仅需要上述结构作为基础,还需要对整个系统进行调整,最主要的就是各模块、单元之间的时序调整,使得整个结构能够以流水线的方式工作起来,实现数字信道化的功能。系统的调试主要分为两大部分:分时复用多相滤波结构流水线的实现和FFT 模块及其输入输出的时序调试。调试主要分为两大步:代码编写时的功能仿真(采用Active HDL 软件)和后期板上运行调试(采用chip Scope 软件)。

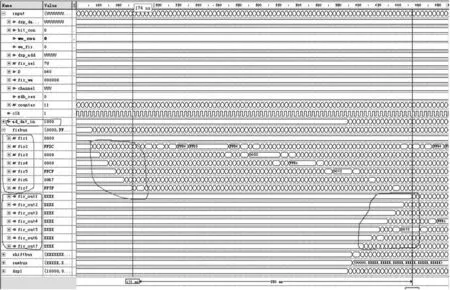

图6 所示是功能仿真调试分时复用的多相滤波结构,根据输入ad-dat-in 设置的值,考察滤波器系数的输出fir1 ~fir7 和滤波器的输出fir-out1 ~firout7,将其与理论值对比,作为调整设计的依据。

图6 多相滤波结构功能仿真调试Fig.6 Simu lation and debugging of polyphase filter structure

图7 所示是功能仿真多相滤波信道化的效果。输入一个单频信号,计算其所在子信道,考察该子信道及其相邻子信道的输出。由图可见,处于通带的子信道输出为一个抽取后的正弦波,与阻带子信道的输出相比,输出幅度小很多,达到了滤波的效果。

图7 数字信道化功能仿真调试Fig.1 Simulation and debugging of digital channel

5 结果验证

在信号处理板上验证数字信道化功能,主要方法为:使用信号源输入某频率单频信号,根据当前信道化的相关参数,推算该信号出现的子信道编号,将该子信道及相邻两子信道的信道化结果存储后,在Matlab 中计算其频谱,对比该频率在不同子信道中的信号强度,以验证数字信道化功能。经过实际测试,采用上述方法实现的数字信道化能够达到3.1节中的各项指标。

6 结束语

本文基于多相滤波结构,重点研究了基于Virtex4-SX35 芯片实现的数字信道化FPGA 设计方案,该方案实现了覆盖接收带宽全频段的、并行实时的数字信道化处理。仿真和实际电路测试均验证了数字信道化的功能,指标达到了要求。通过本文的研究得到以下结论:

(1)设计本身滤波性能好,实时性强,可并行输出所有子信道,抽取倍数高且可调,原型滤波器阶数高,实现资源消耗小,可以在一片Virtex4-SX35 中完成;

(2)方案实用性较强,虽然完成的是短波宽带数字信道化,但其设计思路通用性较强, 可应用于通信、电子侦察等领域的多通道数字信道化接收机的实现。

[1] 杨小牛, 楼才义,徐建良.软件无线电原理与应用[M] .北京:电子工业出版社,2001:21-87.

YANG Xiao-niu, LOU Cai-yi, XU Jian-liang.Software radio principle and application[M] .Beijing:Publishing House of Electronic Industry,2001:21-56.(in Chinese)

[2] 胡广书.数字信号处理(理论、算法与实现)[M] .北京:清华大学出版社,2004:179-191.

HU Guang-shu.Digital signal processing(theory, algorithm and realization)[ M] .Beijing:Tsinghua University Press,2004:179-191.(in Chinese)

[3] 宗孔德.多抽样率信号处理[M] .北京:清华大学出版社,1996:150-164.

ZONG Kong-de.Multirate signal processing[M] .Beijing:Tsinghua University Press, 1996:150-164.(in Chinese)