一种用于高速QPSK 解调的四次方环载波恢复电路

王志超 ,王平连

(1.中国科学院 光电研究院,北京100094;2.中国科学院 研究生院, 北京100094;

3.中国科学院 空间应用工程与技术中心, 北京100094)

1 引 言

QPSK 调制体制由于具有频带利用率高、抗干扰能力强及技术成熟等优点,被广泛应用于卫星数据传输系统中。近些年来,我国对地观测、空间遥感及航天事业发展迅速,对卫星到地面的数据传输速率需求不断提高,相应的地面站也需提升高速数据的接收解调能力。高速QPSK 信号解调大多采用相干解调方式,其关键技术之一是同步载波的恢复。

目前,国外全数字化高速解调器产品已较成熟,比如法国IN-SNEC 公司的某款通用遥感高码速率解调测试仿真设备 QPSK 解调码速率可达3.2 Gbit/s,相比之下,国内公开报道的实际应用产品较少,解调速率也较低,因此国内的数字化水平还有待提高。数字器件(如模数转换器)由于工作速率受限很难实现高码速率信号的全数字解调,这也是制约国内高速数据解调研究的技术瓶颈[1]。本文从解决实际问题的角度出发,采用模拟方案跨越该技术瓶颈,设计并实现了一种用于高码速率QPSK 信号的四次方环载波恢复电路。

2 四次方环恢复载波基本原理

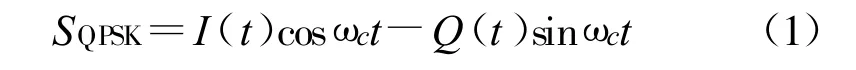

设QPSK 信号一般表达式为

式中,I(t)为同相分量,Q(t)为正交分量。对该信号进行四次方运算,可得:

因I(t)、Q(t)为矩形信号,故上式可化简为

由式(3)可见,QPSK 信号经四次方运算后已包含了4 ωc频率分量, 用一窄带滤波器将此离散的4 ωc频率分量滤出,经过分频用作锁相环的参考信号,通过锁相环的跟踪及窄带滤波作用,即可获得用于高速信号相干解调的高纯度同步载波[2-3]。据此,用四次方环恢复同步载波的框图如图1 所示,其中四次方由两次平方来实现。此方案主要针对中频载波为720 MHz、码速率在1 Gbit/s及以下QPSK 信号的载波同步。

图1 四次方环实现框图Fig.1 Block diagram of the fourth power loop

本方案的重点与难点在于宽带平方电路和锁相环电路的设计,同时也因篇幅所限,下面仅重点介绍此两种电路的设计与实现,其他电路如功分器、放大器等的设计读者可参考相关文献与书籍。

3 电路设计

3.1 宽带平方电路的设计

对微波信号进行平方运算一般想到的是使用集成的射频二倍频器来完成,然而本文中要进行平方运算的不是单载频,而是具有几百兆甚至千兆带宽的高速QPSK 信号,并且QPSK 信号经过平方运算后其带宽不变,这要求二倍频器具有超宽带的输入、输出频率范围,如此宽的频带范围集成倍频器很难做到。

鉴于倍频的本质是混频,故考虑采用混频器的上变频特性[4]来实现QPSK 信号的平方运算。本文中频载波720 MHz平方后为1 440 MHz,1 440 MHz再平方后为2 880 MHz,这就要求混频器中频和本振输入频率要覆盖720 MHz和1 440 MHz,射频输出频率要覆盖1 440 MHz和2 880 MHz, 同时还要有足够的频带余量保证QPSK 调制信号频谱有效通过。此外,混频器还应在宽频带范围内具有良好的变频损耗平坦度,保证经平方运算后的QPSK 信号不产生严重失真,这样才能将QPSK 调制谱的能量高效地转换为载波能量,得到高载噪比的载波分量。

经过大量调研与比较,最后选择了国外某公司一款集成混频器芯片,它具有非常高的线性度及超宽的频带范围,满足本文的频带要求,且具有较低的变频损耗,其基本特性见表1。

表1 集成混频芯片的基本特性Table 1 Character of integrated mixer

用此款混频芯片设计的平方电路原理图如图2所示。

图2 平方电路原理图Fig.2 Schematic of square circuit

图2 所示的电路中:本振为单端输入,由于混频芯片内部包含缓冲放大器并与50 Ψ阻抗匹配,故可以实现宽带操作;芯片本身中频输入和射频输出为差分端口,均使用变压器来实现双端到单端的转换,并在变压器外围加入了电感、电容,与变压器一起构成宽带匹配网络。图3 是该平方电路的PCB 版图,其中包含了必要的供电稳压电路。

图3 平方电路PCB 版图Fig.3 PCB of square circuit

第一、二级平方电路的版图相同,不同的只是输入、输出匹配网络。此平方电路的难点为在不同的工作频带内完成输入输出的宽带匹配。电路调试过程中,通过选用宽频带、低插入损耗的变压器以及调整输入、输出LC 匹配网络通频带的方法解决了该难点,使电路达到了较好的宽频带、低插入损耗性能。

3.2 分频及锁相环电路的设计

由于QPSK 信号经过四次方电路后得到的四倍载频为2 880 MHz,此信号频率较高很难直接用于鉴相,故需对其进行分频处理降低到合适的频率作为锁相环的参考信号,由锁相环对其锁定以完成载波的同步与提纯。

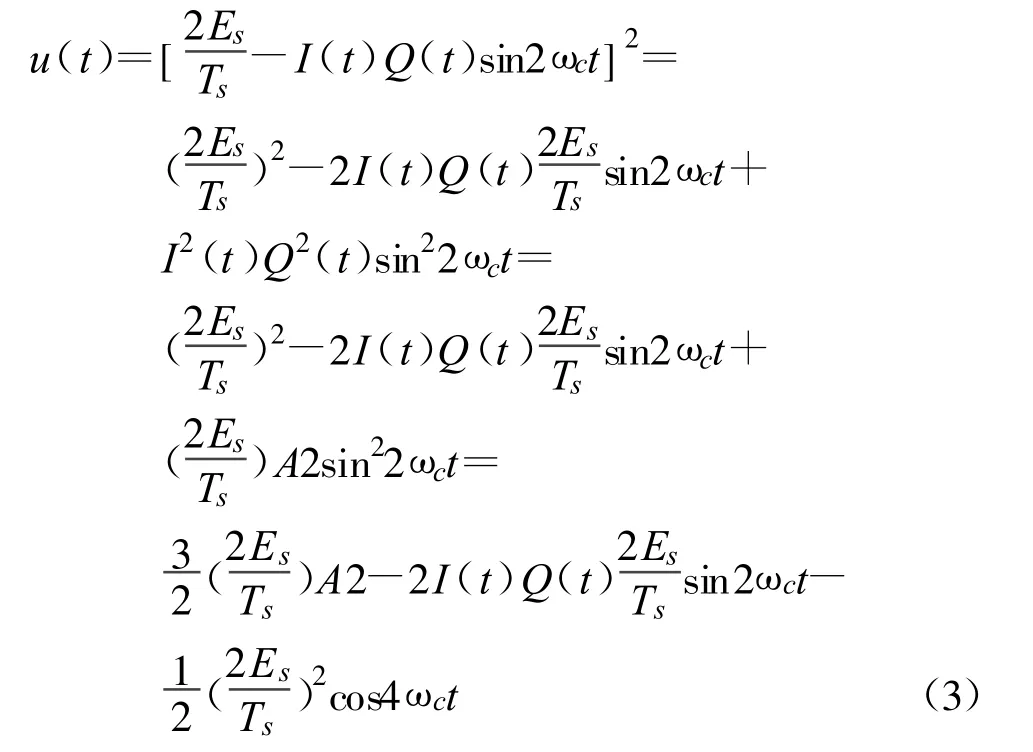

本文中分频器选用了一款集成可编程分频芯片,能够满足不同鉴相频率的需求;鉴相器为国外某公司的集成鉴频鉴相芯片,它具有超低噪声基底,可编程分频比和高鉴相频率等特点,其电性能指标如表2 所示。

表2 集成鉴频鉴相器的电性能Table 2 Electrical specifications of integrated phase-frequency detector

分频及锁相环电路原理图如图4 所示,其中的环路滤波器是重点设计内容。此处环路滤波器选用了有源比例积分滤波器,其模型如图5 所示,可通过调整R1、C1、R2、C2 的取值获得合适的环路带宽。

图4 锁相环电路原理图Fig.4 Schematic of PLL circuit

图5 环路滤波器Fig.5 Loop filter

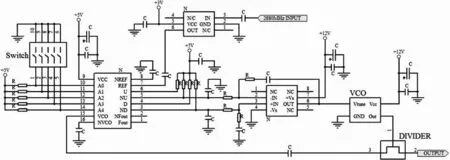

按照锁相环理论[5],环路滤波器中各电阻、电容的取值可由以下两式计算得出:

式中, ωn 为环路带宽;ξ为阻尼系数,通常取0.707;Kd 为鉴相器的鉴相灵敏度,本文所用鉴相器的Kd为0.286 V/rad;Kφ 为VCO 的压控灵敏度,本文中Kφ为5.5 MHz/V;N 为锁相环的分频比。根据式(4)、式(5),将C2 取定一值,则R1 和R2 即可计算得到。此外,C1的取值应满足C1<1/10 ωnR1。

经过调试,最终可编程分频器定为八分频,锁相环鉴相频率为360 MHz,环路带宽选为680 kHz,环路滤波器中各元件的取值分别为R1=120 Ψ, C1=100 pF,R 2=220 Ψ,C2=2 200 pF。

4 测试与分析

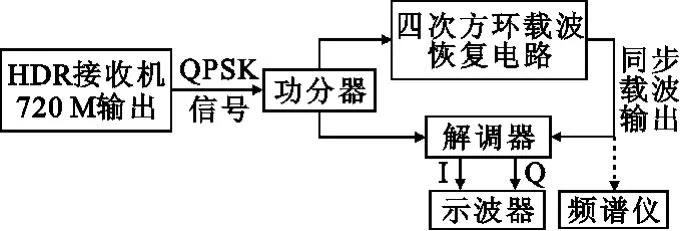

为检验本载波恢复电路的实际性能,对其进行了测试,测试框图如图6 所示。测试过程中,使用Cortex HDR 接收机的中频测试信号作为QPSK 调制源,其特点是当载频为720 MHz时QPSK 码速率在100 Mbit/s ~1 Gbit/s范围内连续可调, 缺点是无法输出未调制基带信号,因此下面的测试结果只能给出解调得到的I、Q 两路基带信号波形。示波器用来观察解调出的I、Q 两路基带信号波形,频谱仪用来观察恢复出的同步载波的频谱。

图6 载波恢复电路测试框图Fig.6 Test block diagram of carrier recovery circuit

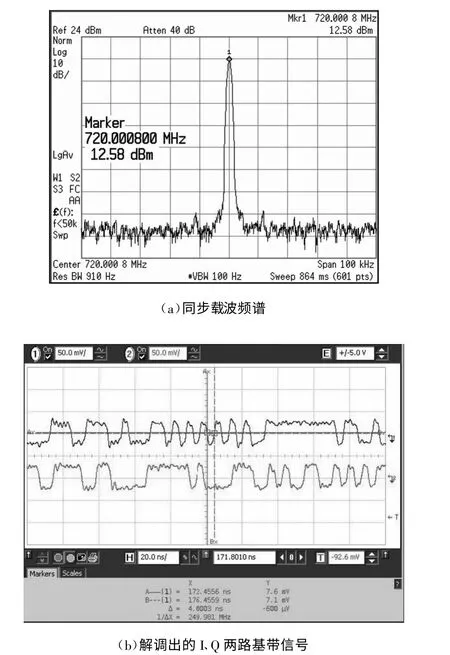

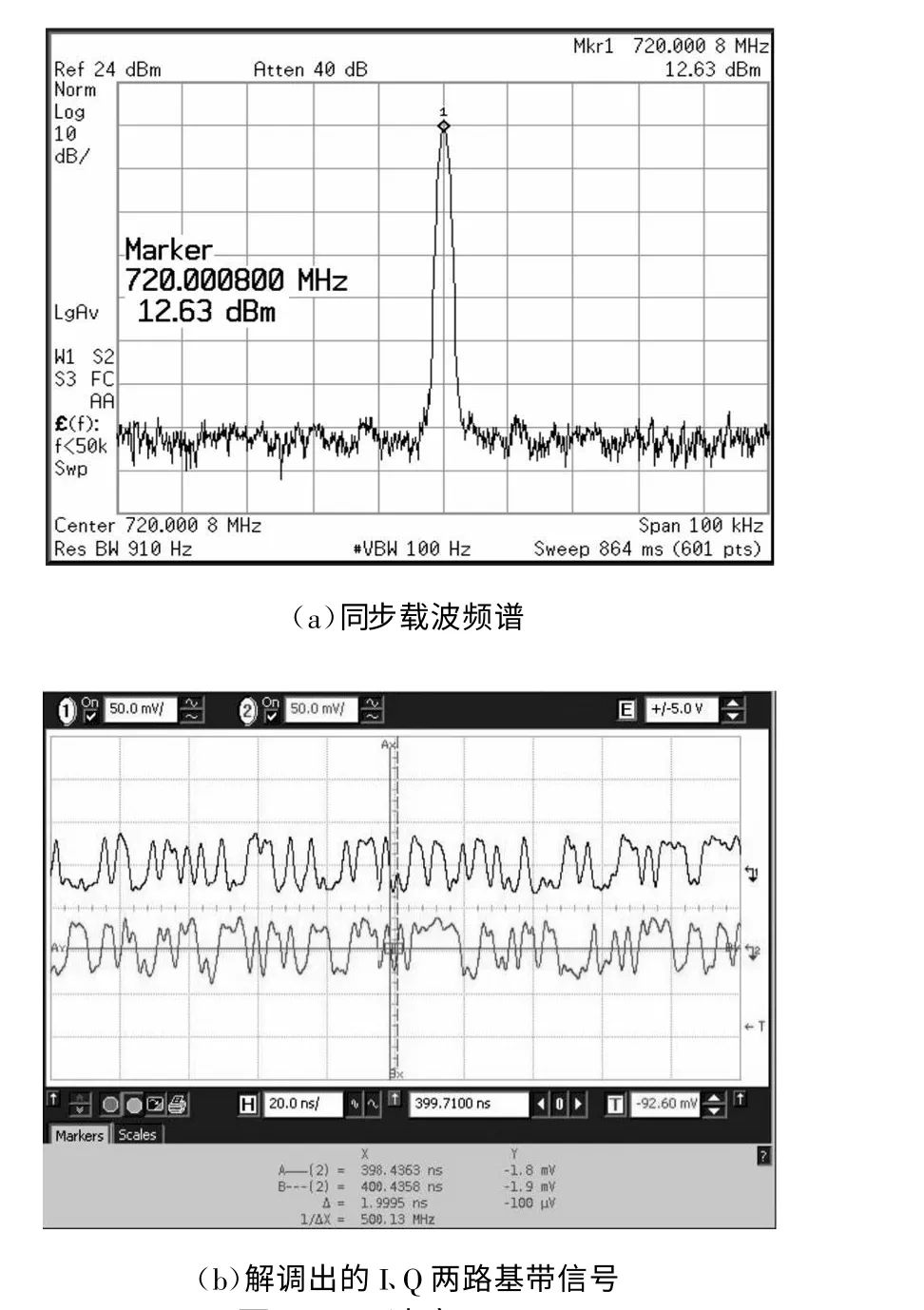

因篇幅所限, 下面仅给出当码速率为500 Mbit/s、700 Mbit/s、900 Mbit/s和1 Gbit/s时的测试结果。相应地,恢复出的同步载波频谱及解调出的I、Q 基带信号波形分别如图7 ~10 所示。

图7 码速率500 Mbit/sFig.7 Bit rate of 500 Mbit/s

图8 码速率700 Mbit/sFig.8 Bit rate of 700 Mbit/s

图9 码速率900 Mbit/sFig.9 Bit rate of 900 Mbit/s

图10 码速率1 Gbit/sFig.10 Bit rate of 1 Gbit/s

从测试结果可以看出,恢复出的同步载波相位噪声低并且纯度高,解调得到的基带信号从波形上看质量较好,虽然随着码速率的升高解调出的基带信号质量有所下降,但是在1 Gbit/s码速率时本四次方环电路仍能正常工作并恢复出同步载波,达到了预期目标。刘琼在文献[6]中使用了与本文电路结构不同的四次方环,但其最高工作码速率仅能达到325 Mbit/s,相比之下,本文实现的电路极大地提高了工作码速率,具有更广的适用性及更高的工程化参考价值。

5 结束语

本文设计并实现了一种基于四次方环的高速QPSK 信号同步载波恢复电路,重点描述了平方电路的宽带化设计和锁相环载波提取电路的设计。由实测结果可知,该电路可以完成载频720 MHz、码速率100 Mbit/s ~1 Gbit/s范围的QPSK 信号同步载波恢复,且应用提取出的同步载波实现了高速QPSK 信号相干解调。本文用模拟方案跨过了高码速率全数字解调的技术瓶颈,验证了模拟四次方环方案用于高速QPSK信号解调的可行性,解决了高速信号同步解调的关键技术问题,为下一步高码速率解调系统的工程化研制奠定了坚实的基础。

[1] 王波, 彭华,宋文政.一种用于高速率QPSK 信号的并行解调方法[ J] .电讯技术,2009,49(2):55-59.

WANG Bo,PENG Hua,SONG Wen-zheng.A Parallel Demodulation Method for High-rate QPSK Signal[J] .Telecommunication Engineering,2009,49(2):55-59.(in Chinese)

[2] 姚彦, 梅顺良, 高葆新, 等.数字微波中继通信工程[M] .北京:人民邮电出版社,1990.

YAO Yan, MEI Shun-liang, GAO Bao-xin,et al.Digital Microwave Relay Communication Engineering [ M] .Beijing:People′s Posts &Telecommunication Press, 1990.(in Chinese)

[3] 陈邦媛.射频通信电路[M] .2 版.北京:科学出版社,2006.

CHEN Bang-yuan.RF Communication Circuits[ M] .2nd ed.Beijing:Science Press, 2006.(in Chinese)

[4] Pozar D M.微波工程[M] .3 版.张肇仪, 周乐柱, 译.北京:电子工业出版社,2006.

Pozar D M.Microwave Engineering[M] .3rd ed.Translated by ZHANG Zhao-yi, ZHOU Le-zhu.Beijing:Publishing House of Electronics Industry,2006.(in Chinese)

[5] 张厥盛, 郑继禹, 万心平.锁相技术[M] .西安:西安电子科技大学出版社,2006.

ZHANG Jue-sheng, ZHENG Ji-yu, WAN Xin -ping.Phase-locked Technique[ M] .Xi′an:Xidian University Press, 2006.(in Chinese)

[6] 刘琼.高码速率QPSK 信号解调系统的研究[ D] .北京:中国科学院研究生院, 2008.

LIU Qiong.The Research on Demodulation System of Highrate QPSK Signal[ D] .Beijing:Graduate University of Chinese Academy of Sciences,2008.(in Chinese)