被动模式的芯片IIC接口设计

一、IIC接口特点及应用

IIC(Inter-Integrated Circuit)总线是一种由荷兰飞利浦(Philips)公司开发的两线式串行总线,用于连接微控制器及其外围设备。IIC总线产生于在80年代,最初为音频和视频设备开发,如今主要在服务器管理中使用,其中包括单个组件状态的通信。IIC总线最主要的优点是其简单性和有效性。由于接口直接在组件之上,因此IIC总线占用的空间非常小,减少了电路板的空间和芯片管脚的数量,降低了互联成本。IIC总线的另一个优点是,它支持多主控,其中任何能够进行发送和接收的设备都可以成为主总线。一个主控能够控制信号的传输和时钟频率,在任何时间点上只能有一个主控。IIC总线是由数据线SDA和时钟SCL构成的串行总线,可发送和接收数据。在CPU与被控IC之间、IC与IC之间进行双向传送。各种被控制电路均并联在这条总线上,但就像电话机一样只有拨通各自的号码才能工作,所以每个电路和模块都有唯一的地址,在信息的传输过程中,IIC总线上并接的每一模块电路既是主控器(或被控器),又是发送器(或接收器),这取决于它所要完成的功能。CPU发出的控制信号分为地址码和控制量两部分,地址码用来选址,即接通需要控制的电路,确定控制的种类;控制量决定该调整的类别(如对比度、亮度等)及需要调整的量。这样,各控制电路虽然挂在同一条总线上,却 彼此独立,互不相关。

图1 被动模式IIC接口电路框图

二、被动模式的芯片IIC接口设计

在实际设计芯片与计算机接口电路时,通常只希望计算机能够检测、控制芯片的内部工作情况,因此可以简化IIC接口电路,只需要实现处于被动模式的芯片IIC接口电路即可。该接口电路主要用于芯片内部寄存器的读写操作,这样可以减小占用过多的芯片面积资源。

根据IIC总线上数据传输过程的特点,使用状态机控制整个系统的运作,可以使设计思路清晰明确,程序模块化。系统上电复位后即进入状态机,并在状态机控制下完成起始/停止信号的自动检测,slave地址、子地址、配置数据的接收及响应,发送数据及检测响应,对配置寄存器阵列的寻址和连续读写等功能。此外,系统最高数据传输速度应由时钟CLK及寄存器的存取速度决定。根据电路的功能,整个IIC接口电路的系统框图如图1所示。

状态机如图2所示,其中Idle是空闲状态,Rx_address状态接收slave地址,Ack_rx_address状态接收slave地址响应,Tx_data状态发送数据,Ack_tx_data状态发送数据响应,Rx_subaddress状态接收子地址,Ack_rx_subaddr状态接收子地址响应,Rx_data状态接收数据,Ack_rx_data状态接收数据响应。状态机的状态转换在SCL下降沿后第5个时钟周期进行,但是,停止信号出现后,总线被释放,SCL/SDA均为高电平,除非再出现起始信号进行数据传送,SCL不会再出现下降沿。如果停止信号出现后,就把空闲状态赋给下一个状态,将没有SCL时钟下降沿做时间基准完成状态转化(即状态机进入到空闲状态)。为了解决这个问题,需要将停止信号看作复位信号。一旦有停止信号出现,当前状态在下一个CLK脉冲强制进入到空闲状态,而不再等到SCL下降后第5个时钟脉冲。

图2 被动模式IIC接口电路状态机

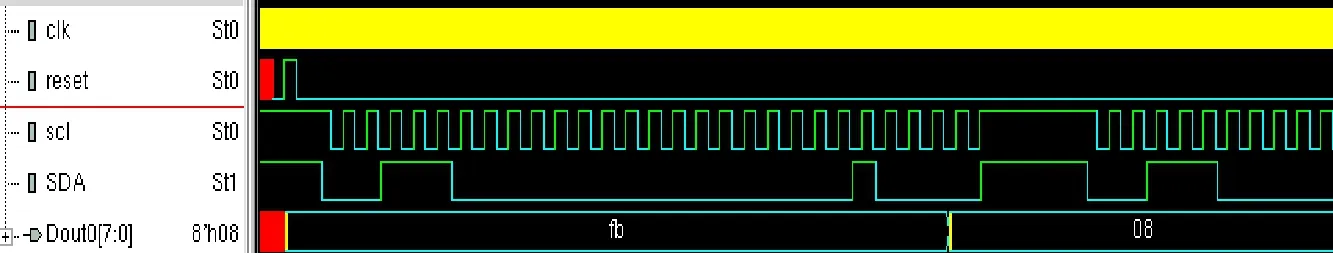

图3 被动模式IIC接口电路仿真波形

Ack_rx_subaddr状态之后,master既可能发送数据又可能发送重复停止信号或者停止信号,如何区分是哪种情况成为正确进入相应的状态的关键。这里设定ack_rx_subaddr状态之后无条件紧跟rx_data状态。这样,如果在rx_data状态时检测到重复起始信号,丢弃已经接收的数据,并在SCL时钟下降沿后第5个时钟周期进行状态转化进入rx_address状态,否则继续完成接收数据。若发现停止信号,处理如前所述。这样做既满足设计要求又不会增加多余的状态。

master收到数据后没有响应(SDA=1)表示master接收的是最后一个字节数据。在这种情况下,可以在SCL时钟下降沿后第5个时钟周期就直接进入到空闲状态,处理接下来应该出现的重复起始信号或停止信号。

起始/停止信号、SCL检测如下:

在高速时钟CLK的上升沿采样SDA、SCL,如果在前后两个采样点发现SDA从“1”变化到“0”而SCL保持“1”则认为master发出起始信号,将detect_start设置为有效。同理,若发现SDA从“0”变化到“1”而SCL保持“1”,则认为是停止信号,将detect_stop设置为有效。detect_start有效保持一个状态周期,detect_stop有效保持一个时钟周期,以避免误操作。

依靠SCL时钟下降沿进行状态转换以及在SCL时钟上升沿将SDA的数据送入移位寄存器。移位寄存器在rx_address、rx_subaddress、rx_data状态完成在数据采样时刻(SDA数据有效时)对slave地址、寄存器子地址、数据的移位接收,接收完毕后在响应状态将数据并行送往指定的寄存器,在ack_tx_data状态和ack_rx_address状态且读写控制位为高(r/w=1)时,并行输入数据,在tx_data状态发送时刻有效时输出最高位,在数据采样时刻有效时进行移位操作。

寄存器子地址寄存器实现完成对寄存器一次读写操作后地址自动增加的功能,这样可以实现在对器件的配置时只输入一次子地址就完成对所有的配置寄存器的配置。计数器寄存器记录接收或发送的数据的位数,为状态机提供控制信号。

三、被动模式的芯片IIC接口验证

根据上面的状态机,使用verilog编写硬件描述代码,为了减小竞争冒险、提高电路运行的可考性,所有电路均在同一时钟控制下工作,例如,状态转化并没有依靠SCL时钟的下降沿触发,而是利用高速时钟的上升沿采样SCL,检测到SCL时钟的下降沿后,在时钟的上升沿触发状态转化。这样就避免了由于总线负载过重而导致SCL上升、下降时间太长所带来的一系列问题。代码编写好后,运用modelsim进行仿真验证,仿真验证设计的IIC接口工作正确。图3是计算机对IIC接口电路进行写操作仿真得到的CLK、SCL、SDA波形,刚开始时,reset有个高电平脉冲,IIC模块复位,IIC中第一个寄存器的数据Dout0[7∶0]被置为fb(16进制),之后开始对IIC的第一个寄存器写入数据08,最终Dout0[7∶0]中的数据从fb为08,表明计算机成功完成了对芯片寄存器的控制。

四、结语

被动模式的IIC接口电路是IIC总线的一个简化版本,通过被动模式的IIC接口电路,计算机可以检测、控制芯片的状况,本文分析了被动模式的芯片IIC接口设计,并通过modelsim验证设计的正确性。

[1]徐伟,刘建成.基于模拟IIC总线的电压测量系统[J].南京信息工程大学学报,2011,1.

[2]王钰,潘仕彬,王卉.IIC在数据采集中的应用[J].科技广场,2008,8.

[3]张文甲.IIC总线通信中主机控制器的设计与应用[J].电脑知识与技术,2007,1.

[4]徐广振,张茂青,王力,黄颖.基于IIC总线的键盘读取[J].江苏电器,2007,4.

[5]夏宇闻.verilog数字系统设计教程[M].北京航空航天大学出版社,2008.