基于FPGA的生物电阻抗成像系统设计*

丁忠林 ,陈晓艳 ,吴佳妮

(1.天津科技大学 计算科学技术与信息工程学院,天津 300222;2.天津科技大学 电子信息与自动化学院,天津 300222)

电阻抗断层成像技术EIT(Electrical Impedance Tomography)即生物电阻抗成像技术(Bioelectrical Impedance Tomography),根据人体内部组织电特性参数(电阻率等)的不同(即不同的组织)在不同的生理、病理状态下具有不同的电特性参数的原理,通过对其表面施加安全激励电流(或电压),同时测量物体表面的电压(或电流)信号来获知物体内部的电阻率分布,从而得到反映物体内部组织特性的电导率断层图像[1]。生物电阻抗成像技术是当今生物医学工程学重大研究课题之一,利用生物组织或器官的电特性及其变化,提取与病理状况相关的生物医学信息,是继形态、结构成像之后,近20年出现的新一代功能成像技术[2]。EIT是功能成像,虽然在分辨力等方面不如结构成像(CT),但是能够反映内部组织的生理变化,作为新的医学成像技术具有较高的临床应用价值,具有无创、无辐射、成本低廉等优点。CT、超声波、核磁等成像时会对人体产生伤害而且价格昂贵,不易连续进行检测,但EIT克服了以上缺点,所以电阻抗成像技术被广泛地应用于心、肺、脑、胃及相关循环系统的研究中。电阻抗断层成像系统国外研究发展较早,在ECT和ERT系统的研究中,一些机构研制出了各自的硬件系统,但其系统结构复杂、成本高,对其广泛应用研究和推广具有局限性。因此,本文设计了以Spartan3E系列XC3S500E型号的 FPGA为核心的生物电阻抗成像系统由嵌入8 bit微处理器PicoBlaze实现逻辑控制产生激励信号和高速A/D采集,实现数字解调并通过 RS232将采集数据传输到PC机,重建人体内部的电阻率分布或其变化图像的16电极生物电阻抗成像系统。系统结构简单、成本低、工作性能稳定和精度较高,为电阻抗断层成像技术被广泛应用研究提供了一种硬件设计方案。

1 生物电阻抗成像技术原理与EIT系统

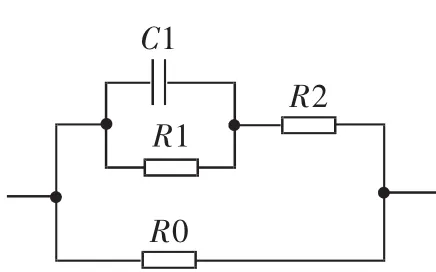

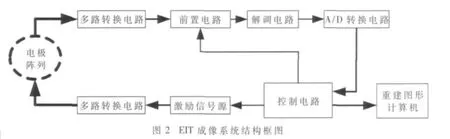

人体可以看成是由一定数量的具有不同电阻抗特性的空间分布的组织组成的复合导体。生物组织的电导性与金属导体不同,它主要由离子的运动而不是由电荷的运动形成。生物组织的阻抗特性与许多因素有关,包括温度、频率及组织的各向异性等。其中生物组织阻抗的频率特性是设计EIT系统需要考虑的主要因素。生物组织是由大量细胞和细胞之间的液体组成的,其中细胞又由细胞膜和细胞质组成,且不同的组织与器官有不同的阻抗特性。用于生物测量的电流进入生物组织时(电流在人体内的分布特性还与注入电流的频率有关),电流将呈三维发散,指向性不强。研究表明,生物组织细胞内液和细胞外液具有很好的导电性,可视为纯电阻,细胞膜和组织界面等则表现为电容性。在低频情况下,电流主要通过细胞外液,而细胞膜容抗很大,细胞可视为绝缘体。随着频率的增加,细胞膜容抗逐渐下降,细胞将参与导电,生物组织的整体阻抗值随频率的增加而减小[3]。细胞的电特性模型如图1所示,其中,电阻R1和电容 C1代表细胞膜,R0、R2分别代表细胞内外的流质。如果通过在生物目标物体四周安放电极阵列并注入交流电流,则会产生电流场,同时通过电极测量目标物体表面的电位,由注入的交流电流和测量的电压数据可以重构出目标物体横截面内电导率的空间分布,从而得到电阻抗断层图像。根据以上原理,EIT系统应包括电极阵列、数据采集系统和重建图像计算机三部分,如图2所示。电极阵列固定在被测目标物体周围向物体输入激励电流。数据采集系统主要包括精准的激励恒流源、多路转换电路、前置电路、A/D转换电路、解调电路和控制电路等。恒流源的作用是产生安全的正弦激励电流,实现高精度的恒流输出。多路转换电路是对不同电极测量时进行切换。前置电路是对信号进行放大处理。A/D转换电路是对测量信号进行模数转换。解调电路是要从信号中解调出有用的阻抗信息。控制电路主要是负责激励源及测量电路的参数设置以及将采集到的数据传输到重建图像计算机中。重建图像计算机主要是用数据采集系统得到的数据,采用一定的算法重建出反映阻抗信息的图像。

图1 细胞的电特性模型

2 基于FPGA的EIT成像系统设计和实现

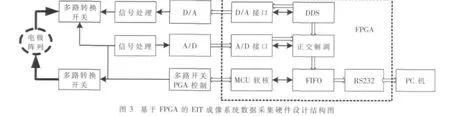

EIT成像系统主要是主从式方式,以高性能单片机(或DSP、FPGA)作为下位机完成数据采集,上位PC机完成图像重建算法及图像显示。本文采用FPGA作为下位机,FPGA芯片选择Spartan3E系列的XC3S500E芯片,其内部具有丰富的可配置资源,可内嵌8 bit微处理器PicoBlaze软核,用户可以根据需求充分利用这些资源在FPGA内部构建各个硬件功能模块及其接口,且很多功能模块都有厂商提供的知识产权核IP核可以使用,参数设置方便、功能齐全。系统具有结构简单、成本低、工作性能稳定等特点。

2.1 硬件系统设计

根据图2,基于FPGA的EIT成像系统硬件设计结构图如图3所示。系统由激励源(DDS)、模拟多路开关阵列及其逻辑控制(MCU)、信号处理电路、正交序列解调、数据缓存(FIFO)和通信接口(RS232)六部分构成,其中激励源、逻辑控制、正交序列解调、数据缓存和通信接口都通过FPGA芯片XC3S500E实现。系统的工作原理是:FPGA的DDS产生100 kHz正弦激励信号,经过处理变成5 mA电流信号,通过多路转换开关加到电极阵列中的一个电极上,A/D分别采样相邻电极之间的电压信号,经正交解调后将电阻信息存到FIFO中。经过电极轮流激励和采集得到一组采样信息,通过RS232传输到上位PC机中进行图像的重建。

2.1.1 激励源

在EIT数据采集系统中有多种测量方式,本设计采用电流驱动电压测量方式,故激励源设计成正弦恒流源。考虑到激励源是EIT数据采集系统的核心,其输出信号的频率决定着系统的工作频率,其性能直接决定了系统最终的精度,所以对激励源信号的稳定性、精确性、动态范围及信噪比等的要求都比较高。为了满足以上要求,设计中采用直接数字合成技术(DDS技术)设计实现可编程的电流源,调用Xilinx公司开发软件提供的IP核DDS编译器,利用FPGA的资源在其内部构造DDS模块;然后外加高速的数模转换器AD9754和巴特沃斯二阶低通滤波电路,得到正弦电压信号;最后再经过电压控制电流源电路得到正弦恒流源。

本设计中设置DDS输入时钟频率为125 MHz,输出正余弦信号的频率为100 kHz,无杂散动态范围为80DB,频率分辨率为0.023 4 Hz。其中,频率与相位的设定是由相位增量控制字PINC与相位偏移量控制字POFF所决定的。相位增量控制字PINC与输出频率的关系为:

其中,Bθ(n)为相位累加器的宽度,fout为输出频率,fclk为输入频率。

相位偏移量控制字POFF与初始相位的关系为:

其中,φ为初始相位。通过改变相位增量控制字POFF实现相位连续可调[4]。

本设计中,上位PC机可以通过串口发送32位的PINC和32位的POFF给FPGA来实现激励源的频率和相位调节。例如,当激励源频率设为100 kHz时,PINC=0068DB8BH;当激励源频率为50 kHz时,PINC=00346DC5H。

根据DDS技术的原理和结构特点,输出的模拟正弦波中含有大量的杂散谱线,需经过低通滤波器使波形平滑。由于巴特沃斯二阶低通滤波器的幅频响应在通带中具有最大平坦度,且结构简单、容易实现,故本设计采用由AD8066构成的巴特沃斯二阶低通滤波器。

2.1.2 模拟开关阵列及其控制逻辑

本系统设计成16个电极的串行系统,即只有一个激励源和一个电压测量模块,因而需要通过模拟开关阵列在EIT数据采集时进行激励电极对与测量电极对的选择切换。本设计采用相邻电流激励、相邻电压测量模式。设计中采用4片8选1的模拟开关芯片MAX4598来完成16路的电流激励选通功能。MAX4598各通道的导通电阻为45 Ω,选通电阻通道间不匹配小于 4 Ω,通道间的串扰抑制为-80 dB(1 MHz),开关关断抑制为-90 dB(1 MHz)。采用1片8×16模拟开关阵列芯片MT8816来完成16路的电压测量选通功能。MT8816具有失真小、开关带宽大、导通电阻小等特性,可以降低应用多对模拟开关造成的电路的复杂性和不稳定性,提高了系统的可靠性以及各通道的一致性。

为了完成对4片MAX4598和1片MT8816的通道选通控制需要23个端口引脚。考虑到所选用的FPGA输入输出I/O引脚有限,所以使用4片74HC574SJ来完成对MAX4598和MT8816的控制,只需用到12个I/O引脚就可以满足要求,节省了FPGA的资源。

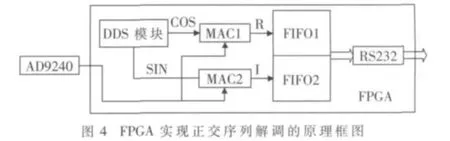

2.1.3 正交序列解调

设计中充分利用FPGA的IP核资源,采用正交序列解调方法,其优点是:一方面可以克服模拟解调的缺点,提高系统的精度[5];另一方面使用IP核资源,省时省力、性能可靠。FPGA实现正交序列解调的原理框图如图4所示。利用FPGA内部的DDS模块在产生正弦激励信号的同时产生同频率的正余弦参考信号,保证了正交序列解调中参考信号的频率和激励信号的频率完全一样,进而保证了解调结果的准确性。将AD9240输出的数字信号通过接口送入FPGA内部,使用Xilinx公司提供的IP核MAC乘累加器进行乘累加,从而得到测量电压的实部信息和虚部信息,并存入数据缓存器FIFO中。本设计中IP核MAC的累加次数设置为300(即300个采样点计算出一个实部信息和一个虚部信息)。

2.1.4 数据缓存和通信接口

本系统由16个电极完成16次激励,每次激励测量 13次电压,与激励电极相邻的两对电极不测量,完成一幅图像重构需要208个数据。设计中,在ISE9.2i中调用IP核生成器分别构建了两个深度为1 024、写宽度为32 bit、读宽度为8 bit的异步先进先出存储器FIFO,将每次正交序列解调后得到的实部信息和虚部信息分别存放到FIFO1和FIFO2中。每采集到一个数据经过解调存入FIFO1和FIFO2中后,立即通过串口发送给上位PC机。

2.2 软件设计

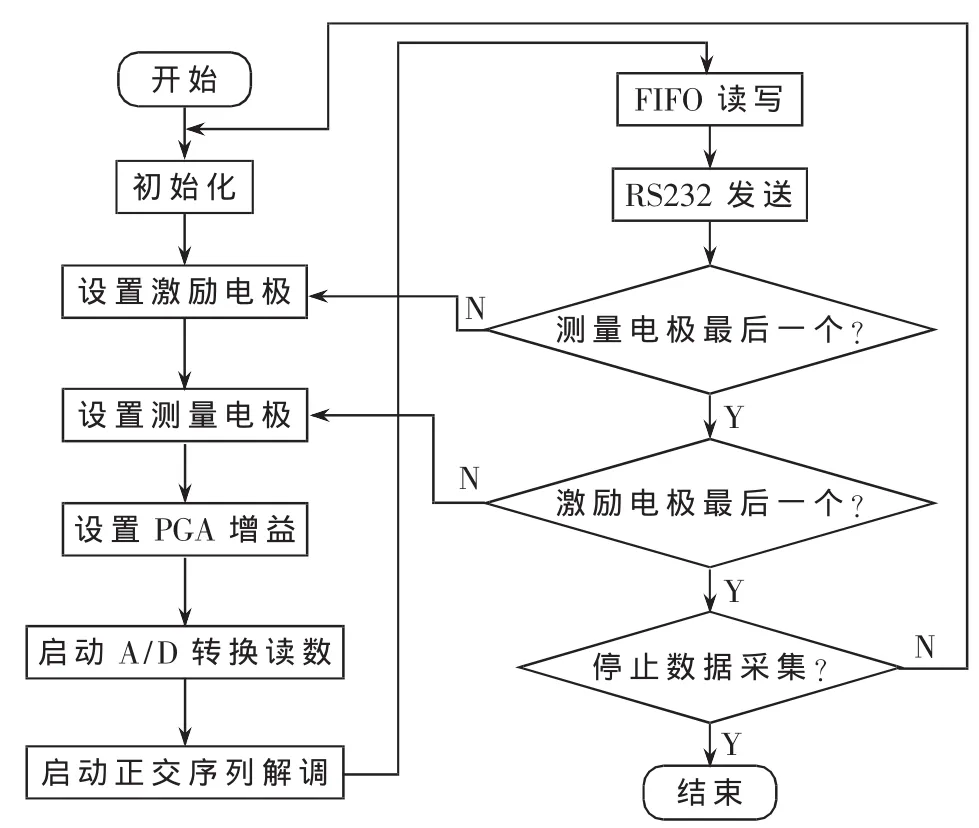

系统软件设计采用ISE 9.2i开发环境和Notepad++文本编辑环境。根据PicoBlaze指令系统在Notepad++中编写控制代码,并保存为.psm格式的文件,再用Xilinx的KCPSM3编译器对文件进行编译,编译后生成一个存储用户程序的 VHDL文件,将其与PicoBlaze微处理器软核加载到ISE的工程中,建立上层文件,对各输入、输出口进行配置。系统的软件控制流程图如图5所示,控制流程为:当上位PC机准备就绪,发送开始工作指令给PicoBlaze微控制器,该控制器接收到指令后先进行系统初始化设置,然后开始选择激励电极对,并按照相邻测量模式进行测量电极的选择。第一个数据测量完成后,切换到下一对测量电极,直到所有测量电极都选通,然后选通下一对激励电极,继续进行测量,直到全部测量完成,这样就完成了1幅图像重构的数据采集。在上述过程中,数据采集并解调后,立即通过串口传送到上位PC机。上位PC机在接收到这些数据后,采用成像算法开始进行图像重建。程序反复循环执行,直到成像计算机发出停止工作指令。

图5 系统的软件控制流程图

3 实验数据

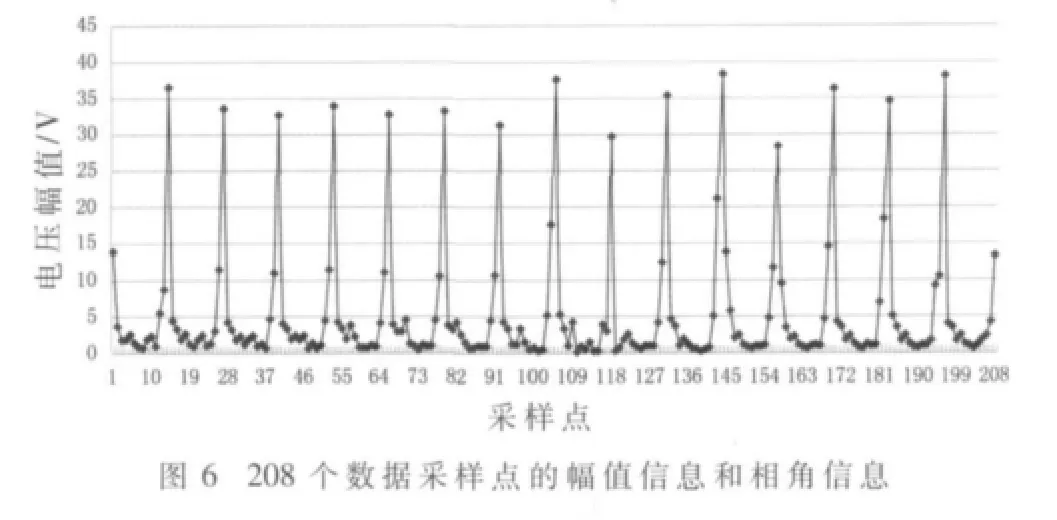

将数据采集系统应用于实验水槽。实验条件为:盐水电导率为710 μs/cm,水温为25.8℃,激励源频率为100 kHz,激励电流峰峰值约为1 mA。在水槽上按照相邻激励相邻测量的模式,依次在电极对 1-2、2-3、3-4、4-5、5-6、6-7、7-8、8-9、9-10、10-11、11-12、12-13、13-14、14-15、15-16、16-1上施加激励源。每进行一次激励,测量除激励电极对及其相邻的两对电极以外的13对电极对的电压差,即总共测量了16×13=208个数据。每采集到一个数据就进行解调,然后将解调后的电压的实部信息和虚部信息通过串口传到上位PC机。再使用MATLAB V7.6.0软件对实部信息数据和虚部信息数据做进一步处理,得到电压的幅值信息和相角信息,用MATLAB中的绘图函数进行绘图,如图6所示。

需要说明的是:在理想情况下,图6中所示的208个数据采样点的幅值信息图应该呈对称的“U”型曲线,但是在图6中可以看到某些“U”型曲线不光滑,某些“U”型曲线中个别点的测量值变化量较大。“U”型曲线反映了数据采集系统的通道一致性,图6表明本系统的通道一致性还不是很好,存在一些问题。影响系统各通道一致性的因素有多种,如电极的尺寸和安装间隔是否完全一致、各通道的通信电缆长度和阻抗等是否一致、多路选通电路是否一致以及电路板中各通道的布线情况是否完全对称等[6]。因此,今后将从以上几个方面对本系统进行改进。

从实验结果可以看出,本文设计的16电极数字化EIT数据采集系统能够准确地完成被测场域的多通道电压信号的采集及处理,并将采集到数据通过串口发送到上位PC机。虽然其在通道一致性上还存在一些问题,有待进一步地研究解决,但这并不影响该系统未来在医学临床上的应用前景。

[1]罗仕强.电阻抗断层成像技术研究进展[J].现代生物医学进展,2009,9(6):1189-1191.

[2]王春艳.应用于肺部检测的电阻抗成像系统[M].天津:天津大学,2007.

[3]陈姝君.电阻抗断层成像技术的研究图像重建算法及实现[M].南京:南京理工大学,2008,

[4]陈晓艳.基于FPGA的生物电阻抗成像系统激励源设计与实现[J].微计算机应用,2011,1(32):20-25.

[5]田海燕.电阻抗断层成像技术理论和实践的研究[M].重庆:重庆大学,2002.

[6]陈晓艳.肺功能电阻抗成像技术研究[M].天津:天津大学,2008.