基于Harris角点检测的嵌入式稳像系统设计

蔡耀仪,林海军

(湖南师范大学 工学院,湖南 长沙410081)

电子稳像系统是应用于车载、飞机、舰船等场合的摄像系统后端,消除图像序列的抖动。传统稳像系统中,图像检测和匹配算法全部由计算机完成,而计算机处理数据是一种单指令周期、串行处理数据方式,难以满足稳像系统实时性的要求。其次,基于通用PC的稳像系统体积一般较大、稳定性较差,难以满足某些对系统体积要求和工作条件比较苛刻的场合的要求。所以采用新型的FPGA器件,研制专用的稳像处理系统成为既有意义又有实际需求的工作。

现有嵌入式稳像系统多数基于投影法(PA)[1]、位平面匹配法(BPM)[2]、块匹配法(BMA)[3]等。其中PA和BPM法只针对摄像机的平移运动进行稳像,而BMA法经过改进能够应用于摄像机小角度的旋转稳像。这些算法很难直接适用于基于并行处理架构的FPGA实现。基于上述原因,针对FPGA的结构特点改进了特征跟踪算法中基于Harris角点检测的特征点匹配算法[4],求取特征点运动参数,利用基于距离准则的特征点匹配验证方法[5]结合最小二乘法得到全局运动估计结果。

1 系统组成

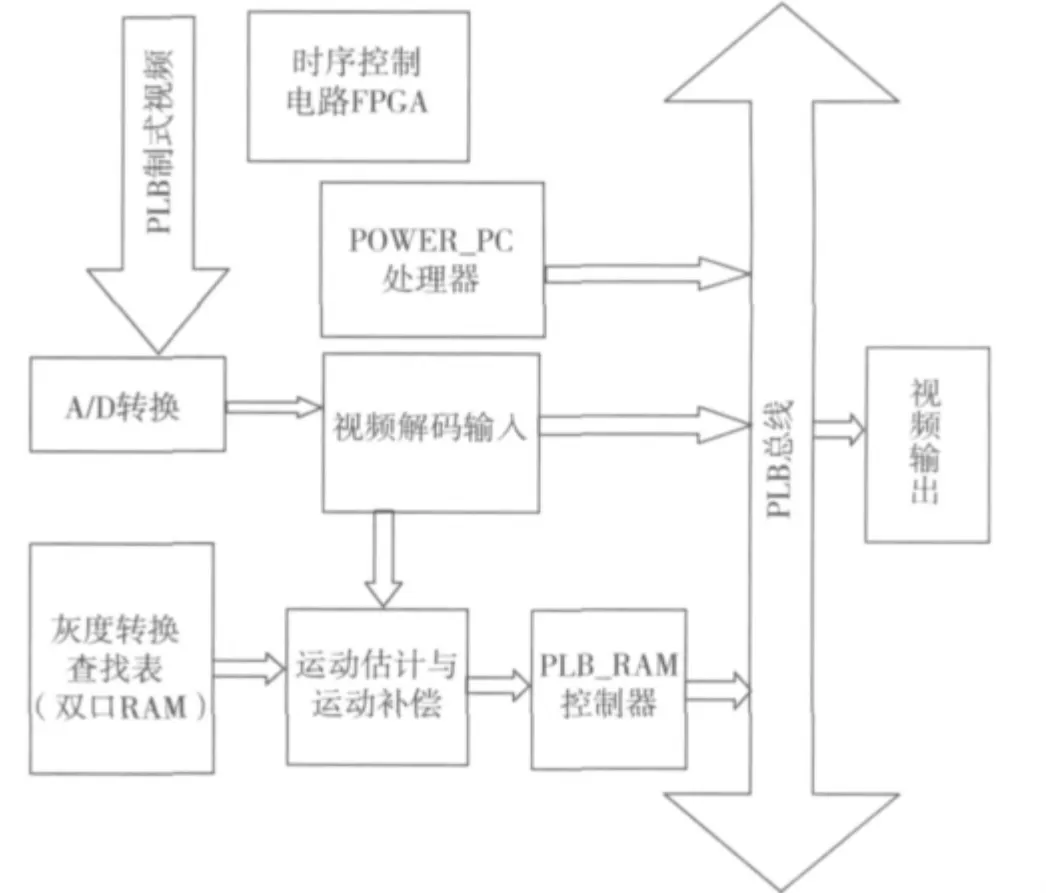

系统以Xilinx公司的Virtex 5 FX100T系列为目标器件,由视频采集、视频解码输入、运动估计模块、运动补偿模块、视频输出模块和时序控制模块组成,如图1所示。系统核心处理器件为Virtex 5 FX100T上的2个PowerPC处理核心,PAL制式的视频信号通过A/D转换子卡转换成符合CCIR.656数字视频流输入到FPGA内部寄存器中,经过运动估计和运动补偿模块将处理后的视频输出到显示器上显示。系统的存储部分包括片上BRAM对少数帧图像进行存储,DDR SDRAM对待补偿的图像和补偿后的图像进行存储,整个过程的控制由时序控制模块完成。

图1 系统框架图

2 软件设计

2.1 摄像机参数模型

视频序列图像产生抖动的原因来自于摄像机的运动,这种运动主要包括平移和旋转。建立合适的数学模型描述摄像机的运动决定了算法能实现的功能和算法的精度。该系统采用Similarity模型描述摄像机的运动,通过此模型能实现图像平移、旋转和缩放的处理。

摄像机坐标系中,由于图像视频序列是三维物体在二维平面的投影,此运动从时刻tk的坐标p(X,Y)运动到时刻tk+1的坐标p'(x',y'),由Similarity模型可得计算方程为

式中:s为缩放因子;θ为旋转因子;d1,d2为p'相对于p的偏移量,通过求解此方程,可得特征点运动参数。

2.2 改进的Harris角点检测算法

普通视频分析系统一般采用DSP实现Harris角点检测,计算量相当大,从而影响稳像系统的实时性,严重时将导致系统运动估计部分不能实时处理。基于Harris角点检测结构相对简单的特点,采用FPGA实现能够较大程度地提高角点检测的速度,从而保证稳像系统的实时性。

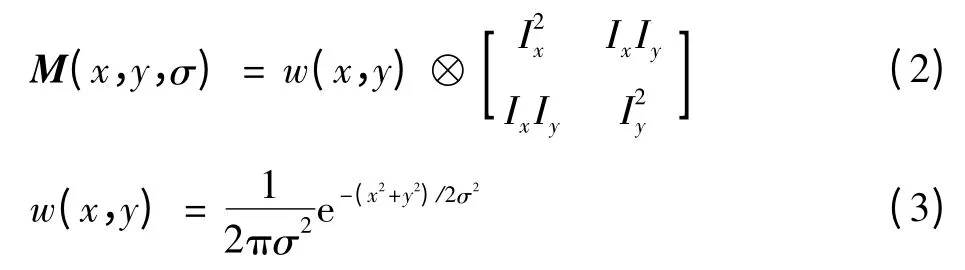

Harris角点是一种基于信号点的特征提取算子,通过建立自相关函数相联系的对称矩阵M,求取M的两个特征值λ1和λ2,则λ1和λ2代表的是自相关函数的一阶曲率,若两个特征值都很大,即代表自相关函数呈尖顶状,即此点为角点。

不同于基于边缘的Moravec角点检测和和采用固定阈值的Susan算子角点检测[6],Harris算子对图像旋转、灰度变化、视角变化和亮度变化具有较好的稳健性。Harris角点检测的过程中利用水平、竖直差分算子对每个像素进行滤波求得水平、竖直方向上的导数,由于Harris算子存在各向异性,所以M保持旋转不变性。

式(2)中:Ix,Iy分别表示图像中像素在水平、竖直方向的导数,而其表达的含义是分别对4个元素进行高斯平滑滤波,由式(3)即高斯函数的形式可知,决定平滑程度即高斯滤波器的宽度由参数σ表征,在一般的Harris角点检测中,通常取σ的值为2,大小为5×5的高斯模板,即可算出其模板系数为:(1/84)×[1,2,3,2,1;2,5,6,5,2;3,6,8,6,3;2,5,6,5,2;1,2,3,2,1],采用此模板进行FPGA实现,得到对1个像素进行1次高斯滤波需要25个乘法器,24个加法器以及完成除以84操作的除法器,造成大量硬件资源的消耗,并提高了系统的复杂性和设计难度。而文献[7]提出采用高斯滤波中采用矩形模板会在自相关检测中引入噪声。基于上述原因,采用圆形模板并将模板系数表示为2的整数次幂的方法对原有5×5高斯模板进行改进,其改进后模板系数为:(1/32)×[0,1,1,1,0;1,2,2,2,1;1,2,4,2,1;1,2,2,2,1;0,1,1,1,0]。比较改进后模板与原高斯模板结构可知,两者同样为低通滤波器,能够有效滤除噪声,且与高斯圆形模板近似,能避免自相关检测时引入的噪声,是有效的高斯滤波模板。同时,采用改进后的模板具有3个优点:1)提高了硬件实现程度。由于FPGA内除法器的实现难度较大,而改进后模板系数与图像像素的乘积运算只是简单的移位操作,即乘法运算为向左移位操作,而除法运算则是向右移位,极大地降低了设计难度。2)进一步满足系统实时性的要求。采用移位运算能够减少计算所占用的时钟周期,改进后模板仅需2个时钟周期便可完成1次高斯滤波过程,而原有模板则会带来变长时钟周期的延时,从而所耗费时间远远超过2个时钟周期。3)减少了硬件资源的开销。对图像像素的移位操作在原有的存储空间中即可完成,不需要调用额外的硬件资源,从而大大节省了硬件资源的消耗。

2.3 基于距离准则的特征点匹配验证

对当前帧图像中的特征点进行正确提取后,需将当前帧图像和参考帧图像中对应的特征点进行匹配,并求取匹配后特征点之间的运动参数。匹配搜索的方法分为全搜索法和局部搜索法2种。由于对系统精度的要求,采用计算量较大但精度较高的全搜索法求得运动参数。对特征点的匹配验证采用绝对误差和(SAD)验证准则,得到1组特征点对集合。

由于视野中运动物体在当前帧的出现和消失会造成局部特征点,并且在匹配过程中容易产生误匹配点,进而严重影响运动估计的精度,从而需要采用一定方法剔除误匹配点和局部特征点,该系统采用距离不变准则来校正特征点对。具体算法为:

设A(ma,mb)和B(mb,nb)为任意2个参考帧图像上的特征点,而当前帧图像上与其对应的特征点为A'(m'a,m'b)和B'(n'a,n'b)。假设(A,A')与(B,B')之间是正确的匹配对,则满足

基于以上方程描述距离准则,设计匹配验证步骤为:

1)对已有的N个特征点对计算其横纵坐标之间的距离,采用桶形聚类方法将其分成k(k≤N)类。

2)统计和比较k类中特征点的个数ti(i=1,2,…,k)。

3)求取特征点距离对最多的类,即距离对数量满足ti=max{ti|i=1,2,…,k),即所有集合为全局特征点对。

2.4 最小二乘估计法计算全局运动矢量

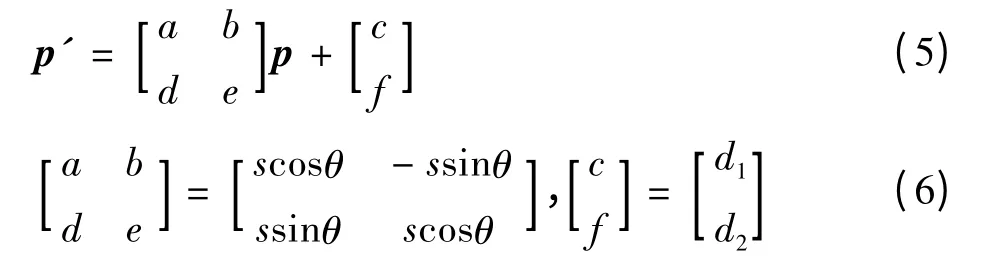

通过局部运动估计得到的运动矢量采用最小二乘法的思想求出全局特征点的信息,将Similarity模型转换6参数仿射模型,得

公式(6)给出了变换后两种参数模型的对应关系。将当前帧图像特征点与参考帧图像对应特征点的坐标分别记作(x'i,y'i),(xi,yi),i=1,2,···,n。则对每一个特征点匹配对,有

公式(7)中:i为特征点对的编号,Δxi,Δyi为当前帧特征点对应参考帧的运动矢量。在6参数模型的基础上,定义能量函数ρx,ρy如

根据最小二乘法,当ρx,ρy取得最小值时,即

可以得到帧间旋转角度θ和缩放因子s为

3 硬件设计

系统采用模块化设计,并借助ISE和EDK开发工具设计实时稳像系统。

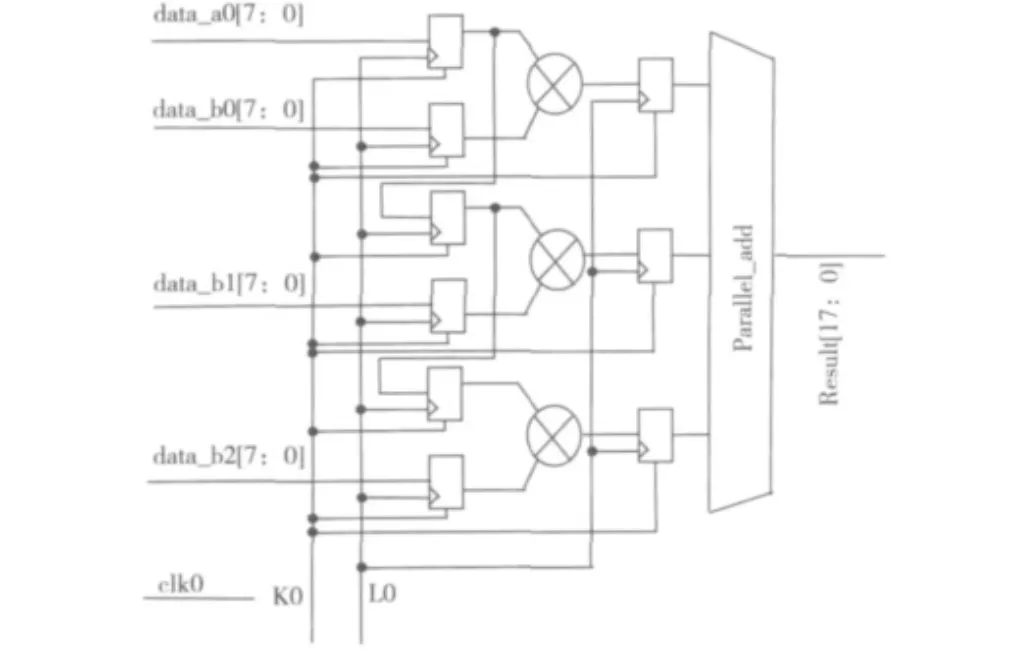

3.1 高斯滤波模块设计

高斯滤波计算过程中,采用5行缓存,即需要将视频数据流形成数据窗口,应用改进的高斯滤波模板完成计算。数据缓存器设计应用FIFO存储器结构,在像素时钟以及行同步信号的控制下完成数据缓存。由于模板中乘除法计算采用移位的形式,避免了复杂计算带来的时间与资源消耗。窗口形成模块设计如图2所示。

图2 基于FIFO的窗口形成模块

对缓存的设计采用ISE工具集中的Core Generator高速缓存生成器生成所需缓存。其中模块中FIFO存储器是关键的设计。FIFO通常存在读使能端口、写使能端口、FIFO状态端口、数据输入输出端口等信号端口,其状态一般分为3种:满、未满或空。其中FIFO设计的深度等于图像中列数,而其设计难点在于判断数据的空/满状态。传统的FIFO设计中,亚稳态难以避免,而该设计中采用冗余的触发器,即避免FIFO在真正发生空/满状态时设置空/满标志,而是提前设置标志,使得FIFO能够提前清空与写入双口RAM中。这样设计势必会浪费一定的硬件资源,但保证了FIFO模块的精度。

FIFO模块系统仿真时序如图3所示。由时序图可知,FIFO很好地完成数据缓存与输出,减小了亚稳态出现的概率,能达到系统设计的要求。窗口模块后的每个数据输出端口均接入与改进后的高斯模板系数相对应的乘法器,即对数据完成相应的左移位操作。对5行数据完成相应系数的乘法操作后汇总进行右移5位的操作,即完成对改进后规范化系数的除法运算。高斯滤波模块每个时钟周期即可得到相应的滤波值,从而完成高斯滤波操作。

图3 FIFO功能框图及仿真时序图(截图)

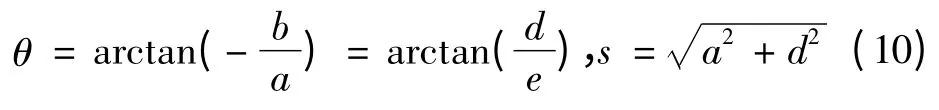

3.2 求导计算与非局部最大值抑制模块

对X与Y方向的求导计算同样采用模板来完成,该模板与低通滤波模板类似,只改变模板的系数,只需1个时钟周期的操作即可计算出X与Y方向的梯度算子,由于篇幅关系,在这里定制实现3个数据梯度计算的ladder_3模块,如图4所示。该系统所需梯度计算模块即在此模块上的扩展,即将数据分别于相对应的5×5计算模板系数相乘,其可利用Sobel模板求取梯度[8]。

图4 梯度算子计算模块

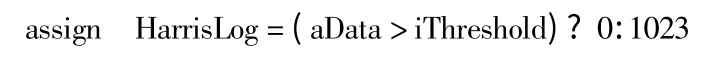

对计算后结果还需进行兴趣值领域的非极大值抑制,即只保留最佳结果。非极大值抑制在计算兴趣值R时针对FPGA将小于零的R值置零。兴趣值的计算需调用乘法器完成,其非极大值抑制在3×3领域内完成。将得到的兴趣值图像与阈值进行比较,若其大于设定阈值即为最终求得的角点。其Verilog代码如

其中:iThreshold即为设定的门限值,将aData标记为黑的点即为所求得的角点,从而能够得到角点的坐标。

3.3 运动估计与运动补偿模块

提取出角点信息后,需要进行局部运动矢量的估计以及全局运动矢量的计算。单纯采用FPGA结构很难完成如此复杂的计算。应用Virtex 5 Fx100T中嵌入的Power PC处理器构建软硬协同处理模式,通过PLB总线访问高速缓存中的角点信息,最终计算出帧间全局运动矢量。

运动补偿是通过对存储在DDR SDRAM中的待补偿帧图像数据,利用Xilinx公司的MPMC(Multi-Port Memory Controller)IP核来完成内存的读写管理在其专用开发工具EDK中完成。调用此IP核能够将整个DDR SDRAM分成8个互相独立的端口,每个端口的操作类似于BRAM,即可以通过任意一个端口访问内存。在应用MPMC核进行运动补偿时,由于其写入机制为先将数据写入缓存后再完成写入内存操作,而对内存数据的读取是直接进行。为了避免此冲突的发生,系统设定判定信号首先判定缓存是否为空,仅当判定信号返回为空时才执行读取操作,从而避免了读写冲突造成的数据丢失。

4 实验与分析

系统采用PAL制式彩色工业线阵摄像头,拍摄某室内场景,数据流经FPGA稳像系统实时处理后显示在VGA显示器上。为了验证系统的性能,将系统放置在用于产生震动的云台上,以2 Hz的频率进行一定幅度震动。图5为结果的第1帧、第7帧、第14帧、第21帧。为了便于对比系统效果,显示器左半边为未进行稳像处理视频流,右半平面为进行稳像处理后的同源视频流。

图5 实验结果

对比左右显示结果可以明显看出:左半平面内容发生明显的改变,而右半平面内容基本保持不变。其中结果第7帧右半平面可以明显看到系统进行运动补偿后产生的黑色空白区域。从而证明,系统具有良好的实时稳像效果。

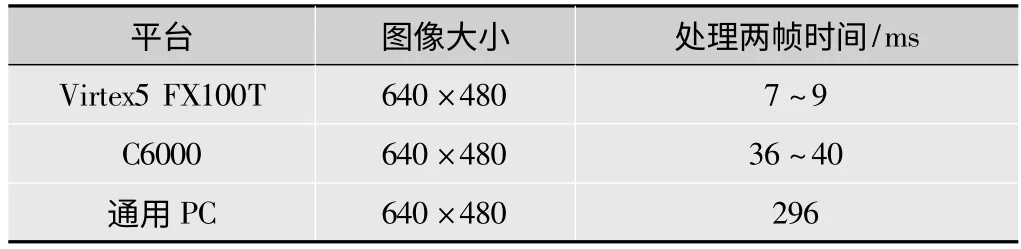

将系统与同样移植程序的基于C6000系列的DSP稳像平台以及基于INTEL Pentium E5300 2.6 GHz、内存为4 Gbyte的通用PC稳像平台处理时间对比如表1所示。

表1 不同平台处理时间

由此看出,采用基于FPGA的处理平台每秒处理帧数能够达到100帧以上,处理速度远远高于DSP平台以及通用PC平台,能够实现高速视频的稳像。系统在某厂矿企业已经运行达2 000 h,事实证明其能稳定工作。

5 结束语

系统针对FPGA的特点,改进了基于Harris的角点检测算法,并应用距离准则对角点对进行验证。在得到角点的基础上应用硬核处理器对抖动进行运动估计和运动补偿,实现了能够高速处理抖动视频的嵌入式稳像系统。实验表明,稳像系统处理速度高,效果较好,能够达到高速实现稳像的要求,具有较高实用价值。但对运动补偿部分即补偿后画面中空白区域的处理还缺乏研究。

[1]ZHANG Yongxiang,CHEN Fangmin.Implementation of gray projection image stabilization algorithm based on TMS320DM642[C]//Proc.IEEE 5th International Joint Conference on INC,IMS and IDC.[S.l.]:IEEE Press,2009:1724-1726.

[2]SUNG J K.Fast digital image stabilizer based on gray-coded bit-plane matching[J].IEEE Trans.Consumer Electronics,1999,45(3):598-603.

[3]杨光宇,朱丹,佟新鑫,等.基于灰度投影法的电子稳像平台设计与实现[J].电视技术,2011,35(19):115-118.

[4]倪乐真,李玉山,刘洋,等.一种基于角点配对的稳像算法[J].电视技术,2009,33(S2):71-74.

[5]朱娟娟,郭宝龙.一种鲁棒的电子稳像系统[J].西安电子科技大学学报:自然科学版,2007,34(3):418-422,452.

[6]贺菁,李庆华,王新赛.基于方向性SUSAN算子的图像角点特征提取[J].小型微型计算机系统,2008,29(3):508-510.

[7]PIKAZ A,DISTEIN I.Using simple decomposition for smoothing and feature point detection of noisy digital curves[J].IEEE Trans.Pattern Analysis and Machine Intelligence,1994,16(8):808-813.

[8]唐永鹤,胡谋法,卢焕章.抗噪型Sobel边缘检测算法及其硬件加速设计[J].计算机工程,2011,37(24):204-206.