基于FPGA的多路高速信号可重构系统平台设计

朱 昊 刘化君 宋宇飞

南京工程学院 江苏南京 211167

基于FPGA的多路高速信号可重构系统平台设计

朱 昊 刘化君 宋宇飞

南京工程学院 江苏南京 211167

提出了基于FPGA的多路信号高速采集、存储、处理系统的设计方案。给出了现代电子系统的需求分析。介绍了系统的硬件结构,讨论了FPGA内部的资源分配与设计,分析了系统的可重构特点。实际应用表明,本系统具有功能灵活、处理速度高、抗干扰能力强的特点,可作为高速信号通用处理平台使用。

FPGA;多信号;高速处理;系统重构

随着电子技术的发展,电子系统处理信号的能力越来越强大。用户对电子产品的要求也在不断提高。传统的低速系统已经逐渐不能满足用户的需求。另一方面,电子器件的成本越来越低,以往各种昂贵的功能强大的高速处理芯片已经逐渐平价化。因此,现在基于高速处理芯片的电子系统在生活中的应用越来越广泛。对于这一变化趋势,作为大学电子类教学来说,也应该逐渐调整教学重心,逐步加强各种新型高速处理芯片以及高速信号处理系统设计的介绍,以此来加强与实际需求的衔接。

1 现代电子系统的功能需求

1.1 信号处理数量多

现代电子系统往往都具有多种功能,这就要求系统能并行处理多路模拟、数字信号。这在工业控制领域尤其明显,某些领域,如针织机械要求同时处理上百路信号。以往处理信号较少时,控制系统中通常采用微处理器,如各种单片机或数字信号处理器(Digital Signal Processor,DSP)等。但对于现在的复杂控制系统,限于处理能力、速度以及引脚数量,仅仅靠用普通的微处理器往往难以完成任务。对此,通常只能采取多个微处理器联机的并行处理模式,或者添加其他芯片扩展系统资源来完成系统的控制任务。但这样做不仅增加了大量的外部电路和系统成本,而且大大增加了系统的复杂性,同时系统的可靠性也会受到影响,这显然是设计者所不希望的。

1.2 信号处理速度高

现代电子器件中,各种处理芯片的主频越来越高。在现代生活的各个领域中,电子系统的处理速度越来越快。传统的单片机主频一般在6M~12MHz,对于现代高速电子产品而言已经越来越难以胜任。可编程逻辑器件(Programmable Logic Device,PLD)、ARM(Advanced RISC Machines)以及DSP等芯片可通过内部锁相环(Phase Locked Loop,PLL)生成高达500~700MHz的时钟信号,因此在各种民用、工业、军事领域内广受青睐。

1.3 电路体积和功耗小

现代电子产品中,手持设备以及微小型设备越来越多。低功耗在现代电子系统中逐渐成为一个重要的指标。另一方面,电路板的体积也不断缩小。因此,传统数字电路设计中多芯片结构已经不能满足这种需求。而PLD芯片凭借其可编程实现复杂数字逻辑的功能,在现代电子系统设计中逐渐被作为数字逻辑电路的取代品。

2 系统硬件架构设计

2.1 系统总体架构

该系统选用现场可编程门阵列(Field Programmable Gate Array,FPGA)为核心处理芯片,FPGA是目前PLD芯片中最常用的一种。它作为专用集成电路(Application Specifi c Integrate Circuit,ASIC)领域中的一种半定制电路而出现,既解决了定制电路功能单一的不足,又克服了原有简单可编程器件资源有限的缺点。其内部丰富的数字电路资源以及外部IO引脚更加适用于复杂逻辑的数字信号并行处理。该系统中,FPGA完成多路信号的并行采集、存储以及输出功能。选用FPGA可以整合传统数字电路设计中的众多数字芯片,使得电路体积充分缩减,同时有效地减少电路系统的功耗。

考虑到该系统完成信号处理的复杂程度较高,从运算能力角度来说,仅采用FPGA芯片难以完成复杂信号运算。因此该系统选用一片高速DSP专门用于复杂信号处理和数据运算。

该系统选用一片Flash芯片作为系统的数据存储器。由于该系统中DSP内部不含EPROM,所以为了能够独立运行,当系统脱离仿真环境以后,必须把编译后的可执行代码和上电自举所需的自举表存储在外部存储器之中。另一方面,FPGA的核心结构为SRAM,同样需要将配置数据存放在片外存储器中。因此,系统中的Flash芯片除了用于系统工作时的数据存储之外,还同时存放DSP和Flash的下载程序和配置数据。

系统输入接口分为模拟和数字两个部分。模拟部分选择了2片高速AD和1片低速AD。高速AD为单通道输入;低速AD可支持8路模拟信号输入。由于目前低功耗电子系统的广泛应用,3.3V的LVTTL电平逻辑系统使用越来越广泛。因此系统的数字输入部分通过数据总线转换芯片74LVC16245来实现TTL电平和LVTTL电平信号通用系统。

系统输出部分选用8位数模转换芯片以及低通滤波电路作为模拟数据输出接口。

系统中FPGA,DSP和Flash三种芯片采用3.3V电平逻辑,而AD芯片和DA芯片为5V逻辑电平。因此AD芯片和DA芯片与FPGA连接时,也需要加接数据总线转换芯片74LVC1624作为电平转换。系统结构框图如图1所示。

图1 系统结构框图

2.2 核心芯片选择

该系统中的FPGA芯片选用美国Altera公司Cyclone II系列芯片中的EP2C8Q208芯片。CycloneII系列芯片是Altera公司推出的新一代低成本FPGA,用于中等复杂度且追求性价比的系统。基于Altera公司的开发环境QuartusII可以对芯片内部硬件资源进行编程并对芯片管脚的功能进行定义。

该系统中的DSP芯片选用美国TI公司5000系列中的TMS3205410芯片。5000系列芯片是TI公司一大类新型而重要的阶段性16位定点数字信号处理器,在各种应用领域有着广泛的应用。

该系统中的Flash芯片选用Spansion公司的S29GL064M芯片,其存储容量为64Mbit。FPGA芯片EP2C8Q208的配置数据大小约为1.9Mbit,可见该芯片足够用于存放FPGA配置数据和DSP程序。

该系统中的模数转换芯片选用了2种,分别为TLC5540和ADC0809。TLC5540是美国TI公司推出的高速8位AD转换器。它的最高转换速率可达40MSPS。TLC5540可广泛应用于数字电视、医学图像、视频会议、CCD扫描仪、高速数据变换及QAM调制器等应用方面。AD0809是美国国家半导体公司生产的8位AD转换芯片。其最高采样频率为10KSPS。但其片内带有锁存功能的8路模拟多路开关,因此可以对8路模拟电压信号分时进行转换。

该系统中的DA芯片选用8位DAC0832芯片。

2.3 可重构系统实现

FPGA的核心结构由SRAM构成。由于SRAM的掉电易失特性,所以需要把决定FPGA内部的配置数据存放在片外存储器中,每次加电时,配置数据都必须重新下载。因此对于FPGA来说,并不采用常见的系统编程(In System Programming,ISP)方式下载程序,取而代之的是通过在线配置方式(In Circuit Reconfigurability,ICR)配置数据。基于FPGA的可重构系统是指在FPGA器件已经配置好的情况下,在线进行重新配置,以改变电路逻辑结构和功能。在FPGA工作时,利用FPGA的ICR特性,通过外部控制信号选择不同的配置数据,经过在线更新后,可以实时改变FPGA内部的电路逻辑结构。

FPGA配置方法有PC机配置、专用芯片配置、微处理器配置等多种方式。PC机配置是指FPGA的配置数据存放在PC机中,由PC机通过下载电缆对FPGA进行系统重构。PC配置法虽然在调试时非常方便,但对于独立产品来说并不现实。专用配置芯片自带时序生成系统,使用方便,但只能存放一个配置文件,即FPGA只能实现单一功能,如果需要改变FPGA的结构,只能重新设计、综合适配后把数据下载到配置芯片中,过程繁琐。而利用微处理器对FPGA进行配置则可把多个配置文件存放在片内或片外存储器中,通过微处理器的程序实时选择不同的配置文件对FPGA进行重构,通过这种方式使得1片FPGA具有多种功能,且能够进行实时功能切换,具有非常实用的价值。

该系统利用DSP和Flash芯片共同构成FPGA的重构电路,Flash内同时存放了FPGA和DSP的配置程序。两者配置过程为:

(1)在CCS中编写编译DSP应用程序、自举程序并生成相应二进制代码。

(2)在QuartusII中设计系统、综合、适配并生成相应二进制代码。

(3)在CCS中编写Flash烧写程序,下载至DSP。

(4)系统上电,DSP运行烧写程序,将DSP应用程序、自举程序、FPGA配置数据全部烧写进Flash。

(5)断电脱离PC机。

(6)再次上电,自动运行自举程序,先后从Flash中把DSP应用程序调入DSP的程序存储空间,用户可通过DSP程序随时从Flash中调出FPGA配置数据并下载到FPGA中,实现FPGA的系统重构。

3 FPGA内部逻辑设计

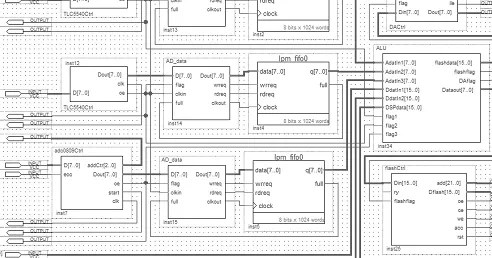

FPGA内部由TLC5540控制模块TLC5540Ctrl,ADC0809控制模块adc0809Ctrl,FIFO存储器模块lpm_fifo0,FIFO时序控制模块AD_data,逻辑运算模块ALU,Flash控制模块FlashCtrl和DA控制模块DACtrl组成。

其中TLC5540Ctrl和adc0809Ctrl模块用于控制2种AD芯片的工作时序。2个模块均采用状态机的设计思路通过VHDL语言编程实现。FIFO模块用于采样数据和处理模块之间的数据缓冲。AD_data模块用于控制FIFO模块的工作时序,将AD采样结果送入FIFO存储器。ALU模块完成核心逻辑处理功能,结合上文所述系统重构原理,可实现不同逻辑功能。DACtrl模块完成DA0832的时序控制,同样采用状态机的思路编程实现。FlashCtrl模块将ALU的运算结果根据需要送入Flash芯片存储。FPGA内部结构如图2所示。

图2 FPGA内部结构图

4 结束语

针对目前信号处理系统功能越来越强的趋势,提出了一种基于FPGA技术的多路信号高速采集与处理系统。相比传统的设计方法,该系统利用FPGA的高速特性及其在电路逻辑设计方面的特点,配合DSP的高速信号处理能力,一方面有效提高了系统处理速度,另一方面简化了电路结构。特别是利用FPGA的在线可重构特性设计了相应电路,使得系统功能以及灵活性得到显著的增强。该系统既可作为高校通用信号处理教学平台,也可作为科研的通用开发系统。

[1] 王宏义,董文娟,黄宗福,等.DSP和FPGA共用Flash进行配置的方法[J].微计算机信息,2008,26:101~102,110

Design of multiple high speed signal reconfi gurable system platform based on FPGA

Zhu Hao, Liu Huajun, Song Yufei

Nanjing institute of technology, Nanjing, 211167, China

This paper introduces the design scheme of multiple high speed signal acquit, store and process system. The demand analysis of modern electronic system is put forward. The structure of hardware is introduced. The resource assign is discussed. The reconfi gurable feature of system is analyzed. The application indicates that this system is fl exible high speed and interference-free. It can be used as utility platform.

FPGA; multiple signals; high speed process; system reconfi gurable

2010-12-01 稿件编号:1012007

朱昊,硕士,讲师。

南京工程学院“先进数控技术江苏省高校重点建设实验室”。

南京工程学院科研基金项目(编号:KXJ08114),江苏高校科研成果产业化推进项目(编号:JHZD08-12)。