边界扫描技术在工程测试中的应用

徐 静,刘 军

(中电集团第三十八研究所,合肥 230088)

随着微电子制造技术向深亚微米方向的发展,电路设计的高度复杂性及多层印制板、表面贴装(SMT)、圆片规模集成(WSI)和多芯片模块(MCM)技术在电路系统中的运用,FPGA的集成度也越来越高,管脚数目和管脚密度不断提高,使得基于物理探针的传统测试技术难以为继,电路和系统的可测试性急剧下降,常规测试方法正面临着日趋严峻的困难。基于这一难题,近几年飞速发展的边界扫描技术很好的解决了这个问题。本文主要介绍了边界扫描的概念、原理、优势及利用该技术设计的自动测试设备,通过实际测试结果阐述边界扫描技术的先进性、高效性。

1 边界扫描基本简介

1987年,联合测试行动小组(JTAG)提出了一种新的电路板测试方法——边界扫描技术,并于1990年被IEEE接纳,形成了IEEE1149.1标准[1]。该标准要求在集成电路中加入边界扫描电路,在模式选择的控制下,构成一条环绕集成电路边界的移位寄存器链,由此对集成电路的所有引脚进行扫描。边界扫描测试结构提供了一种方法,可以高效的测试PCB上面的器件。

2 边界扫描结构和工作原理

2.1 结构

图1给出了芯片内部边界扫描逻辑结构,它包括测试存取端口(TAP)、TAP控制器 、指令寄存器及一系列数据寄存器、数据寄存器包括旁路寄存器、器件标示寄存器和边界扫描寄存器等[2-3],各信号定义如下

边界扫描单元信号(boundary-scan cell signals)

在并行输入端PI俘获数据

在并行输出端PO更新数据

串行扫描数据从SO到与它相邻的SI

行为透明:PI到达PO

TAP控制器信号(TAP controller signals)

TDI测试信号输入

TDO测试信号输出

TMS测试模式选择

TCK测试时钟

TRST可选择的测试复位信号

TAP(test access port)是一个通用的端口,通过它可以访问芯片提供的所有数据寄存器和指令寄存器。而对整个TAP的控制是通过TAP Controller来完成的。边界扫描寄存器是数据寄存器中很重要的一种,它用来实现对芯片的输入输出的观察和控制。指令寄存器用来实现对数据寄存器的控制。

图1 边界扫描逻辑结构

2.2 原理

边界扫描测试技术是通过在芯片的每个I/O脚附加一个边界扫描(boundary scan cell,BSC)以及一些附加的测试控制逻辑来实现的。BSC主要是由寄存器组成,每个I/O管脚都有一个BSC,每个BSC有2个数据通道:① 测试数据通道,测试数据输入TDI(test data input)和测试数据输出TDO(test data output);②正常数据通道,正常数据输入NDI(normal data input)和正常数据输出NDO(normal data output)。

图2展示了BSC的连接。

图2 边界扫描单元BSC的连接

BSC除了与封装引脚和芯片的工作逻辑相连外,也串行互联,形成一个移位寄存器链。在芯片的正常工作情况下,它是透明的和停止运行的,因此,输入和输出数据可以自由通过每个BSC,正常工作数据从NDI进,从NDO出;在测试模式下,元器件的边界引脚以及内核逻辑可以通过边界扫描单元进行控制和观察,对于输入的IC(集成电路,integrated circuit)管脚,可以选择从NDI或从TDI输入数据;对于输出的IC管脚,可以选择从BSC输出数据至NDO,也可以选择从BSC输出数据至TDO。

图3所示是边界扫描测试应用的示意图。测试2个JTAG设备的连接,首先将JTAG设备1某个输出测试脚的BSC置为高或低电平,输出至NDO,然后,让JTAG设备2的输入测试脚来捕获从设备1管脚输入的NDI值,再通过测试数据通道将捕获到的数据输出至TDO,对比测试结果,即可快速准确的判断这两脚是否连接可靠。

图3 边界扫描测试应用示意图

通过边界扫描链这种结构可以实现内部结构测试、互连测试、功能测试、存储器测试等。

3 利用边界扫描技术测试优势

1)边界扫描技术的使用,可以消除实际测试点。边界扫描是利用“虚探头”代替传统使用的物理探头,设计时无需考虑实际测试点问题,这样不仅可以减少设计时间,而且当测试点的消除达到一定数量时,可以减少PCB板的层数,从而降低了制造价格。

2)方便芯片的故障定位,可以准确地判断两个芯片管脚的连接是否可靠,提高测试、检验的效率。

4 自动测试设备设计及测试结果分析

4.1 自动测试设备的组成

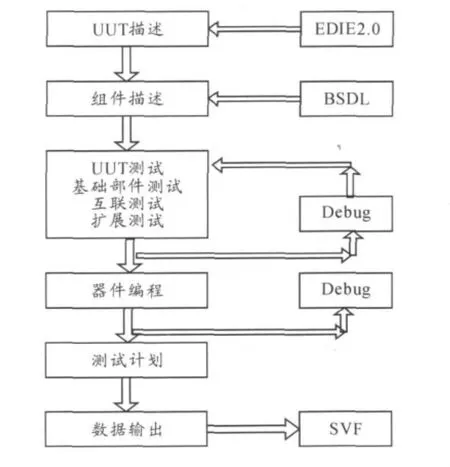

软件部分采用法国TomentoSystems公司的DiaTem做为开发工具,自动测试软件设计流程如图4。

图4 自动测试设计流程

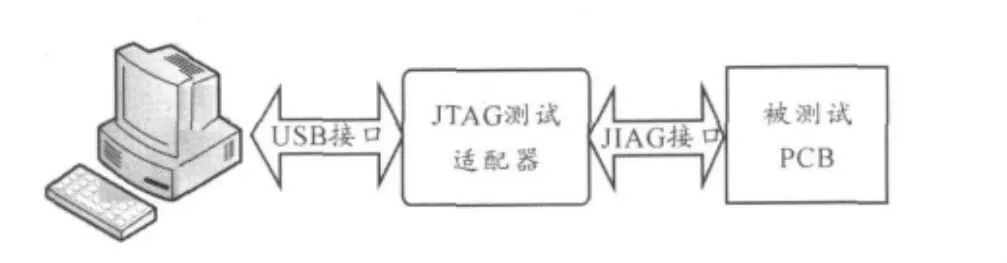

硬件包括计算机、JTAG适配器、测试背板和电源,如图5所示。

图5 自动测试台构造

4.2 测试结果分析

测试完成后,会生成一份测试报告,根据报告分析被测PCB的好坏。测试过程中经常出现的故障类型与解决方案举例:

1)故障类型

a)测试链路不通;

b)测试链路通,但部分信号工作不正常。

2)解决方法

对于链路不通,排除硬件连接情况后。链不通有两种可能,器件自身问题或者创建的测试工程有误,这就要求在设计时,仔细分析相关的电路及工作原理,遵循设计原则,确保测试工程正常运行;对于部分信号工作不正常情况,一般表现为短路或开路情况,它们可能由于生产PCB所致,也可能由于电路板焊接所致,报告中会给出故障出错支路或出错类型,使问题查找范围缩小,方便排查。测试报告列举如下:

5 结束语

边界扫描测试软件可以自动分析产生测试激励信号,自动分析测试结果,并且给出详细的测试报告,有测试速度快,效率高且不需要测试者过多干预等优点。利用边界扫描技术设计的自动测试设备可以应用在板极测试与系统级测试,包括开发调试、生产测试、维修测试等过程。

[1]IEEE1149.1,IEEE Standard Test Access Port and Boundary-Scan Architecture[S].

[2]宋克柱.边界扫描测试的原理及应用设计[J].电子技术,2001(10):31-35.

[3]邱峰,梁松海.IEEE1149.1可测试性设计技术的研究与发展[J].测控技术,1999,18(1):28-30.

- 兵器装备工程学报的其它文章

- 构建寓军于民的供油保障“大系统”