基于FPGA的m序列发生器的设计★

高磊,陈志强,吴黎慧,蒲南江

(中北大学信息探测与处理技术研究所,山西 太原 030051)

0 引言

m 序列是伪随机序列的一种, 结构简单, 实现方便。在现代工程实践中, m 序列在通讯、导航、雷达、通信系统性能的测量等领域中有着广泛的应用。例如, 在连续波雷达中可用作测距信号, 在遥控系统中可用作遥控信号, 在多址通信中可用作地址信号, 在数字通信中可用作群同步信号, 还可用作噪声源及在保密通信中起加密作用等。伪噪声发生器在测距、通信等领域的应用日益受到人们重视。有关产生m 序列发生器的方法很多。其中, 用通用数字器件构成的特点是速度可以很快, 但硬件电路不便修改特性, 只能产生单一n 级m 序列; 用软件方式构成的特点是采用灵活的数据查询方式可以获得任意级数n 的本原多项式系数,从而实现m 序列的产生, 但速度受到单片机工作速度的限制。而FPGA 具有硬件电路实现的优点, 又具有设计上的灵活性, 并且由于FPGA 便于实现大规模的数字系统, 其中内嵌了一定数量的E2PROM。因此,本文利用FPGA设计生成了3路m序列发生器。

1 基本理论

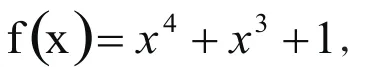

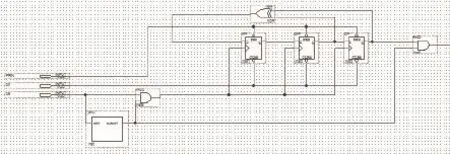

m序列是最长线性反馈移位寄存器序列的简称,它是由带线性反馈的移位寄存器产生的周期最长的一种序列。m序列可以利用n级移位寄存器产生.可能产生的最长周期为(2n-1)。m序列发生器的结构主要分为两类,一类称为简单型码序列发生器,另一类称为模块型码序列发生器。原理图如图1所示。

图1 m序列原理图

2 设计思想

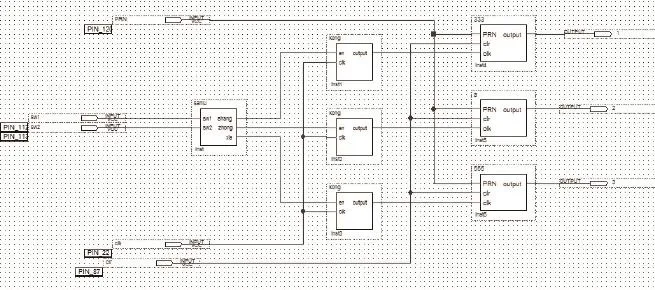

2.1 总体方案设计

本文通过控制模块控制各个m序列发生器,从而生成不同位数的m序列。

2.2 一路m序列发生器的设计

图2 仿真实现

图3 伪码仿真图

图4 伪码设计图

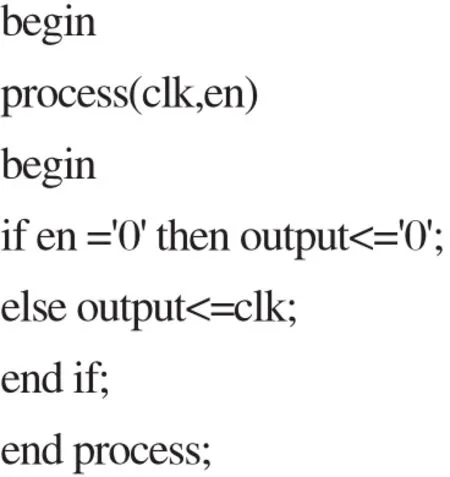

2.3 控制模块的设计

控制模块是选择3路信号的控制端口。如图5所示。部分VHDL源代码如下:

图5 控制图

3 实验结果

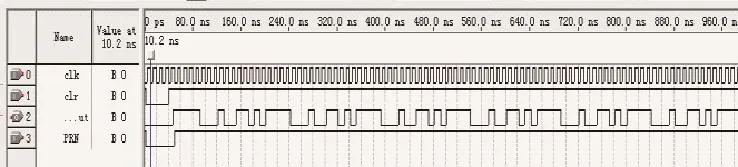

根据上述实验步骤,可得出m序列发生器的仿真图如图6所示。

图6 3路信号仿真图

最后,通过示波器观察实验结果。如图7所示。

图7 示波器显示的实验结果

4 结束语

本文论述的基于FPGA的m序列发生器简单易行,具有很强的实用性,通过VHDL语言编写程序完成m序列信号的生成,以及控制模块的生成,为相关领域提供了较好的模型和方法,具有很强的实际使用价值。但本系统在提高码速率方面亟待进一步提高。

[1]樊昌信.通信原理[M].北京:人民邮电出版社,2007.

[2]张涛.双通道伪随机信号发生器的研究[J].电子测量与仪器学报,2008,11(2):11-151.

[3]束礼宝,宋克柱,王砚方.伪随机数发生器的FPGA实现与研究[J].电路与系统学报,2008,8(3):121-124.

[4]邬杨波,王曙光,胡建平.有限状态机的VHDL设计及优化[J].信息技术,2008,28(1):75-78.

[5]张力军.数字通信简介[J].电子工业大学学报,2003:552-552.

[6]童成意.扩频通信技术的应用研究[J].湘潭师范学院学报:自然科学版,2008(8):21-28.

[7]William,Sandoval.The ZigBee Revolution[DB/OL].[2005-09-23].

[8]吴先用,邹学玉.一种m序列伪码发生器的产生方法[J ].测控技术,2003,22(9):56-591.