组网跳频电台同步过程的设计及实现

何苏勤, 张海庆

(北京化工大学信息科学与技术学院,北京100029)

0 引 言

跳频通信具有频谱资源共享、抗干扰、抗截获的特点,当前在很多领域已得到了广泛的应用。跳频通信组网时,多采用时分多址接入(time division multiple access,TDMA)组网,在基于TDMA的跳频通信系统中,各个电台必须在分配的时隙中发送或接收信号,因而整个系统必须有严格的同步过程,以便保证双方可靠的组网和通信。本文根据跳频电台的TDMA组网协议,在参考了文献[1-2]的基础上,提出了适用本系统的时隙分配方式,结合跳频同步方法,设计了一套组网跳频电台同步方案,实现了组网和同步的结合,能有效地提高跳频电台组网的稳定性和数据传输效率。

FPGA(现场可编程逻辑门阵列)以其丰富的逻辑资源和可重新配置的优势,成为人们前期研究与开发的重要手段[3]。在FPGA上进行仿真实验,具有重要的应用价值。通过在Altera公司的FPGA开发软件Quartus2软件上仿真,并在FPGA硬件开发板上调试,成功实现了组网跳频电台的同步过程。

1 同步方法的选择

本文采用同步头法和精准时钟法相结合的同步方案实现组网跳频同步。同步头法是指由发送方发送一个同步用的协议帧,其中含有同步所需的全部信息,收方依据接收到的同步信息实现收发两端同步[4]。精准时钟法是指在网中或两个电台之间使用精准的基准参考时钟。由于通信各方使用了相同结构的跳频图案,当前通信频率仅取决于时间信息,当通信距离一定时,就可以依据当前时钟信息来确定当前通信频率。该方法要求时钟必须足够精准,因此就有必要对通信各方的参考时钟不断进行校正,来保持时钟的准确性[5]。利用同步头法同步搜索快,易于实现,同步可靠的特点,以及精准时钟法计时精确的特点,使跳频系统的同步实现方便、精度高、速度快。

2 组网协议

时分多址接入(TDMA)技术把无线频谱按时隙划分,并且在每一个时隙仅允许一个用户接收或者发送。在跳频通信系统中,要完成电台之间的交互通信和信令传输,就需要设计出适合的帧结构和时隙分配方法。

2.1 帧结构设计

为了适应不同的功能需要[6],本文设计了以下4种帧类型:同步信息帧、确认帧、时隙分配帧和数据帧,帧结构设计如图1所示。

图1 帧结构

4种帧类型的区别仅在帧内容有所不同,具体帧内容为:

(1)同步信息帧:帧内容包括跳频剩余跳数和下一跳频率。跳频剩余跳数由计数器控制,当为0时,就进入跳频通信阶段;而帧中的下一跳频率,用于从机电台或迟入网电台实现频率跟踪。

(2)确认帧:帧内容包括目标电台号和确认信息位。用作从机给主机的反馈信号,网内从机电台收到时隙分配帧后,给主机反馈;迟入网电台收到同步信息帧后,在空闲时隙给主机的反馈。

(3)时隙分配帧:帧内容包括总共时隙数和目标电台的分配时隙号,用于主机向从机分配时隙。

(4)数据帧:作为网内数据通信的信息单元。帧内容为目标电台号和发送的数据内容。

2.2 时隙分配方法

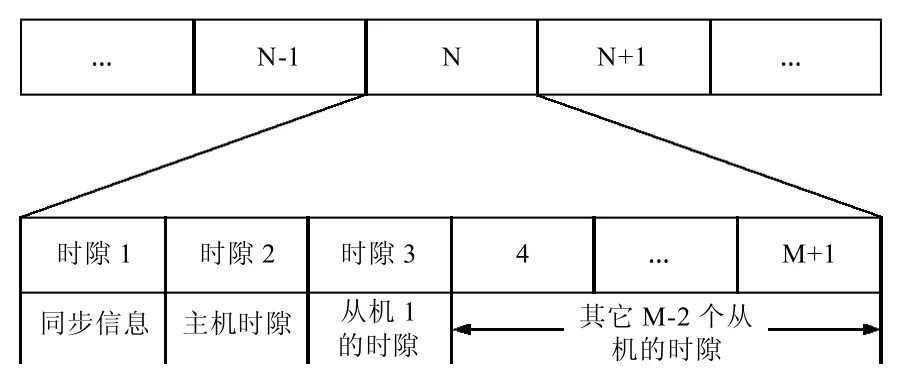

TDMA协议将时间划分为一定长度的时元,每个时元对应一个频点,每一跳上只有1个时元。每个时元划分为若干个时隙。每个时隙分配给一个从机发射信号,其它电台接收信号。假设网络中共有M个跳频电台,包括1台主机和M-1台从机,将一个时元分成M+1个时隙,如图2所示。

图2 时隙分配

每一个时元的第一个时隙由主机发送同步信息帧,有两个作用:一是实现从机与主机的时间同步,二是帮助从机完成迟入网;第二个时隙分配给主机使用,用于主机将数据发送给目标电台;之后的M个时隙分配给M个从机,用于各个从机将数据发送给目标电台。

3 同步过程

同步过程包括捕获与保持两部分。捕获过程包括频率同步和时间同步。每隔一个校验周期,进行一次组网调整,包括电台的新入网、保持入网和离开网络,同时也完成同步校验,如果出现错误,则电台进入迟入网状态,在捕获同步后的下一个组网时元重新入网。

3.1 同步信号的捕获

主机将自身的时间信息、同步信息和下一跳频率组合在同步信息帧中,向外发送。从机开机后,处于接收状态,搜索网络,接收网络同步信号(同步信息帧)。

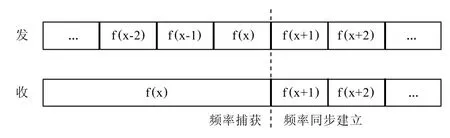

3.1.1 频率同步

从机在设定的频率上接收主机的信号,当主机跳变频率与从机相同时,从机捕获主机的同步信息,并跟随主机一起进行频率跳变,完成一个跳频扫描周期后,主从机同时进入跳频通信状态。其捕获过程如图3所示,f(x)表示电台在不同时刻的跳频频率,x表示跳频图案的顺序值[7-8]。

左达和徐艺同时笑起来,徐艺最后还是被左达的笑惊呆了。左达笑着站起来张开双臂看着天空,又突然转过头来看着徐艺。

图3 同步频率捕获过程

3.1.2 时间同步

频率同步是使收发双方跳频图案的时间差小于一跳的长度,而时间同步则要求收发双方每一帧都严格对应,本文采用同步头法进行时间同步,从机捕获到同步信息帧后,通过判断帧头和帧类型,对同步信息帧进行识别,完成了时间同步,使从机与主机严格对时,按位接收后面的信息帧,这样就完成了时间同步。其实现过程如图4所示,f(x)表示电台在不同时刻的跳频频率,x表示跳频图案的顺序值。

图4 同步信息捕获过程

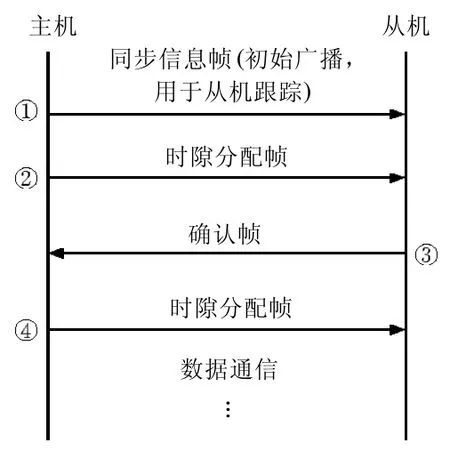

3.2 时隙分配

同步建立后,主机发送一个时隙分配帧,向各从机随机分配不同的时隙,然后转为接收状态,从机记录下时隙信息后,向主机反馈一个确认帧,用来声明占用此时隙。主机在各个时隙收完各个从机的反馈后,确认了网内从机数量和电台号,然后对入网的电台重新分配时隙,将多余时隙去掉。该组时隙分配帧发送完成后,整个网络进入数据通信阶段。时隙分配过程图如图5所示。

3.3 跳频数据通信

按照图1时隙结构图中的通信帧进行通信,每一跳有M+1个时隙。数据通信过程如图6所示。

第1个时隙用于发送同步信息帧,保持网络的同步状态,同时也用于向迟入网电台发送同步信息。后面M个时隙用于网内M个电台分别发送信息,在每个时隙,其它电台处于接收状态,接收自己的信息。

图5 时隙分配过程

图6 跳频数据通信过程

3.4 同步校验 (组网的调整)

跳频数据通信周期结束后,进行系统的同步校验,也完成组网的调整功能(包括电台的离开,发送请求,时隙调整等)。此过程与时隙分配过程类似,如图7所示。

图7 组网调整过程

丢失时隙的从机,有2种可能,一种是通信结束,时隙占用请求信号处于无效;另一种是通信失步,此时从机自动进入迟入网状态。

3.5 电台迟入网

跳频电台网络建立好之后,如果有电台想加入网络,需要进行迟入网申请。实现过程如图8所示。给每个电台设置成不同的初始频率,来接收主机在每一个数据通信时元内第一个时隙发送的同步信息帧,当网络频率跳变到迟入网电台的频率值上时,迟入网电台就可以接收到同步信息帧,然后开始跳频跟踪,当这一个跳频数据通信周期结束后,进入组网调整时元,从机在后面的空闲时隙,向主机发送确认帧。在后面的通信过程中,主机给其分配一个时隙,这样就完成了电台的迟入网。

图8 迟入网过程

综上所述,同步捕获过程主要采用同步头法,实现简单,同步建立速度快。之后则要借助精确时钟法,在每次对时之前,保持时间同步。

同步校验过程同时也是一次组网调整过程,弃掉失步电台,保留同步电台,有效地重新分配时隙;失步的电台则进入迟入网过程。本文提出的时隙分配方法以及组网调整过程,能够即时的减少多余空闲时隙并给新入网电台分配时隙,所以资源利用率比较高,同时能够降低各个从机电台的等待入网时间。

4 FPGA实现设计和仿真

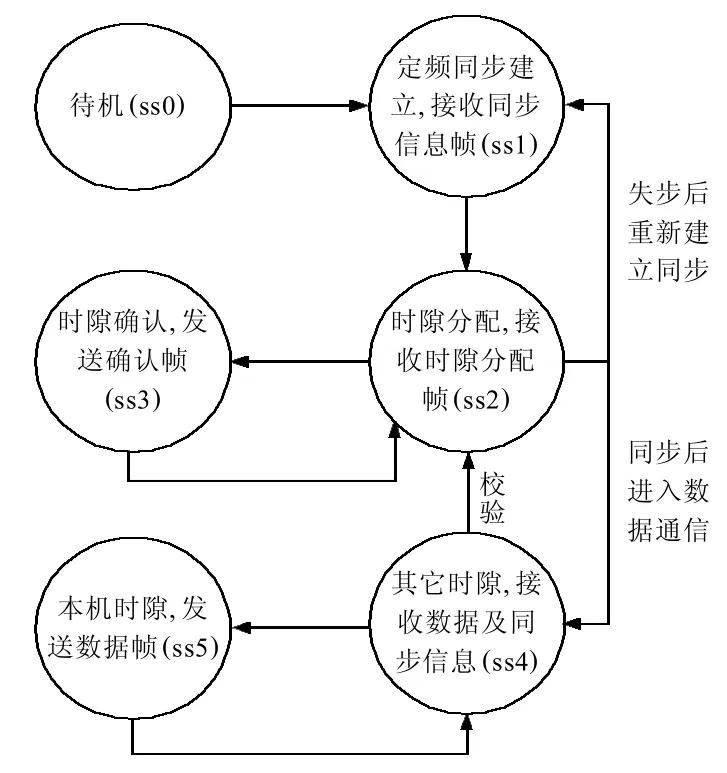

上述组网同步过程用FPGA仿真实现,主要设计两个状态机:主机状态机和从机状态机。如图9和图10所示。

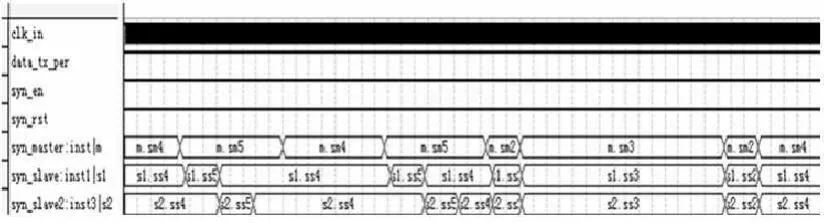

用Altera公司的FPGA开发软件Quartus2自带的Simulation对组网过程中的同步建立过程和同步校验过程进行观察,结果如图11和图12所示。syn_master为主机同步模块,syn_slave为从机1同步模块,syn_slave2为从机2同步模块。m表示主机状态机,范围为sm0~sm5;s1和s2表示从机1和2的状态机,范围为ss0~ss5。

图11显示了同步建立过程、时隙分配过程以及数据通信过程。开始阶段,主机和从机都处在待机状态,也就是sm0和ss0。主机在进入sm1状态后,开始广播同步信息帧,从机在ss1接收同步信息帧,并跟踪主机进行同步跳频,在完成跳频扫描周期后,主机进入sm2状态,从机进入ss2状态。此时就进入了同步状态。也就完成了同步建立过程。

主机进入状态sm2后,给各个从机广播时隙分配帧;从机处于接收状态ss2,接收时隙分配帧。广播结束后,主机进入状态sm3,从机收到时隙分配帧后,进入状态ss3。主机开始在各个时隙接收反馈的确认帧,从机在刚刚分配给自己的时隙发送确认帧。成功确认,则时隙保持;如果没有反馈,则主机在接下来进入状态2后把此时隙删除,重新给各个从机分配。在状态3完成后,主机再回到状态sm2,从机回到状态ss2,通过了解各个从机的反馈信息,重新合理分配时隙,到此完成了时隙分配过程。

图9 跳频电台主机状态机

图10 跳频电台从机状态机

图11 同步建立、时隙分配和数据通信过程仿真

重新分配时隙后,主机进入状态sm4,从机进入状态ss4。主机的状态sm4为发送数据,状态sm5为接收数据。从机的状态ss4为接收数据,状态ss5为发送数据。从图11中可以看出,主机的状态sm4和从机的状态ss5始终占据着不同的时隙。主机在状态sm4先发送一个时隙分配帧,用于给整个网络对时,也用于迟入网电台的跟踪,然后在下一个时隙发送数据给目标电台,结束后进入状态sm5,接收数据,当收到以自己作为目标电台的信息帧时,接收下来。从机在状态ss4接收其它电台的信息,当计时到达自己的时隙时,转到状态ss5,向目标电台发送信息帧。

图12显示了同步校验过程。一个跳频数据通信周期结束后,主从机同时进入同步校验状态,主机由状态sm5进入状态sm2,从机由状态ss4进入状态ss2。校验过程和图11中的时隙分配过程一样,校验结束后,主机由状态sm2进入状态sm4,同时从机由状态ss2进入状态ss4,再次进入数据通信过程。

图12 同步校验仿真

图13显示了跳频组网中电台迟入网过程。在整个系统的组网通信过程中,每一个时元的第1帧,为由主机发送的同步信息帧,迟入网电台通过接收同步信息帧,进行跳频跟踪,并在下一个同步校验时元,申请时隙。从机s1和s2和主机m处于同步过程中,从机s3迟入网,在syn_en3信号变为1后,申请迟入网,在ss1状态接收同步信息帧开始跟踪跳频,在ss2状态接收时隙分配帧,在 ss3状态反馈给主机确认帧申请迟入网,在下一个ss2状态,主机广播新的时隙分配帧,然后进入数据跳频通信状态。通过仿真图可以看到,迟入网前为4个时隙,迟入网后系统变成了5个时隙。

图13 电台迟入网过程

5 结束语

本文在实际跳频电台系统设计过程中,针对跳频电台的组网协议和同步方法,以其同步过程作为研究对象,分析了组网跳频电台同步过程中各个步骤的实现方案,整个方案设计在FPGA上实现,有效的实现了网络的建立和调整、同步的捕获和保持等功能。通过Quartus2软件的仿真结果,表明本文的同步方案实现简单,同步快速可靠,该方法在跳频电台的设计中具有一定的应用价值。

[1]白翔,于秦.基于TDMA的AdHoc网络跳频组网的实现[J].现代传输,2007(3):78-81.

[2]杨新华,王鹏.基于TDMA的跳频组网研究[J].电子测量技术,2009,32(2):60-62.

[3]李瑾,赵明生.数字跳频快速同步方案设计与FPGA实现[J].微计算机信息,2008,24(5-2):169-170.

[4]曾兴雯,刘乃安,孙献璞.扩展频谱通信及其多址技术[M].西安:西安电子科技大学出版社,2005.

[5]梅文华,王淑波,邱永红,等.跳频通信[M].北京:国防工业出版社,2005.

[6]吴文卓,张立毅.战术跳频通信系统同步技术研究[J].电子测量技术,2008,24(2-3):132-133.

[7]宋大风.基于TDMA的跳频系统基带设计[J].电讯技术,2008,48(10):73-75.

[8]将定顺,杨长雷.基于TDMA的高速跳频数传通信系统研究[J].重庆邮电学院学报,2004,16(4):57-60.

[9]王龙庆,杜栓义.跳频通信中的同步技术研究[J].电子科技,2006(7):29-35.

[10]李金涛,王祎.跳频通信组网研究[J].电子科技,2007(1):20-23.

[11]徐明霞,徐志江.利用跳频同步的Ad hoc网络时隙同步[J].电路与系统学报,2006,11(4):65-69.

[12]郑继禹,林基明.同步理论与技术[M].北京:电子工业出版社,2003

[13]胡中豫.现代短波通信[M].北京:国防工业出版社,2003.

[14]Ebner A,Rohling H,Lott M.Decentralized slot synchronization in highly dynamic ad hoc networks[C].Wireless Personal Multimedia Communications,2002:494-498.

[15]Ebner A,Rohling H,Halfmann R.Synchronization in Ad hoc networks based on UTRA TDD[C].Proc PIMRC,2002:1650-1654.