信道化接收机的暂态效应处理及频率编码器设计技术

王坤达

(船舶重工集团公司723所,扬州 225001)

0 引 言

信道化接收机是毗邻频率窗测频技术的具体实施,对同时到达信号具有潜在的分离能力,在现代高密度复杂信号环境下越来越受到电子侦察系统设计师们的亲睐。但是,暂态效应影响信道化接收机的窄脉冲测量能力以及频率测量精度,高脉冲信号密度、信号交叠情况影响信道化接收机的全概率截获和实时处理。针对这些难点,在不影响信道化接收机其它电性能指标,且不增加设备体积、重量的前提下,要是能通过频率编码器解决这些问题那将是解决这些难点的首选。

1 暂态效应及其对信道化接收机性能的影响

1.1 暂态效应分析

脉冲信号的频谱会在频域内扩展。假设一方形脉冲信号振幅为A,宽度为T,其时域表达式为:

上式对应的傅里叶变换为:

式中:t为时间;f为频率;ω=2πf。

在A=1的情况下,以分贝(dB)为单位画出的功率谱见图1。

图1 脉冲信号的功率谱

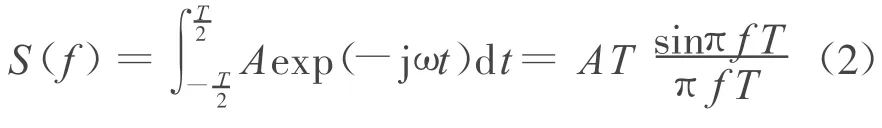

由图 1可以看出脉冲信号的功率谱曲线为sin(πf T)函数。在频域上,f以1/T为周期,T越小,脉冲信号的频率谱在频域上的扩散范围就越宽。在信道化接收机中信号通过滤波器组其能量会扩散到许多信道中,所有滤波器的输出都不与输入相类似,滤波器的输出信号在脉冲的前沿和后沿上有较大的幅度,这种现象称为暂态效应(或“兔耳”效应)。由于滤波器的边界对脉冲包络起微分作用,对应脉冲前后沿的暂态输出特别强,一般形象地称为兔耳信号。作为一般规律,信道化接收机中采用的滤波器带宽越窄,带外抑制越大,暂态效应就越明显。暂态效应在时域的示意图见图2。

图2 暂态效应在时域的示意图

暂态效应现象的频域解释指出,脉冲频谱中的旁瓣能量会通过滤波器的主要部分;而时域解释指出,由于包络幅度的改变而在前沿上升和后沿下降处会产生正弦载波失真。

1.2 对信道化接收机性能的影响

“兔耳”现象对信道化接收机来说是一个严重的问题,它意味着与远离真实信号载频的信道滤波器相联的差分放大器将被不希望的尖峰脉冲所触发,而且通常它将被单个尖峰脉冲触发2次。一般来说信号扩散到其他信道的能量增多,将引起多路相邻信道产生输出,造成对信号类别的判断错误和测频误差的增大。

解决这一难题的许多传统做法,由于设计困难或技术要求不能兼顾,工程应用上较少采用。在实际信道化接收机应用中,采用较多的有比幅法和限制滤波器输入信号动态法。比幅法,设备量庞大,且对窄脉冲的适应能力差;而限制滤波器输入信号动态法虽对暂态效应有明显的抑制效果,却牺牲了双音无虚假动态范围指标。

2 新型频率编码器设计

笔者提了一种时域同步连续采样和数字处理相结合的信道化接收机编码器设计方法,对暂态效应有很好的抑制效果。经实际测试,该方法较好地解决了由于信道带宽限制对窄脉冲信号测频能力的影响问题和传统限制滤波器输入信号动态法影响接收机双音无虚假动态范围的问题;同时还具有测频恢复时间短的特点,适应了复杂电磁环境下高脉冲密度、信号交叠情况的测量。

2.1 频率编码器设计概述

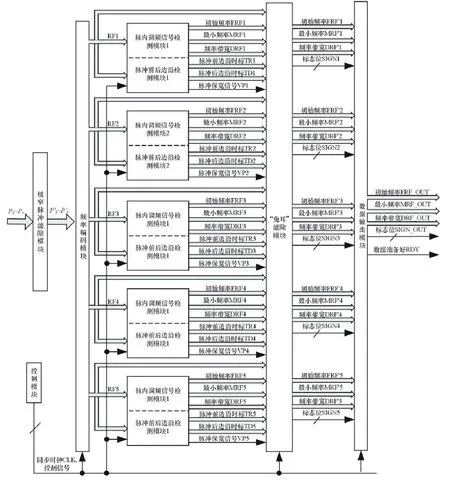

本频率编码器以现场可编程门阵列(FPGA)(Xilinx公司的XC5VLX50T)为硬件平台,对滤波器所有子信道的检波输出信号同时进行时域连续采样,极窄脉冲滤除,频率编码,脉冲前后边沿检测,脉内调频信号检测(计算出调频带宽和调频斜率),“兔耳”滤除,最后数据输出,整个流程尽可能采用并行处理、同步逻辑和流水作业的思路。总的设计框图如图3所示。

2.2 频率编码器详述

(1)极窄脉冲滤除块是将小于接收机脉冲宽度测量范围下限的信号滤除,其作用是消除“毛刺”信号误触发;消除窄脉冲或宽脉冲强信号在远离滤波器中心的其他滤波器通道引起的“兔耳”信号。为防止后续编码电路误触发和减小编码电路的编码误差进行预处理。

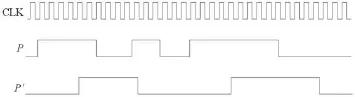

其实现方法是采用带同步清零的移位寄存器,若要滤除的极窄脉冲宽度为n个时钟周期,那么移位寄存器的移位深度设置为(n+1)。从检测到信号开始的第n+1个时钟去检测移位寄存器的入口是否有信号输入,若有,移位寄存器正常移位输出;若无,移位寄存器中所有内容清零。本设计采用的同步时钟频率为100 MHz,滤除的极窄脉冲宽度为50 ns,其时序图如图4所示。

所有滤波器子信道的检波整形信号(P1~Pn)经极窄脉冲滤除模块滤除掉极窄脉冲后形成信号P′1~ P′n,送频率编码模块。

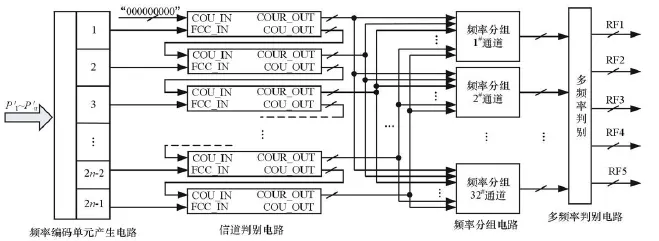

(2)频率编码模块是整个信道化接收机频率编码器的核心电路,主要由频率编码单元产生电路、信道判别电路、频率分组电路、多频率判别电路这些子模块组成。频率编码模块原理框图如图 5所示。整个信道化接收机频率编码器的设计思路是同步流水作业的思路,采用的同步时钟为100 MHz,对频率编码模块而言,从当前数据输入到下一个数据输入的时间为10 ns,也就是说频率编码模块要在小于10 ns的时间内出结果,所以频率编码模块的设计采用将数据尽可能并行处理、尽量减少串行通路环节、以资源换时间的思路。

图3 频率编码器设计框图

图4 极窄脉冲滤除模块时序示意图

(a)频率编码单元产生电路

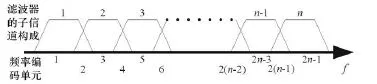

相邻滤波器的相邻边界有三分之一相互重叠构成了本设计中信道化接收机前端滤波器的子信道,即滤波器利用相互重叠区作为1路频率编码单元,将频率编码单元扩展到2n-1,测频精度提高了1倍。频率编码单元产生电路将输入的n个P′1~信号译码为2n-1个频率码单元。滤波器2n-1分频法示意图如图6所示。

图5 频率编码模块示意图

图6 滤波器2n-1分频法示意图

(b)信道判别电路

判断第几个频率编码单元存在信号,并对存在信号的频率编码单元进行编号,不存在信号的频率编码单元编号值为0,编号的顺序从频率编码单元1起始,本设计频率编码单元编号值最大为32(编号值大于32的不处理,此值可根据信道化接收机滤波器的子信道数量、“暂态效应”的敏感程度、最多处理多载频信号的数量等指标决定)。信道判别电路是由2n-1个信道判别器组成,每个信道判别器对应一个频率编码单元,信道判别器的端口定义如下:

FCC_IN:频率编码单元的输出指示信号;

COU_IN:相邻一侧信道判别器的编号值;

COU_OUT:信道判别器的编号值(不存在信号的频率编码单元编号值保持和COU_IN一样);

COUR_OUT:信道判别器的编号值(不存在信号的频率编码单元编号值置0)。

具体连接如图5所示。实现信道判别电路的方法很多,本方法消耗FPGA资源较多,但速度很快。

(c)频率分组电路

根据信道判别电路输出的编号值和与之相对应的频率编码单元数值将信号分到32个通道(本信道化接收机的滤波器子信道为200),信道判别电路输出的编号值为几,就将与之对应的频率编码单元数值存放到第几通道。如果信道判别电路输出的编号值最大为1,那么其余的31个通道数据填0,依此类推。频率分组电路用功能相同的32个频率分组器并行构成,其目的还是为了以资源换速度,提高其运算速度。

(d)多频率判别电路

由于暂态效应的影响,一个单频脉冲信号会在几个相邻滤波器都有响应,导致信道化接收机测频出错或是测频误差增大。多频率判别电路就是根据一定的判断准则,减少接收机虚警,提高测频精度。多频率判别电路将频率分组电路的各相邻通道数据进行比对,若几个相邻通道的数据彼此相差很小,则把这几个通道的数据合并为一个输出,例如,(n-1)#通道内的数据为(m-1),n#通道内的数据为m,(n+1)#通道内的数据为(m+1),则把这3个通道合并为一个通道输出,其合并后的通道数据为m。其判别合并通道的准则,与信道化接收机中使用的滤波器特性密切相关,本文在此不展开讨论。

本设计频率编码模块输出5个通道,5个输出通道(RF1~RF5)表示本接收机最多能处理5部同时到达信号(包括脉冲交叠的情况)。当然处理多少部同时到达信号是由系统的应用环境、接收机的瞬时带宽、测频精度、滤波子信道的总数量等因素决定。本设计中频率分组器的数量j为32,频率编码模块的输出通道数量k为5,j的取值和信道化接收机对测量脉冲信号时的“暂态效应”敏感程度息息相关。j的值取太大浪费系统资源,太小会导致接收机漏警。本设计 j的取值根据系统调试实际测定,并留有余量。

脉内调频信号检测模块和脉冲前后边沿检测模块。频率编码模块5个输出通道数据分别送往各自通道对应的脉内调频信号检测模块和脉冲前后边沿检测模块。脉内调频信号检测模块完成信号的初始频率FRF,最小频率MRF,频率带宽DRF的估算,初始频率FRF在脉冲保宽信号VP的前沿锁存输出,最小频率MRF和频率带宽DRF在脉冲保宽信号VP的后沿锁存输出。脉冲前后边沿检测模块产生脉冲保宽信号VP,并根据脉冲保宽信号VP产生脉冲前边沿时标TR和脉冲后边沿时标TD并锁存输出(TR在VP前沿锁存输出,TD在VP后沿锁存输出)。送往后续“兔耳”滤除模块的VP信号含有了后续模块所需的脉冲宽度信息,并用作后续模块工作的时序参考;T R和TD信号则含有了后续模块所需的脉冲前后边沿到达时刻信息。

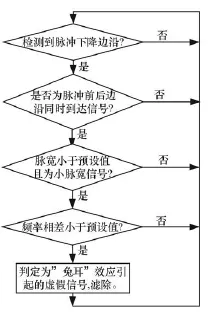

(4)“兔耳”滤除模块是对接收机由于“兔耳”效应带来的虚假信号进行滤除,并产生相关的标志位(连续波标志、大脉宽标志、多信号标志、频率分集信号标志等),标志位的产生本文不再多述。对“兔耳”效应带来的虚假信号滤除在脉冲的后沿结束后进行判断。若判断脉冲后沿同时结束的准则为相差n个时钟,则锁存脉冲前后沿时标的时刻应从检测的脉冲后沿时向后延迟(n+1)个时钟进行,以保证正常锁存后结束的脉冲后沿时标。此时判断脉冲前后边沿时标,若存在脉冲前沿同时到达或是脉冲后沿同时结束,频率RF相差小于预设值,脉冲宽度小于预设值,此脉冲宽度小于与之比较的脉冲前后边沿同时到达的脉冲宽度,则认为是“兔耳”滤除。之所以考虑频率相差要小于预设值,是因为当频率相差较大且脉冲前沿同时到达的将其判定为频率分集信号。“兔耳”滤除的判断流程如图7所示。

(5)数据输出模块将上级模块送来的数据进行缓存,并按一定的准则排序输出。“兔耳”滤除模块送来的5部信号数据,在数据输出模块中都对应1路FIFO先进行缓存,然后通过同步送数时钟对各FIFO进行依次快速轮循读取。为避免因外部信号脉冲密度的不一致而导致脉冲信号密集的FIFO来不及被读取而丢失数据的情况,各FIFO的读数准则采用:当读取某FIFO时,发现该FIFO数据深度大于3,对该FIFO进行连续读取,直至该FIFO读空,再对其它FIFO进行轮循读取。这样很好地解决了信号密集情况下(尤其是同时到达信号情况下)数据输出丢失的问题。

图7 “兔耳”滤除的判断流程图

(6)控制模块提供各模块的同步工作时钟,完成时分控制、复位控制以及自检和通信等功能。

3 结束语

笔者提出的这种时域同步连续采样和数字处理相结合的信道化接收机编码器设计方法,对暂态效应有很好的抑制效果。经实际测试,该方法较好地解决了由于信道带宽限制造成对窄脉冲信号测频能力的影响问题和传统限制滤波器输入信号动态法影响接收机双音动态范围的问题;同时还具有测频恢复时间短的特点,能够对复杂电磁环境下高脉冲密度信号完成全概率截获和实时测量;并能对脉内调频信息进行检测,易于在各种信道化频率编码器之间移植。

[1]James BaoYen Tsui.电子战微波接收机[M].龚金楦,顾耀平,李振初,等译.成都:电子部 29所情报室,1986.

[2]Wiegand Richard J.雷达电子对抗系统设计[M].龚金楦,顾耀平,李振初,等译.成都:电子部 29所情报室,1993.

[3]林象平.雷达对抗原理[M].西安:西北电讯工程学院出版社,1985.

[4]罗景青.雷达对抗原理[M].北京:解放军出版社,2003.