一种6.9 ppm/℃ 92 dB PSRR基准电压源的设计

梁 建,陈向东,陈建立

(西南交通大学 信息科学与技术学院,四川 成都610031)

基准电路广泛应用于模拟电路、数字电路以及数模混合电路。基准电压可不随供电电压、温度变化甚至工艺的变化而变化[1]。传统的带隙基准电压具有一阶温度特性,由具有负温度系数的双极型BE结电压VBE和具有正温度系数的热电压VT组合得到。由于VBE的非线性,一阶温度特性基准,其温度系数在 20 ppm/℃~100 ppm/℃[2-4]。为了得到具有更低温度系数的基准,设计基准时引入了高阶补偿技术,如Soog提出的二次温度补偿技术[5];Lee提出的指数曲率补偿[2];Rincon-Mora提出分段线性曲率补偿[3,6]及 Leung提出的利用高阻多晶电阻和扩散电阻的温度特性进行补偿[7]。以上方法的基本思想是引入高阶项以抵消VBE温度系数的高阶项。要提高电源抑制比(PSRR),可以使用共源共栅(cascode)技术、利用电容滤除噪声技术或者输入电压预调整技术[6]。本文提出了一种宽电源电压范围、低温度系数、高PSRR的带隙基准电压源,通过放大反向饱和电流IS实现指数曲率温度补偿,使用Wilson电流镜和电压负反馈技术提高PSRR。

1 曲率补偿方法

1.1 晶体管基射极电压VBE的温度特性

双极型晶体管通常被用来实现带隙基准电压源,当BJT工作在线性放大区时,BE结电压的表达式为:

从式(1)可知,VTlnT显示出VBE的高阶温度非线性项。当在T0点进行泰勒展开时,VTlnT可以表示为:

一阶温度补偿涉及到抵消温度T的一次项,而高阶温度补偿涉及到抵消温度T的高次项。因此,高阶温度补偿不能仅仅通过传统的线性补偿来实现。

1.2 指数曲率补偿的原理[1]

本文提出的曲率补偿技术如图1所示,它由晶体管NV14和 NV15组成,补偿电流ICOMP注入到节点 B,此时基准电压可以表示为:

其中,ICOMP=βIS,而IS由BE结短接的 NPN晶体管NV14形成。IS可以表示为:

双极型晶体管的电流放大倍数β是一个与温度成指数关系的函数,它可以表示为:

结合式(4)、式(5)得:

结合式(3)和式(7)可得:

2 电路实现原理

本文提出的指数曲率补偿带隙基准电压源的整体电路原理分三部分:

(1)启动过程

电路刚上电时,C点没有电流流出,因此基准不工作,基准输出电压VREF=0,晶体管NV6截止。由于晶体管NV9、NV10的钳位作用,使得 D点电压为 2VBE,因此NV7导通,E点的电位被拉低,使得PL2导通。这样启动电路会给基准核心灌入一股电流ISTART,使得基准核心电路摆脱零工作状态的简并点。此时VREF正常工作,NV6导通,晶体管NV10的基极F点的电位升高,D点的电位降低,使得NV7截止,从而给基准核心电路提供一个恒定持续的启动电流。

(2)一阶补偿基准核心

如图 1所示,PL5、PL6、PL7为威尔逊电流源并与NV1、NV2、NV3、R0、R1 以 及 Trimming 修 条 电阻 组成基准核心电路。其中NV12起到预调整的作用,它可以使得H点的电位更加稳定;NV18与R12形成过流保护电路,当电路正常工作时,NV18处于截止态;RT11~RT34为trimming修条电阻可以提高流片后基准源的精度;NV5、NV4、NV16、NV17 和电阻 R12 一起 形成反 相电 压放大电路,与基准核心一起组成负反馈回路,以产生稳定的基准电压;NV11为米勒补偿电容,在A点产生一个低频主极点,从而保证整个环路的稳定。

3 实验结果与讨论

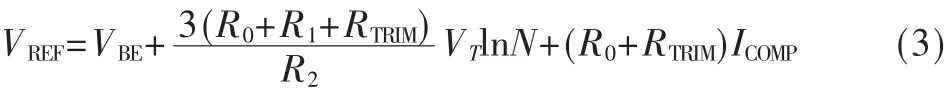

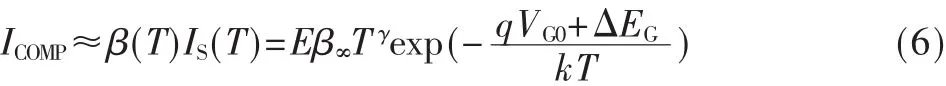

本文提出的基准电压源,使用商用 0.5 μm Bipolar工艺模型进行仿真验证。基准输出电压分别在4.5 V、10 V、35 V的电源电压下,温度从-40℃~+135℃变化时,最小仅产生0.12%的变化,如图2所示。在4.5 V的电源电压下,温度系数仅为6.9 ppm/℃;在电源电压从4.5 V变化到35 V时,温度分别为-40℃、25℃、135℃,而基准输出电压的最大波动也仅为3 mV左右,如图3所示。当电源电压为35 V时,电源电压抑制比可以高达92 dB,其电路版图如图4所示。

本文设计、验证了一种高阶指数曲率补偿带隙基准电压源。利用反向饱和电流IS和β参数的正温度特性,产生正温度系数的PTAT电流,以补偿二阶指数曲率。在电源电压 4.5 V、温度从-40℃~+135℃变化时,达到6.9 ppm/℃的温度系数。如图5所示,在电源电压从4.5 V~35 V变化时,PSRR均高于80 dB,并且在35 V的电源电压下,PSRR高达92 dB。因此,该带隙基准电压源,可以广泛应用于宽电源电压范围的电源管理IC电路中。

图5 带隙基准电压源的电源电压抑制比

[1]WENG R M,HSU X R,KUO Y F.A 1.8 V high-precision compensated CMOS bandgap reference[C].IEEE Conference on Electron Devices and Solid-State Circuits,2005.

[2]KIM I L G,KIM W.Exponential curvature compensated BiCMOS bandgap references[J].IEEE J.Solid-State Circuits,1994,29(11):1396-1403.

[3]RINCONM G A.Voltage references from diodes to precision high-order bandgap circuits[J].IEEE Press,Wiley Interscience,2002,26(11):1023-1032.

[4]Chen Jianghua,Ni Xuewen,MO B.A curvature compensated CMOS bandgap voltage reference for high precision applications[C].7th International Conference on ASIC,Oct.2007.

[5]SONG B S,GRAY P R.A precision curvature compensated CMOS bandgap reference[J].IEEE J.Solid-State Circuits,1983,18(6):634-643.

[6]RINCONM G A,ALLEN P E.A I.I-V current mode and piecewise linear curvature corrected bandgap reference[J].IEEE J.Solid-State Circuits,1998,33(10):1551-1554.

[7]LEUNG K N,MOK P K T,LEUNG C Y.A 2-V 23-fA 5.3 ppm/℃curvature-compensated CMOS bandgap voltage reference[J].IEEE J.Solid-State Circuits,2003,38(3):561-564.