双极工艺下一款高共模输入电平迟滞比较器的电路设计

电子科技大学电子薄膜与集成器件国家重点实验室 侯晋昭 余清华 代 杰

1.引言

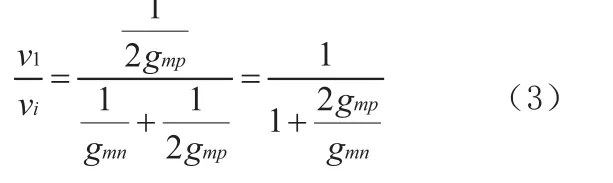

电源管理芯片需要设计过压保护模块以确保负载在安全的电压范围内工作。过压保护模块一般通过电阻分压对输出电压进行采样,和芯片内部基准电压进行比较。如果输出电压的变化量一定,则比较器的共模输入电平设定得越高,采样电压即比较器输入电压的变化量越大,环路的灵敏度越高。

高共模输入电平运算放大器放的设计是IC设计中极具挑战的课题之一。对双极工艺,为了使运放的共模输入电平达到电源电压,可以增加一级射随器做为电位平移,但同时增加了功耗。

本文设计了一种基于双极工艺的高共模输入电平低功耗迟滞比较器,不用加入一级射随器做为电位平移,就可以使共模输入电平达到芯片内部的次级电源电压,而且可以方便的调整迟滞电压。该迟滞比较器用于一款升压型PFC电源管理芯片的过压保护模块,并用1um双极工艺实现,共模输入电平为电源电压7.4V,迟滞电压为O.5V,功耗约为O.74mW。升压转换器的原理参考文献[1]。

2.电路设计

2.1 迟滞比较器原理

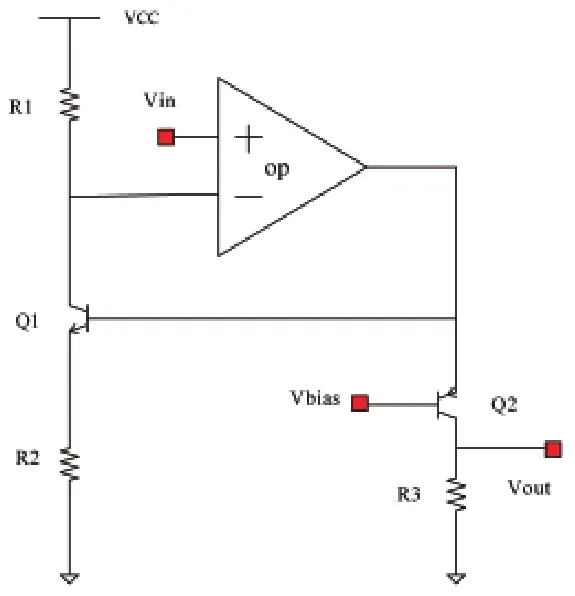

如图1所示,迟滞比较器由一个运算放大器和门限电压(VH、VL)转换电路组成[2]。

当升压变换器的输出电压在正常范围内时,其电阻分压Vin+小于VCC,op输出低电平,Q1和Q2均关断,Vin-为VCC,记做VH=VCC;此时Vout为低电平,该使能信号使芯片其它模块正常工作。

如果升压变换器的输出电压过高使Vin+超过VH,op输出电平升高至Q2导通,R3上有电压降,Vout为高电平,该使能信号关断芯片的输出,使升压变换器的输出电压降低,此时Q1的发射极电位被钳位在Vbias,即R2上的压降为Vbias,则R1上的压降为

此时Vin-为VCC-VR1,记做VL=VCC-VR1。当Vin+下降到VL以下后,输出才再次翻转,芯片正常工作。迟滞电压由公式(1)确定,通过调节Vbias和R1、R2的大小,可以方便的调整迟滞电压。

2.2 高共模输入电平运放的设计

图1 迟滞比较器原理图

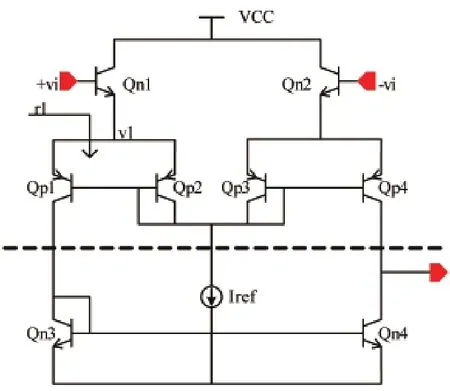

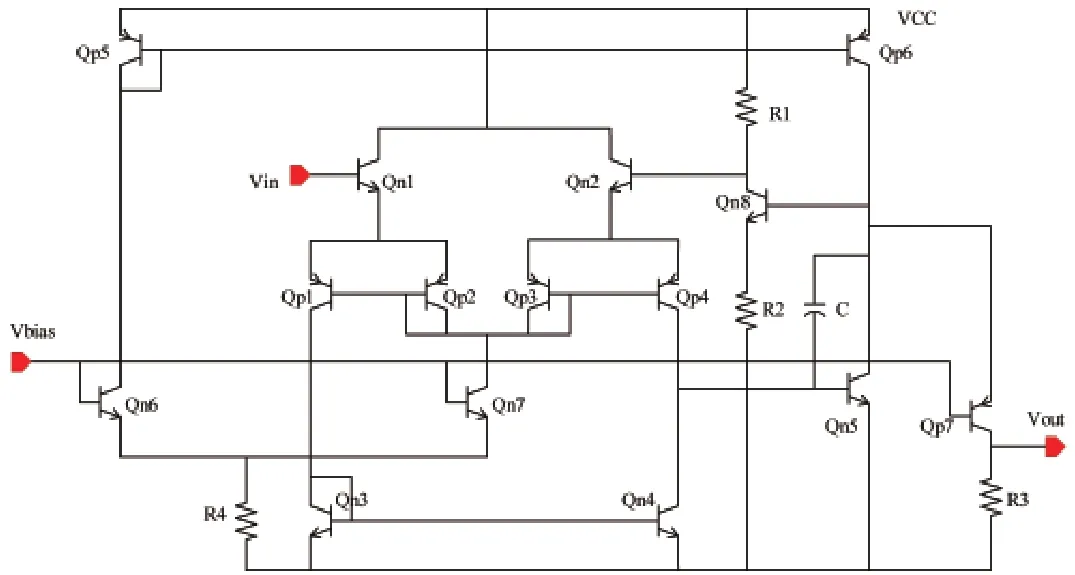

图2 高共模输入电平运算放大器

文献[3]和文献[4]介绍了几种高共模输入电压范围的CMOS运算放大器的设计。对CMOS工艺,采用NMOS做为输入对管的折叠式共源共栅结构的运放,可以使共模输入电平达到电源电压。但对双极工艺,由于三极管和MOS管工作在放大区的条件不同,采用类似的NPN做为输入对管的折叠式共源共栅结构的运放,共模输入电平也只能达到VCC-O.7V。虽然可以增加一级射随器用作电位平移,但同时增加了功耗。

本文设计的基于双极工艺的高共模输入电平低功耗运放如图2所示,不用引入一级射随器做为电位平移,就可以使共模输入电平达到芯片内部的次级电源电压。

因为共模输入电平为VCC,所以必须采用集电极接VCC的NPN作为输入对管,有源负载和偏置电流源只能放置在NPN输入对管的同一侧。图2中所有电流镜均为1:1的镜像电流源。Qn1和Qn2为集电极接VCC的NPN输入对管,Qp1~Qp4为运放提高2Iref的偏置电流,Qn3和Qn4为有缘负载。

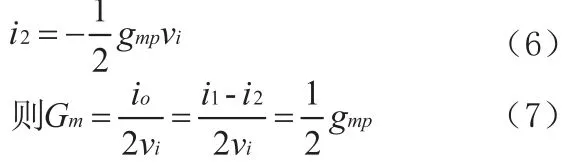

计算运放的跨导。假设Qn1的基极电位升高vi,Qn2的基极电位降低vi,降输出短路到地;由对称性可知Qp2和Qp3的集电极虚地。从Qn1的发射集向下看到的交流电阻为

Qn1为射随器,则

由大信号条件可知,

则Qp1、Qp2、Qn3、Qn4的集电极电流增量为

图3 迟滞比较器电路

图4 迟滞功能仿真

图5 未进行补偿时的环路波特图

图6 进行补偿时的环路波特图

同理,Qp3和Qp4的集电极电流增量为

开环电压增益为

由公式(9)可知,该运放的电压增益为一般有缘负载差动放大器电压增益的一半,增大Iref或者同比例增加Qp1和Qp4并联数可以提高电压增益,也可以采用增加一级共射放大器的方法。

2.3 迟滞比较器整体电路设计

如图3所示,Qn6、Qn7,Qp5、Qp6和R4为电路提供偏置;Qn1~Qn5,Qp1~Qp4和C为高共模输入电平的两级运放,其中Qn5为第二级共射放大器,进一步提高了增益,而电容C对运放进行了密勒补偿,使环路稳定;Qp7、Qn8和R1、R2、R3组成了上下门限电压切换电路。所有电流镜均为1:1镜像电流源。

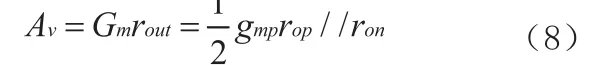

计算迟滞比较器的功耗。当vin+低于VH时,Qn5的集电极为低电平,Qn8和Qp7均关断,Vout=O,此时迟滞比较器的功耗为

由公式(11)可知,过压发生时,迟滞比较器的功耗增大。

2.4 仿真和测试结果

仿真软件使用spectre,仿真工艺库为上华(CSMC)1um双极工艺。设计芯片内部次级电源电压VCC为7.4V,Vbias为1.22V,R1=2O kΩ,R2=5O kΩ,R3=2O kΩ,R4=1O kΩ,所有的电流镜均为1:1镜像电流源。

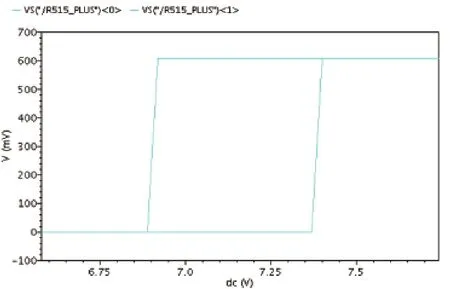

2.4.1 迟滞功能仿真

如图4所示,迟滞比较器的上门限电压VH为7.4V,下门限电压VL为6.9V,迟滞电压约为O.5V,输出高电平约为O.6V。迟滞电压和输出高电平的仿真结果与公式(1)和(1O)相符。迟滞比较器的功耗约为O.74mW。

2.4.2 运放频率特性仿真

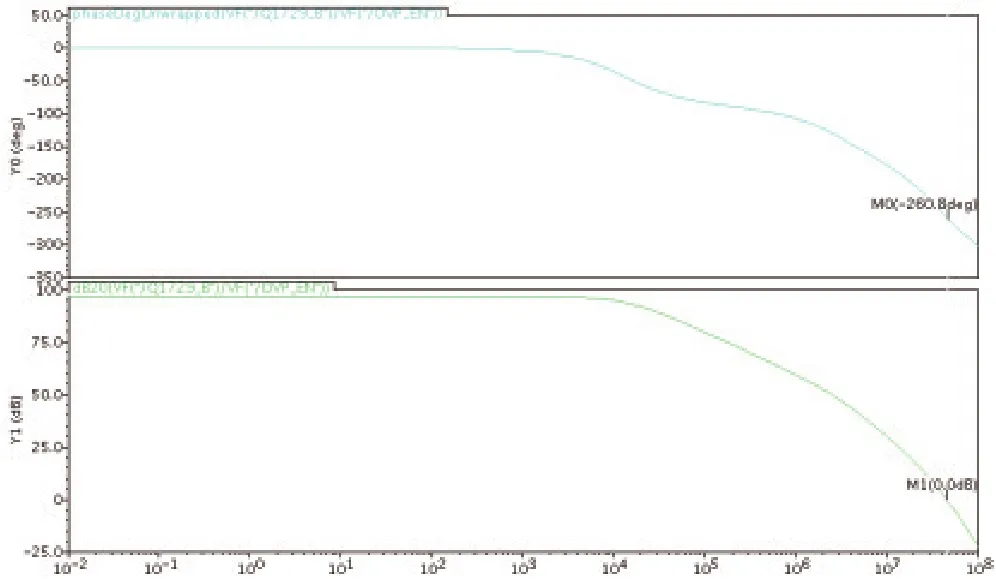

迟滞比较器的运放为2级运放,会引入三个极点;文献[5]说明了迟滞比较器处于一个负反馈环路中,根据文献[6],该运放引入的三个极点有可能造成稳定性方面的问题,所以需要对运放进行补偿。考虑最坏情况,假设反馈系数为1。

当没有电容C时,环路的波特图如图5所示,相位零点在增益零点左边,环路有可能产生振荡。

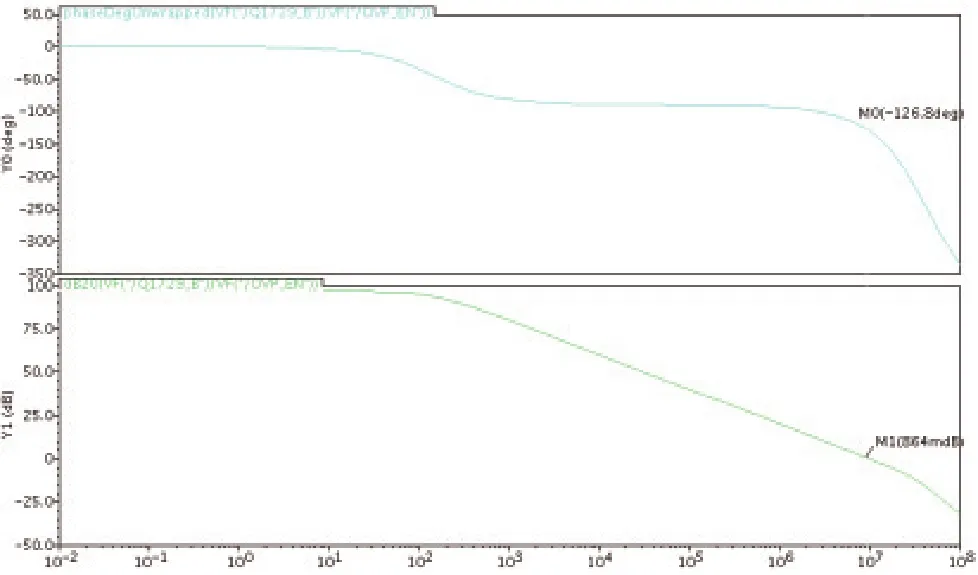

当在Qn5的基极和集电极间加上电容时,由于密勒效应,给系统增加了一个较大的负半平面极点,因此可以加速增益的衰减,提高相位裕度。当加上3pF的电容C时,环路的波特图如图6所示,其相位裕度提高至约6O°,极大地提高了系统的稳定性。运放的低频开环增益约为1OOdB。

3.结论

本文所设计的基于双极工艺的迟滞比较器具有高共模输入电平和低功耗的特点,并且可以方便的调整迟滞电压。并对两级运放进行了补偿,消除了环路稳定性方面的隐患。电路分析和仿真测试结果都表明,这款迟滞比较器具有很高的实用性和广泛的适用性。

[1]Abraham I.Pressman,Keith Billings,Taylor Morey.Switching Power Supply Design[M].Third Edition,New York:McGraw-Hill Company,2009:671-672.

[2]徐静萍.DC-DC转换器中低压迟滞比较器的电路设计[J].西安邮电学院学报,2011,16(1):91-93.

[3]Xian Li,Changyuan Chang,Juan Li.A Rail-to-Rail Op Amp for VLSI Cell With Constant Performance[C].Circuit Theory and Design.European.2007:16-19.

[4]牛秀卿,何人人.一种高共模输入范围高电压输出摆幅的COMS运算放大器[J].南开大学学报,1997,4(1):20-23.

[5]武振宇.均流、连续升压型PFC芯片的分析与设计[D].成都:电子科技大学,2007.

[6]毕查德拉扎维著.陈贵灿,程军,张瑞智译.模拟CMOS集成电路设计[M].西安:西安交通大学出版社,2003:289-315.