基于Nios II步进电机控制器IP核的设计与实现

刘洪朋,葛广英

(聊城大学物理科学与信息工程学院,山东聊城 252059)

随着系统级芯片集成度越来越高,SOPC技术成为电子系统设计的热点。它是利用FPGA器件的可编程性进行SOC设计,其最突出优点是在提供丰富IP库的情况下,用户可以利用IP库中的组件按需求来搭建系统,有较大的灵活性。但是在供应商提供的IP库中没有用户所需的IP核时,用户只能根据需要自定义IP核。另外,FPGA的传统应用是在通信、工业控制等领域。鉴于此,设计了一款步进电机控制器IP核,它具有对步进电机的转速、转向及运转节拍数进行控制的功能。

1 步进电机驱动原理

步进电机驱动是通过按一定顺序切换每相线圈中的电流,以达到旋转切换步进电机的过程。其中,步进电机的控制转速与各绕组中输入脉冲的频率成正比,转向则取决于控制绕组中的通电顺序。步进电机按其励磁相数可以分为三相、四相、五相、六相甚至八相制式。其中工业常用的是三相、四相励磁制式。其中三相制式又包括单三拍(A-B-C-A)方式及双三拍(AB-BC-CA-AB)方式,而四相制式则有三种常见方式,即双四拍(AB-BC-CD-DA-AB)方式;单四拍(A-B-C-D-A)方式;单、双八拍(A-AB-BBC-C-CD-D-DA-A)方式。

2 步进电机控制器IP核设计

对于面向Nios II处理器开发的所有IP核,包括从设备IP核和主设备IP核两大类。文中设计的步进电机控制器IP核是一个受控对象,属于从设备。Nios II处理器通过Avalon总线对步进电机控制器IP核的寄存器进行参数设置,实现对步进电机的一系列操作。其中Avalon总线接口规范的功能是它定义了信号类型、信号的行为及传输类型等信息。

一个典型的IP核由硬件文件、软件文件及组件描述文件组成,步进电机控制器IP核也严格按照规范来编写。它的硬件文件由多个HDL模块组合完成硬件设计,其中包括逻辑任务模块、寄存器模块及接口模块,其原理如图1所示,软件文件则由寄存器头文件、驱动文件组成。Nios II开发工具自2006年公布新版本以后,软件可以自动生成组件描述文件。

2.1 硬件文件设计

IP核设计部分中的逻辑任务模块根据寄存器模块传递的参数产生步进电机控制所需的脉冲信号;寄存器模块则用来存储Avalon总线传来的参数,包括步进电机的转速、励磁相数、正/反转参数、节拍数等;接口模块是一个符合 Avalon规范的接口,起着连接Avalon总线与IP核寄存器模块桥梁的作用。

图1 Avalon接口硬件电路原理图

2.1.1 逻辑任务模块设计

产生控制步进电机所需的脉冲信号一般可以采用ROM查表法或状态机法。本文采用状态机法,即状态机的每个状态输出一种脉冲信号。以四相单、双八拍制式来控制步进电机举例进行说明,其模块设计原理如图2所示,图中共有8种状态,每种状态对应每种输出状态。该制式电机相位顺序为A-AB-B-BCC-CD-D-DA,那么输出状态即为1000-1100-0100-0110-0010-0011-0001-1001。

图2 采用状态机设计步进电机控制驱动原理图

逻辑任务模块采用VHDL语言进行编写,本模块采用控制规则如下,其中,xiangwei为控制电机的相位;direction为控制电机正/反转位;pai为选择节拍数位。

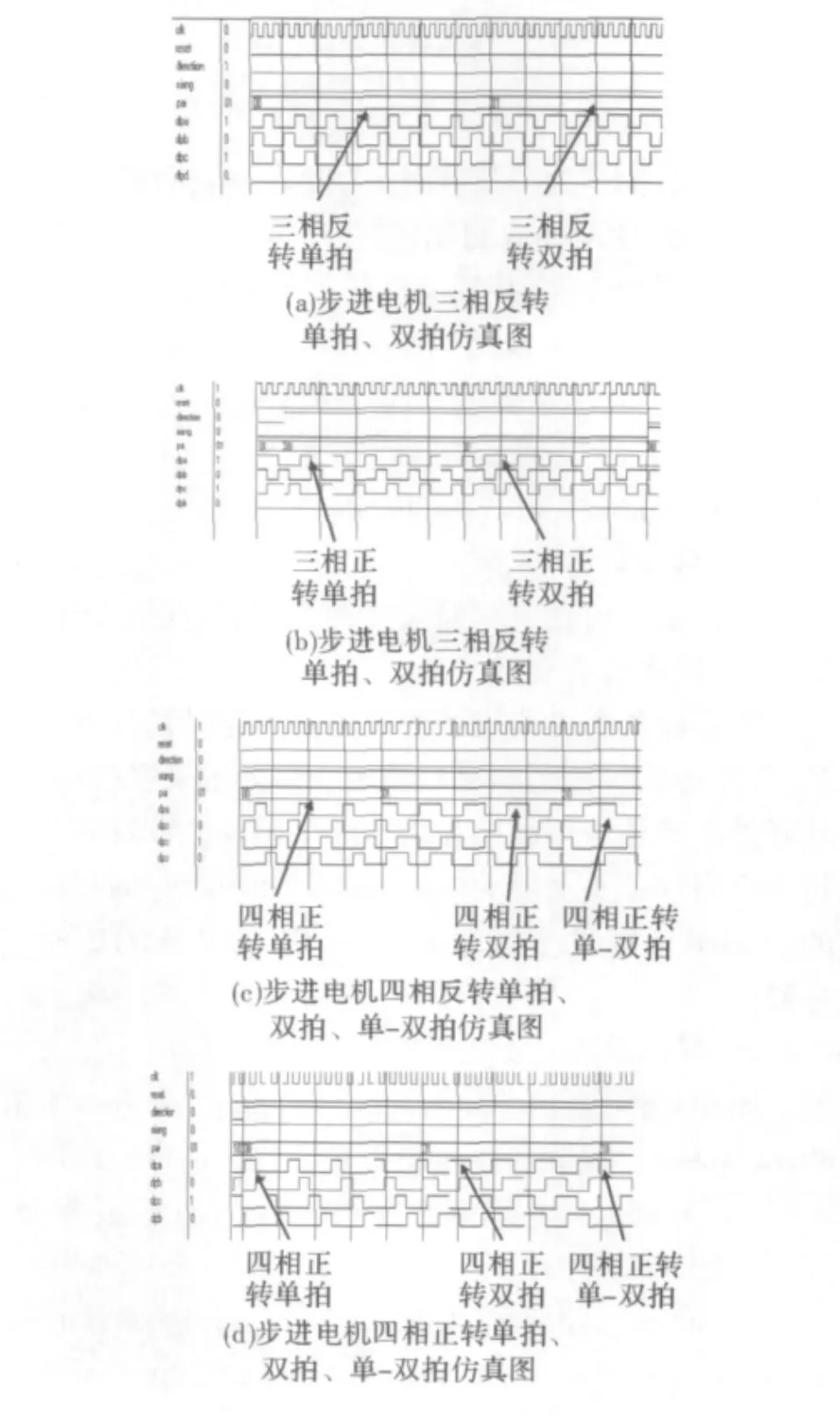

(1)如果 xiangwei为 0,direction 为 0,pai为 00,电机转向为C-B-A-C(三相单拍反转)。

(2)如果 xiangwei为 0,direction 为 0,pai为 01,电机转向为CB-BA-AC(三相双拍反转)。

(3)如果 xiangwei为 0,direction 为 1,pai为 00,电机转向为A-B-C(三相单拍正转)。

(4)如果 xiangwei为 0,direction 为 1,pai为 01,电机转向为AB-BC-CA(三相双拍正转)。

(5)如果 xiangwei为 1,direction 为 0,pai为 00,电机转向为 D-C-B-A(四相单拍反转)。

(6)如果 xiangwei为1,direction 为 0,pai为 01,电机转向为DC-CB-BA-AD(四相双拍反转)。

(7)如果 xiangwei为 1,direction 为 0,pai10,电机转向为D-DC-C-CB-B-BA-A-AD-DC-CCB-B-BA-A-AD(四相单、双拍反转)。

(8)如果 xiangwei为1,direction 为 1,pai为 00,电机转向为A-B-C-D(四相单拍正转)。

(9)如果 xiangwei为1,direction 为 1,pai为 01,电机转向为AB-BC-CD-DA(四相双拍正转)。

(10)如果 xiangwei为 1,direction 为 1,pai为 10,电机转向为A-AB-B-BC-C-CD-D-DA(四相单、双拍正转)。

根据上述控制规则编写逻辑任务模块程序并进行仿真,得到仿真结果如图3所示,所得结果与设计要求一致。

图3 逻辑任务模块仿真图

2.1.2 寄存器模块

寄存器模块的作用是存储IP核与外界交换的信息。驱动程序可以通过Avalon接口采用“基地址+地址偏移量”的方式读取各寄存器的数据。设计一共有3个寄存器,即方向寄存器、励磁制式选择寄存器、节拍寄存器。设计方法:在reset无效,clock和write有效的前提下,若address信号为“00”时,writedata数据则写入方向寄存器direction中;当address信号为“01”时,writedata数据写入节拍寄存器pai中;当address信号为“10”时,writedata数据写入励磁制式选择寄存器中。对此模块进行编程仿真,仿真结果如图4。图中可以看到当address为00时,方向寄存器direction数据与writedata的数据都为1;address为01时,节拍寄存器pai数据与writedata数据相同;address为10时,励磁制式选择寄存器xiang数据与writedata一致。

图4 寄存器接口仿真图

2.1.3 接口模块

接口模块作为顶层模块,为寄存器文件模块提供了一个标准的Avalon前端,它使用Avalon必需的信号来访问寄存器文件,并且支持任务逻辑的传输类型,负责复位、片选、寻址及对内部寄存器进行读写等,主要完成从Nios II处理器接收指令和数据。对于步进电机控制器 IP核,用到接口模块信号有:clk,reset,chipselect,address,write,writedata 信号。

2.2 软件设计

软件设计包括寄存器头文件、驱动软件的设计。

2.2.1 寄存器头文件

寄存器头文件定义了外设的底层硬件访问接口信息,程序员只需使用定义与该头文件的宏来操作外设,其好处在于使应用程序独立于底层硬件。设计首先创建一个寄存器头文件altera_avalon_stepping_regs.h,它的功能用于描述步进电机控制IP核设备的3个寄存器。

2.2.2 驱动软件

驱动软件包括altera_avalon_stepping_routines.h和altera_avalon_stepping_routines.c文件。altera_avalon_stepping_routines.h定义了驱动函数的原型及常量。其函数定义语句为:

int altera_avalon_stepping_init(unsigned int address,unsigned int data1,unsigned int data2,unsigned int data3,int error);

int ltera_avalon_stepping_enable(unsigned int address);

int tera_avalon_stepping_disable(unsigned int address);

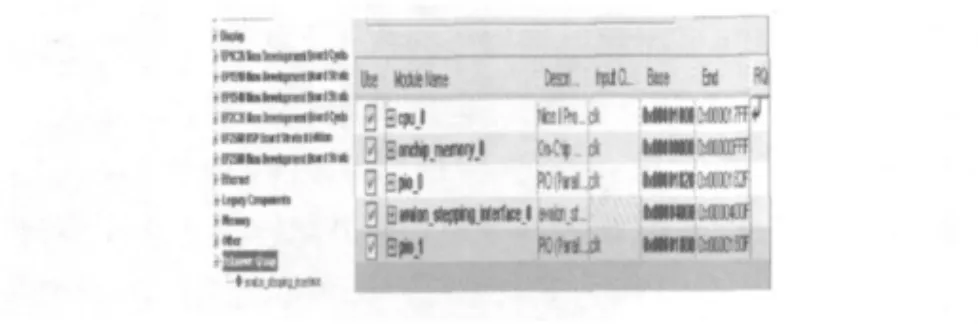

3 生成IP核

将软硬件文件编译完毕后,就需要在SOPC Builder软件中利用Component Editor生成工具封装成自定义组件。设置好HDL files、Signals、Interface以及SW files选项后,生成的IP核便成功设置在组件框内。利用此IP核即可与其他IP核联合搭建构成一个步进电机嵌入式控制系统。整个系统结构图如图5所示。

图5 步进电机控制器IP核及由其搭建的系统结构

4 结束语

提出的基于Nios II的步进电机控制器IP核设计采用的软件平台是Quartus II6.0和Nios II IDE6.0,硬件平台采用康芯公司的SOPC实验系统,步进电机控制IP核的占用资源为20%,它可以移值到所有Altera公司支持SOPC技术的芯片上。采用SOPC技术设计的自定义步进电机控制IP核,在提高效率、缩短开发周期的前提下,可以满足工业控制场合的需要及开源升级。

[1]潘松,黄继业.EDA技术实用教程[M].北京:科学出版社,2010.

[2]李兰英.Nios II嵌入式软核SOPC设计原理及应用[M].北京:北京航空航天大学出版社,2009.

[3]郑恭明,沈媛媛.基于Nios II的伪随机序列信号发生器IP核设计[J].工矿自动化,2011(2):52-55.

[4]高枫,王玉松.基于NiosII自定制Avalon设备的设计与实现[J].中国测试技术,2007,33(4):105 -108.

[5]殷苏民,杨仁宇.基于Avalon总线的插补器IP核的设计[J].机械设计与制造,2009(8):198 -200.

[6]章智慧,白瑞林,沈宪明.面向SOPC Builder的用户自定义 IP 核开发[J].自动化仪表,2006,27(9):23 -26.