基于FPGA高速数据采集与传输的声幅测井系统

杨永侠,李亚炜

(西安工业大学电子信息工程学院,陕西西安 710032)

地球物理测井的方法有多种,如电测井、声波测井、核测井、地层倾角测井、成像测井等,但声波测井是惟一可以获得井壁直观图像的测井方法。声波测井和电法测井,核测井相比,问世较晚,但近20年来发展迅速,其主要优点是不受泥浆性质,矿化度及泥浆侵入的影响。同样,岩石声学研究了声波在岩石或地层中的产生、传播、接收和各种效应,为声波技术发展提供了理论基础。所谓声波是指弹性介质中传播的压强、应力、体积元形变,质点位移,质点速度等的形变或几种形变的综合。最简单的声波测井仪由发射器和接收器组成,接收器所接收到的声波包括直达波、反射波、滑行波和沿仪器外壳传播的声波,声波测井的探测范围一般是指井壁滑行波的影响范围[1]。

声波测井是应用较广泛的现代测井方法之一。其采用声波的速度、幅度在岩石、岩层孔隙、含油气水等介质中传播时的全波记录得出的不同物理地质特征来研究和解决地质问题,进而发现油气、煤、金属与非金属、放射性、地热、地下水等矿产资源。

一般常用的声波测井方法可以分为声波速度测井。声波幅度测井和声波全波列测井。这里使用的是声波幅度测井,声波幅度测井是研究岩层对声波幅度的衰减特性的测井方法[2]。井下信号通过电缆传输至井上后,如何对上传的信号进行及时、高速、准确的处理从而传输到上位机以得到测井曲线是至关重要的。

1 声幅测井概述

固井声幅测井也称水泥胶结测井。声幅测井的井下部分如图1所示。套管应与水泥胶结良好,套管外固结的水泥环完整,否则套管外有泥浆存在。套管与泥浆界面的声阻抗比套管与水泥环的大,就是说套管与泥浆的声耦合较差,套管与水泥环的声耦合较好。因此,套管与水泥胶结差时,套管波的能量不易通过管外泥浆传播,接收到的套管波幅度大,反之则到达接收器的套管波能量小。即在水泥胶结良好时,固井声幅测井值低;水泥胶结差时,固井声幅测井值高[3]。

2 系统硬件设计

图1 声幅测井原理图

井下上传的信号CBL(75 mV,20 kHz)经模数开关多路选择后,进入A/D采样,采样完成后数据进入FPGA进行高速处理,处理后的数据由USB模块上传至上位机。系统框图如图2所示。

图2 系统框图

2.1 模数开关设计

模数开关使用AD7502芯片。AD7502是一款单芯片CMOS双路4通道模拟多路复用器。它根据2个二进制地址输入A0,A1和一个使能输入的状态EN,将2路输出总线 OUT1-4,OUT5-8,切换至8路输入S1,S2,S3,S4,S5,S6,S7,S8中的 2 路S1&S5,S2&S6,S3&S7,S4&S8。通过对模数开关的控制可以选择 A/D采集的是CBL信号或AC信号。

2.2 A/D采集模块

数据采集使用AD1671芯片,AD1671芯片为12位1.25 Msample·s-1,转换时间为800 ns的芯片。

2.3 FPGA主电路模块

数据处理及存储使用EP1C6芯片,cyclone EP1C6是Altera推出的一款高性价比FPGA,工作电压3.3 V,内核电压1.5 V。采用0.13 μm工艺技术,全铜SRAM工艺,其密度为5 980个逻辑单元,包含20个128×36位的RAM块,总的RAM空间达到20×(128×36)=92 160位。而本设计的采样周期为2 ms,采样间隔为1 μs,每次需存储16位,共需存储2 000×16=32 000位,可以满足设计要求。内嵌2个锁相环电路和一个用于连接SDRAM的特定双数据率接口,工作频率高达200 MHz。

2.4 USB数据传输模块

USB传输使用CH375芯片。CH375是一个USB总线的通用接口芯片,支持USB-HOST主机方式和USB-DEVICE/SLAVE设备方式。这里采用设备方式。

2.5 电源模块

由于FPGA正常工作时要求先给I/O口供电再给内核供电,断电时要求先给内核断电再给I/O口断电,为保证严格的上电顺序,系统使用AS2830-3.3 V可将电压由5 V转换到3.3 V,使用 AS2830-1.5 V可将电压由5 V转换成1.5 V,IA0505S为稳压正负双输出电源模块,可将电压由5 V转换成-5 V,这样就可以满足各部分工作需求[4]。

3 系统软件设计

设计的数据采集系统是基于高性能FPGA芯片实现的,FPGA承担了绝大部分的控制和数据处理任务,是设计的核心内容,对FPGA进行模块化设计,是大型系统设计的常用方法[5-6]。本项目中将 FPGA分成USB控制模块、采样控制模块、触发脉冲产生模块和RAM等几个主要功能模块来设计。

FPGA模块的原理如图3所示。其工作原理为触发脉冲产生模块,根据设定的参数周期性输出脉冲信号触发采样控制模块对A/D进行采样。采样控制模块在接收到USB控制模块的启动信号后,只要接收到触发信号就开始采样数据,并判断采样数据是否满足要求,如果满足要求则把数据存放于RAM中,且在采样结束后触发USB控制模块上传数据。

图3 USB采样机FPGA模块的原理框图

通电后,先对USB芯片初始化,然后如果接收到采样结束信号或上传结束信号并且RAM在还剩余有数据的条件下把RAM数据上传,若接收到下传信号,则把计算机下传的数据按要求分配到各端口。

3.1 采样控制模块

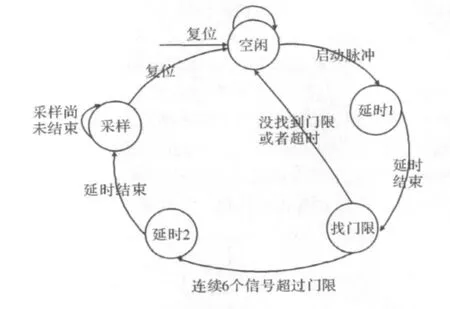

采样控制模块根据外部触发信号,利用状态机对A/D的采样行为进行控制。共有5个状态,每个状态的动作在代码中进行了详细描述。

第1个状态:空闲状态(IDLE),表示程序无任何操作,在等待外部触发信号的到来。

第2个状态:延时1(第一个等待状态,WAIT1),表示收到触发信号后需要禁闭A/D一段预先设定的时间,这段时间不进行任何操作。

第3个状态:找门限(门限判决状态,THDET),在规定的时间段时间里判断A/D采样的信号中是否有连续6个采样大于门限的值,如果有,等待一段时间后把采样后的数据存入缓冲区以便上传给上位机。否则继续等待下一个触发信号。

第4个状态:延时2(第二个等待状态,WAIT2),表示已经满足采样要求后再禁闭A/D一段预先设定的时间,这段时间不进行任何操作。然后启动A/D进行采样。

第5个状态:采样状态(SAMPER),启动A/D进行采样,并存储数据。

此处为米莉(Mealy)型状态机,Mealy型状态机的输出不仅与现态有关,而且和输入也有关。

该状态机采取3段式描述方式:即使用3个always块,第1个always块采用同步时序描述状态转移;第2个always块采用组合逻辑判断状态转移条件,描述状态转移规律;第3个always块描述状态输出[7-9]。

图4 采样控制模块的状态转移图

状态机的编码使用独热码(One-hot)编码,独热码编码的最大优势在于状态比较时仅需要比较一个位,从而一定程度上简化了比较逻辑,减少了毛刺产生的概率。

3.2 USB控制模块

USB控制模块对USB接口进行控制,包括初始化USB、USB中断处理、上传数据、下传数据。这里一共有5个状态,每个状态的动作在代码中进行了详细描述。状态机所有的动作如下:

第1个状态:初始化状态(init),对USB芯片进行初始化。

第2个状态:空闲状态(idle),表示程序无任何操作,在等待外部的触发信号的到来。

第3个状态:上传状态(upload),把储存器中的数据上传给上位机,每次上传64 Byte。

第4个状态:下传状态(dwonload),上位机的数据通过USB下传,并根据命令字把数据分配到不同的寄存器。

第5个状态:中断处理状态(intStatus),对USB的中继信号进行处理,并根据不同的中断状态字把状态机切换到不同的状态。

图5 USB控制模块的状态转移图

本模块的状态机类型为Mealy型状态机、描述方式为3段式描述方式、编码方式为独热码编码,这些与采样控制模块中使用的状态机相同。

4 水泥胶结质量的解释

固井声幅测井曲线如图6所示,当以“自由套管”处的偏转幅度为A,凡固井声幅曲线的幅度<20%A者为固井质量良好;曲线幅度为20%A~40%A,固井质量中等;凡曲线幅度>40%A,为固井质量差的井段,即存在水泥串槽混浆[3]。

图6 固井声幅测井曲线示例

5 结束语

系统是一种基于FPGA的高速数据采集系统,其中包括高速数据采集、存储和传输。整个系统是基于FPGA实现的,具有其它元器件不可比拟的优点。文中给出了基于FPGA的声幅测井系统的设计,包括硬件和软件的设计,讨论了高速数据采集系统中FPGA的模块化设计。实现了将两种不同的声幅信号实时高速采集,快速稳步存储传输给上位机,同时将仪器所需要的控制命令由主机下发,通过USB传输至FPGA再至各接口。实际测试表明:该系统不仅缩短了信号传输时间,而且操作极为简便。使用该系统满足了信号传输的实时性要求,提高了工作效率。

[1]楚泽涵.声波测井原理[M].北京:石油工业出版社,1985.

[2]吴国庆,牛欢,王俊英,等.声波测井技术的理论研究[J].消费导刊:科教论坛,2009(1):198.

[3]孟予萍,郭祥云.煤层气固井声幅测井方法探讨[J].中国煤炭地质,2008,20(12):12 -13.

[4]潘松,黄继业.EDA技术实用教程[M].北京:北京科学出版社,2002.

[5]邱畅,李龙.采用FPGA的双通道500MHz的数据采集卡[J].国外电子测量技术,2008(11):32 -34.

[6]诸振勇,翁木云.FPGA设计及应用[M].西安:西安电子科技大学出版社,2002.

[7]袁俊泉,孙敏琪,曹瑞.Verilog HDL数字系统设计及应用[M].西安:西安电子科技大学出版社,2002.

[8]徐振林.Verilog HDL硬件描述语言[M].北京:机械工业出版社,2000.

[9]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008.

[10]姚国国,李宝森,王景贤.基于SOPC技术的数据采集系统设计[J].电子科技,2008,21(10):71 -74.