基于TS201芯片的雷达信号处理机设计

陈新峰, 张军杰, 赵 非, 王晓东

(1.中国电子科技集团公司 第二十七研究所,河南 郑州450005;2.中国人民解放军防空兵指挥学院 河南 郑州 450052)

现代雷达广泛了应用了数字信号处理技术,主要实现时频信号处理。随着大带宽高分辨率、多种信号处理方式的采用,雷达信号处理不仅流程复杂,运算量大,数据吞吐率也急剧上升,而且对处理数据的精度要求也越来越高,这就要求雷达数字信号处理系统能够高速实时、高通过率地完成各种处理任务。本文讨论的是由高速DSP芯片ADSP-TS201构成的雷达信号处理机,ADSP-TS201数字信号处理器作为雷达信号处理机的核心完成雷达信号处理的大部分功能。本系统在设计时比较好地发挥了高速DSP芯片ADSP-TS201的良好性能;通过灵活的配置,合理地解决了高速数据率的问题,实现了雷达信号处理的各种算法;充分地利用了芯片内部资源;降低了系统设备的复杂性,又保证了系统性能。

1 ADSP-TS201简介

以超大规模处理器技术为基础的数字信号处理器近年来发展迅速,其强大的处理能力和可编程能力,满足了雷达数字信号处理系统实时性和通用性的要求。ADSP-TS201芯片是ADI公司推出的一款高性能浮点数字信号处理器,采用超级哈佛结构,静态超标量操作适合多处理器模式运算,其主要性能如下[1-2]:

1)最高主频可达 600 MHz,指令周期为 1.67 ns,支持单指令多数据 (SIMD)操作,达到每秒48亿次乘加运算(4.8 GMACs/s)和每秒 36亿次浮点运算(3.6 GFLOPS)。

2)支持IEEE32位、40位浮点数据格式和8位、16位、32位和64位定点数据格式。

3)内部集成24 Mbits DRAM,分为6个 4 Mbits的DRAM块,特别适合大数据量信号处理应用。

4)内部4条128位宽总线通过交叉点开关与6个DRAM块连接,可以将程序、数据和输入、输出缓冲区分配在不同的RAM块中,使得在一个时钟周期内可以同时进行指令、数据和I/O访问,带宽可以达到33.6 GB/s。

5)32位的地址总线提供4 G的统一寻址空间。

6)片内集成4个收发全双工链路口(每个链路口可提供1.2 GB/s的传输速率,可同时进行DMA传输),可以方便地进行芯片互连。

2 信号处理机硬件结构

对雷达信号处理机的硬件设计要求通常包括:适于实时信号处理,结构灵活,有较强的通用性,适于模块化设计,开发周期短,系统已于维护和扩展。由于各方面约束有时是互斥的,即要尽量降低硬件的复杂程度,提高系统的可靠性,又要尽量满足实时处理的要求,减轻软件部分的负担,兼顾系统的可重构性能,提高系统的可扩展性。

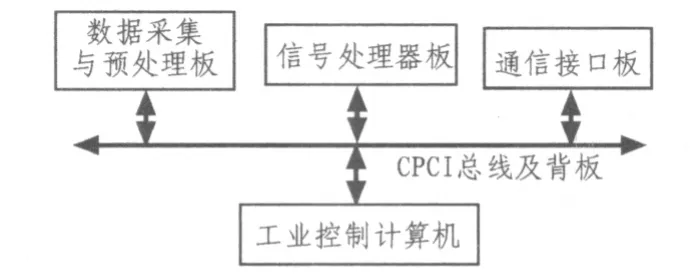

近年来,CPCI总线以其高带宽、可靠性高和兼容性好在工业控制及军工领域内得到广泛的应用。设计的雷达信号处理机采用6U的CPCI板卡结构尺寸,具有结构紧凑美观、印制板不易变形、集成度和可靠性高的优点。雷达信号处理机从硬件结构上主要分为3部分:数据采集与预处理板,信号处理器板,通信接口板,3块电路板放在一个标准6U的CPCI机箱内,电路板之间的信号线通过底面的扣板连接,调试时利用工业控制计算机通过CPCI接口来访问。系统总的硬件组成如图1所示。

图1 系统硬件框图Fig.1 System hardware structure framework

2.1 数据采集与预处理板

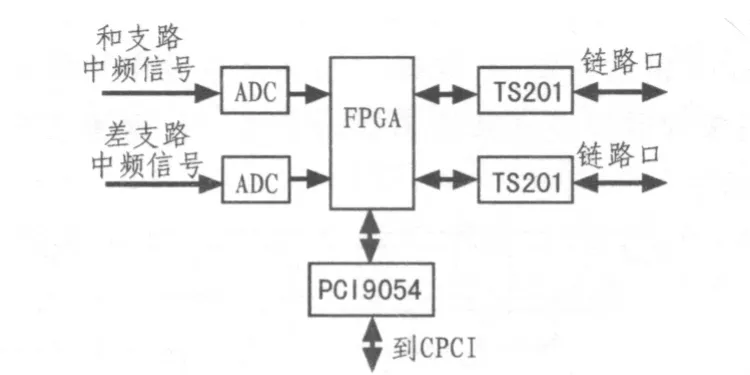

数据采集与预处理板用来对中频模拟信号进行采样,并完成数字信号的正交解调、定点到浮点转换以及与雷达系统的时序调度。数据采集与预处理板构成如图2所示:两路AD实现对雷达和差两路中频信号的数字采样,一片FPGA完成对数字信号的正交解调,两片TS201完成雷达回波数据的定点到浮点转换与雷达系统的时序调度,一片PCI9054(CPCI总线结构芯片),通过CPCI与主机通信。

图2 数据采集与预处理板框图Fig.2 Data sampling and pre-processing framework

2.2 信号处理器板

信号处理器板完成雷达回波信号的脉冲压缩、MTD、跟踪和测角、测距、测速等功能[3]。信号处理器板构成如图3所示。

在一个标准的6UCPCI板上集成了ADI公司的8个600MHz TS201S处理器,可提供28.8 GFLOPS峰值计算能力。系统总线采用66 MHz,64 bit 6U CPCI总线。8个TS201S处理器不共享总线,采用分布内存体系结构。每个处理器的64位总线无缝连接 4片 32 M×16位 SDRAM (MT48LC32M16),4片SDRAM配置成32 M×64位,共256 MB。CPCI主机和DSP均可访问SDRAM。DSP访问SDRAM的峰值速率为800 Mb/s。PCI访问SDRAM的速度峰值速率为240 Mb/s。8个处理器提供强大的I/O接口,其64位总线直接连到对应的FPGA。FPGA采用Altera的 STRATIX系列 “EP2S30”,300万门,672个I/O引脚。主机通过CPCI总线可实现对8片DSP的程序加载与通讯。理论峰值速率可达240 MB/s[4]。信号处理器板上的8片TS201通过链路口进行互联,其链路口连接方式拓扑结构如图4所示,这种拓扑结构可以形成多种芯片互连方式,如图5所示,这种设计很方便地进行雷达信号处理软件流程设计,而且有利于雷达信号处理算法的扩展。

图3 信号处理器板框图Fig.3 Signal process framework

图4 链路口连接图Fig.4 Link-port connection framework

图5 DSP芯片互连图Fig.5 DSP chip inter-connection framework

2.3 通信接口板

通信接口板主要是用来完成把雷达处理结果发送到主机端进行终端显示,同时与雷达的天线、发射、接收分系统通信。

3 信号处理机软件实现

雷达的工作体制为一维相扫、相位和差单脉冲、二相编码[5]。信号处理机由以下基本的功能单元组成:40 MHz高速A/D数据采集、数字正交解调器、数字脉冲压缩、MTD处理、CFAR信号检测、相位和差波束测角、目标跟踪、通信与控制等模块构成[6]。主要的数据流程为:和差两个支路的70 MHz中频信号经40 Mb/s的ADC采样,再经过数字正交解调和滤波抽取,得到10 Mb/s和差支路的I、Q数字信号,I、Q数字信号经过相位编码脉冲压缩后进行数据重排,然后对重排后的数据进行MTD、求模、恒虚警检测、测距、测角、测速、距离跟踪、角度跟踪等处理,处理后目标的的距离、速度、角度数据送数据处理与显示控制分机进行终端显示。

3.1 数字解调器

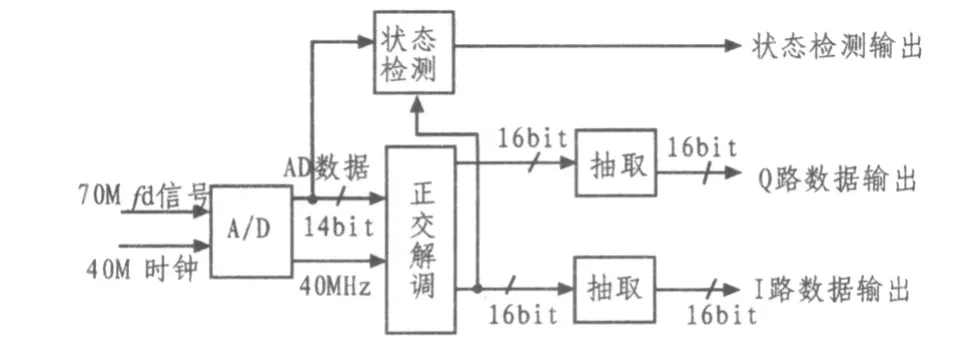

中频宽带数字解调器的主要任务就是完成对雷达接收的70 MHz中频和差两路模拟信号分别进行AD采样、数字正交解调、低通滤波、数据抽取,从而得到所需的零中频正交双路信号。解调器由A/D、正交数字解调电路、故障检测电路组成。中频宽带数字解调器就是对由于双路信号是经过数字处理所得到的,况且相干解调与低通滤波都是数字电路实现的,因此可以达到更高的精度与稳定性[7]。图6给出的是其中一路框图,另一路的流程基本相同。

图6 一路中频数字解调器框图Fig.6 IF demodulation framework

3.2 脉冲压缩

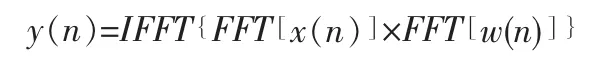

本雷达采用长短脉冲结合的波形方式,短脉冲用来测量近距离目标,宽脉冲用以测量远距离目标。短脉冲内由13位BK码相位编码调制,长脉冲用长度为511位的m序列相位编码调制[8]。在本系统中,脉冲压缩采用频域算法,即对输入的接收信号序列先进行FFT变换,将离散输入时间序列x(n)变换成数字谱,然后乘以匹配滤波器冲击响应w(n)的数字谱,对相乘后的结果进行逆FFT还原成脉冲压缩后的时间离散信号。其算式如下:

这种方法的优点是大时宽信号时可采用高速FFT算法,大大减少运算量,提高运算速度,实现大的压缩比[9]。本设计中针对TS201芯片内存量大的特点,将W(w)直接存入DSP内存,以W(w)所需内存换取了一次FFT运算时间。

3.3 MTD

MTD通过对目标回波信号的相参积累提高了SNR,使雷达在各种杂波背景下的目标检测能力提高,另外MTD还是抑制杂波的有效办法,由于DSP芯片具有高速FFT算法,因此通过FFT实现MTD,可以减少运算量。FFT实现MTD是通过舍去零号及其附近的几路滤波器来实现抑制杂波功能的,舍去滤波器的路数取决于杂波谱的宽度。FFT抑制杂波存在一个问题是其窄带滤波器的旁瓣很高,第一旁瓣只有-13 dB,因此普通FFT抑制杂波的改善因子不可能很高。提高FFT改善因子的方法有两种:一种是在FFT之前加一次对消,这种方法脉冲回波数需要比FFT点数多一个,并且需要在FFT之后给不同滤波器加权以改善一次对消幅频响应的不平坦性;另外一种是通过加窗处理降低FFT的旁瓣,如加海明窗第一旁瓣降为-42 dB,加布莱克曼窗第一旁瓣为-58 dB。加窗也有缺点,加窗会损失信号能量,加窗会使主瓣展宽,降低相参积累效率,但加窗使总的幅频响应曲线更平坦,一般FFT相邻窄带滤波器交界点为-3 dB,加布莱克曼窗后为-0.5 dB[10]。本设计中MTD模块采用128点FFT实现,通过加窗处理降低FFT的旁瓣,所以MTD模块运算数据量大,需要利用片外的SDRAM,主要实现难点是数据传输时间问题。由于MTD是对同一距离单元上的脉压数据进行处理,因此要求数据在DMA传输的过程中实现矩阵行列转置,128个脉冲周期的数据量已经远远超过了普通一维DMA传输方式的上限,且若在SDRAM中跳址传输,遭遇频繁的跨页寻址时会耗费更多的时间,采用二维DMA传输方式,通过改变TCB配置使DMA传输在SDRAM中连续寻址,而在DSP端接收地址自动跳变,在矩阵传输的同时实现行列转置,满足了系统的数据传输时间要求。

3.4 恒虚警处理

雷达工作在杂波环境中时,目标检测是在杂波背景中作出的。检测器门限设置与热噪声背景下的设置不同,必须自适用于杂波功率的变化,使杂波引起的目标检测即虚警保持在一个较低的可接受水平上,这种信号检测的方法称为恒虚警检测。

根据本雷达的要求,选择采用两侧单元平均恒虚警处理方式,用来抑制固定点杂波和地物杂波。恒虚警实现方法如图7所示。

图7 单元平均恒虚警框图Fig.7 CA-CFAR framework

4 结 论

本文以雷达信号处理机的设计为背景,利用ADI公司的新型DSP芯片ADSP-TS201的超高性能的处理能力和易于构造多处理机体系的特点,实现了雷达信号处理机,由于采用了模块化的设计,不仅研制周期短,可重构好,而且对雷达信号处理算法的适应性强。该雷达信号处理机已经成功地应用于实际工程中,实现了雷达信号实时高精度处理。

[1]冯小平,曹向海,鲍丹,TigreSHRC处理器技术其应用[M].西安:电子科技大学出版社,2010.

[2]刘书明,苏涛,罗军辉.TigerSHARC DSP应用系统设计[M].北京:电子工业出版社,2004.

[3]江铃,苏涛,程丽丽.基于通用信号处理板的LPI雷达的实时信号处理[J].火控雷达技术,2007(36):58-62.JIANG Ling,SU tao, CHENG Li-li.Real time signal processing of LPI radar based on general signal processing module [J].Fire Contrd Radar Techno logy,2007 (36):58-62.

[4]顾颖.用ADSP-TS201芯片架构的雷达数字信号处理机[J].雷达与对抗,2005(4):27-29.GU Ying.A radar digital signal processor constructed with ADSP-TS201[J].Radar& Ecm,2005(4):27-29.

[5]丁鹭飞,耿富录,陈建春.雷达原理[M].4版 北京:电子工业出版社,2009.

[6]吴顺君,梅晓春.雷达信号处理和数据处理技术[M].北京:电子工业出版社,2008.

[7]杨小牛.软件无线电原理与应用[M].北京:电子工业出版社,2001.

[8]Barton DK,南京电子技术研究所.雷达系统分析与建模[M].北京:电子工业出版社,2007.

[9]李欣,刘峰,龙腾.定点FFT在TS201上的高效实现[J].北京理工大学学报,2010(30):88-91.LI Xin ,LIU Feng,LONG Teng.Efficient implementation of fixed-point FFT on tS201 [J].Journd of Beijing In stitute of Techologg,2010(30): 88-91.

[10]程佩青.数字信号处理[M].北京:清华大学出版社,2007.