基于FPGA的WTB总线控制器设计

蒋国涛

(中国南车集团 株洲南车时代电气股份有限公司 技术中心 ,湖南株洲412001)

目前,国际上列车通信网络控制技术己经成熟。其核心技术由西门子、Bombardier和ABB等公司掌握,市场上的TCN专用控制芯片被它们所垄断。在国内还没有公司能够开发出符合IEC 61375要求的专用绞线式列车总线(WTB)的专用控制芯片。虽然有公司开发出了基于FPGA的WTB物理层控制器IP核,但是离成熟标准的绞线式列车总线(WTB)的专用控制芯片的距离还很遥远,其只能实现物理层信号编解码、信号监测、线路选择及冗余管理等物理层功能,如果要实现WTB通信,还需要借助外界器件实现高层数据链路控制器(HDLC)协议,通用性差。

介绍一种基于FPGA平台的能完全满足IEC 61375绞线式列车总线(WTB)的专用控制芯片功能要求的标准IP核。它能完成绞线式列车总线(WTB)链路层的HDLC帧收发、物理层数据的曼彻斯特编解码、冗余线路的控制等功能。该IP核可以流片成专用的ASIC,也可以作为通用的IP核直接使用,解决了目前该类产品通用性差、重复开发等问题,突破了国外公司的技术垄断,在行业内具有战略意义。

1 WTB帧

绞线式列车总线(WTB)是一种串行数据通信总线,主要用于经常相互连挂和解列的重联车辆。WTB满足IEC 61375-1[1]的要求,支持周期性的过程数据、非周期性的消息数据以及监视数据。能够通过初运行实现列车的自动编址、自动编组。WTB最多可互联32个节点,传输介质为屏蔽双绞线,干线电缆最大长度为860 m,工作速率为1 Mb/s。WTB采用了硬件冗余,数据在两条介质上同时发送,仲裁逻辑根据收发器提供的载波检测信号在两路接收信号间作出选择。

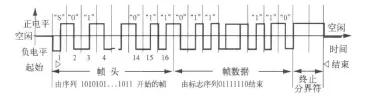

IEC 61375[1]标准规定WTB帧一帧信号由前导码(帧头)开始,接着是帧数据,最后由终止分界符结束。前导码由电平为“1”的起始位S开始,随后是若干个(0,1)位对(本设计中采用了7对),最后以1结束。帧数据的开始和结束由标志序列01111110进行标志。终止分界符为2.0 BT(1 BT=1个时间单位)宽的正电平,见图1所示。

图1 线路上的WTB帧

WTB所有的帧都具有同样的格式,遵循 HDLC(ISO/IEC 3309[2])规范,见图2所示。

图2 HDLC数据格式

Preamble前同步码:WTB帧开始部分的前同步码由曼彻斯特编码器产生,并由曼彻斯特译码器去除。它不属于HDLC帧部分。它的长度为16到32位,16位是默认值,主要用于WTB帧位同步。

(1)Flag帧头标志位。HDLC帧以两个8位标志(01111110)作为分界符,作为帧同步标志。

(2)DD目的设备。接收该帧节点的 Node_Address(节点地址)(或者是广播地址)。

(3)LC链路控制字段。用于链路控制的 8位字段,标志帧类型等。

(4)SD源设备。发送帧的节点地址。

(5)SIZE。标志以字节为单位的链路数据的长度。

(6)FCS帧校验序列。16位的帧校验序列。由曼彻斯特编码器产生,由译码器去除。

(7)ED结束分界符。End_Delimiter(结束分界符)由曼彻斯特编码器产生,由译码器去除。

2 WTB总线控制器构架

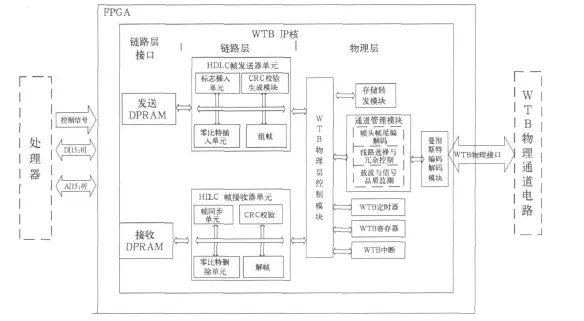

WTB总线控制芯片IP核的整个构架框图见图3所示。从通信协议分层的角度考虑,该IP核可以分为3个大的部分:物理层、链路层、链路层接口。

(1)链路层接口。链路层接口主要提供与外部处理器的接口,为发送数据和接收数据提供缓存空间,作为WTB总线控制芯片IP核与其他处理器件的数据传输通道。主要包含两个模块:发送双口RAM和接收双口RAM。

(2)链路层。链路层是该WTB总线控制芯片IP核的关键核心部分,主要实现HDLC协议。主要包含两个模块:HDLC帧发送器单元和HDLC帧接收器单元。

(3)物理层。物理层主要实现WTB物理通道控制、曼彻斯特编解码、定时、中断、FIFO转发。主要包括WTB物理层控制模块、通道管理模块、曼彻斯特编解码模块、WTB定时、WTB中断、WTB寄存器、存储转发。

图3 WTB总线控制器系统框图

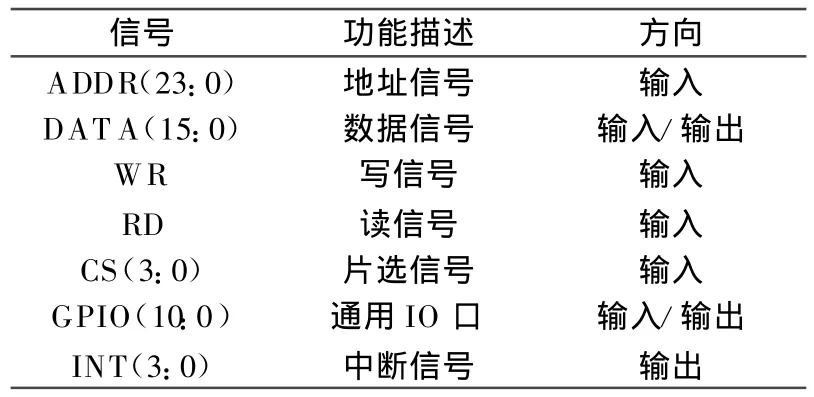

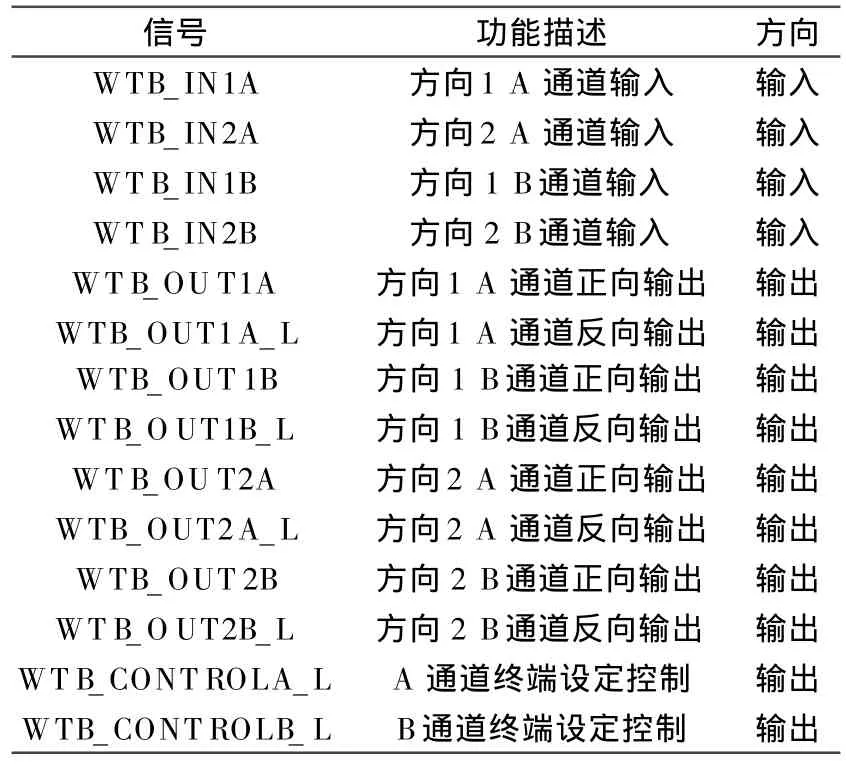

3 链路层接口设计(表1)

WTB总线控制芯片IP核功能主要是完成WTB通信控制,其接收的数据和需要发送的数据都是与外界处理器件相关。该链路层接口主要提供与外部处理器的接口,为发送数据和接收数据提供缓存空间,分别用FPGA内部双口RAM实现。

表1 链路层接口

4 链路层设计

WTB总线控制器链路层从功能上分可以分为HDLC帧发送器单元[3]和HDLC帧接收器单元[3]。链路层模块图见图4所示。

4.1 HDLC帧发送器单元

HDLC帧发送器主要实现对 HDLC帧数据生成CRC校验码、完成HDLC数据部分的零比特填充、构建HDLC帧的标志符(01111110)、对待发送的信息进行组帧发送控制,帧发送器内部电路结构见图5所示。

图5 HDLC帧发送器内部电路结构

HDLC帧发送器首先将来自应用层的有效数据存储到内部双口RAM即发送缓存中,然后将有效数据一路送给CRC校验模块生成校验码,另一路送给发送模块进行插入帧起始和终止标志符01111110的插入以及0的插入,然后组成HDLC帧送给曼彻斯特编码模块对帧数据进行曼彻斯特编码后输出到物理链路上。当在发送过程中,出现发送失败,产生发送失败中断。

(1)CRC-16校验生成

采用CRC-16校验,产生16位的CRC校验码,数据发送和接收都是采用相同的CRC校验,其生成多项式为g(x)=x16+x12+x5+1。为了提高IP核性能和处理速度,该发明采用并行CRC代替传统的串行CRC。

(2)构建 HDLC帧的标志符(HDLC帧头和HDLC帧尾)

根据ISO 3309中定义的HDLC格式,一帧数据由标志符01111110开始,同时由相同的标志符结束。该IP核在发送数据帧前先插入标志符发送,当帧数据发送完毕后再插入相同的标志符标志帧数据发送完毕。

(3)零比特填充

为防止数据位中出现与标志符0111110相同的数据,所以对数据扫描,在5个1后插入一个0,到了接收端再剔除填充零比特恢复链路数据。例如待发送的数据为011101111110,发送的数据则为0111011111010。

(4)发送状态控制模块

HDLC帧发送器采用状态机实现整个控制,控制帧发送器依次完成帧头发送、生成CRC校验码、零比特填充、数据发送、帧尾发送。其流程图如6所示。

图6 发送状态控制模块状态机

4.2 HDLC帧接收器单元

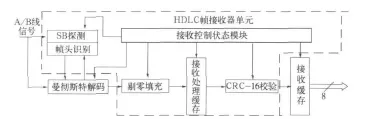

HDLC帧接收器主要实现检测帧开始信号(Start_Bit)、识别帧起始符和结束符、完成CRC校验、剔除HDLC帧的填充零比特、帧接收时序控制。

HDLC帧接收器的电路结构如图7所示,由HDLC帧头识别模块、剔除填充零比特模块、CRC校验模块、接收控制状态模块组成。

图7 HDLC帧接收器内部电路结构图

HDLC帧接收器单元第一次检测到标志符01111110时表示帧数据开始,对帧数据进行同步,接收帧数据;在接收帧数据的过程中,对接收到0111110 5个1后面的0进行剔除操作;在接收数据的同时,对接收的数据进行CRC-16校验;当再次检测到标志符01111110时表示帧数据发送完毕;如果在接收过程中发生错误或接收无效帧产生接收失败中断。

(1)帧头识别

检测Start_Bit,启动解码器工作,同时判断帧头是否为正确的序列。

(2)剔零填充

扫描串行数据,剔除5个1后的0,采用序列检测状态机实现。

(3)CRC-16校验

HDLC帧接收器单元CRC校验原理同CRC校验码的生成相同。将数据输入移位寄存器再生成CRC码,同接收到的CRC码比较,如果不一致,产生CRC错误指示。

(4)接收状态控制模块

HDLC帧接收器单元帧接收时序控制模块采用状态机实现,控制帧接收器依次完成帧头的识别,码元同步,数据的解码,剔除填充零比特和帧校验,最后送至发送缓存,通知上层,同时报告相关的错误信息。其流程图如8所示

图8 接收状态控制模块状态机

5 物理层设计

物理层主要实现WTB物理通道控制、曼彻斯特编解码、定时、中断、信号再生。主要包括曼彻斯特编解码模块、通道管理模块、WTB定时、WTB中断、WTB寄存器、存储转发、WTB物理层控制模块。物理层模块图见图9所示。

(1)曼彻斯特编解码模块

根据IEC 61375规定WTB通信传输的是曼彻斯特信号,曼彻斯特编解码模块的目的就是实现NRZ信号与曼彻斯特的转换。

曼彻斯特编解码模块主要功能按照信号方向分为曼彻斯特编码和曼彻斯特解码。

曼彻斯特编码把链路层HDLC帧的NRZ信号与1M时钟信号作异或逻辑后,用D触发器锁存输出曼彻斯特码。采用16 M b/s时钟采样WTB传输线上的曼彻斯特码,同时作同步校正,判断跳沿类型译出是1还是0,作为NRZ信号传输给链路层。

(2)通道管理模块

通道管理模块主要实现WTB帧的帧头帧尾编码和识别、信号监测、线路选择。

根据IEC 61375规定WTB帧头是由起始位‘1'和结束位‘1'及夹在中间的 7~15对(‘0'‘1')对(默认为7对)组成;帧尾是一个2个位宽的高脉冲和2个位宽的低脉冲(低脉冲可选)组成。发送通道在发送帧数据前根据链路控制层信号先插入WTB帧头发送,等数据发送完毕后再插入帧尾发送;接收通道通过监测到帧头和帧尾对数据进行同步。

图9 物理层模块图

根据IEC 61375规定信号品质监视主要用于信号质量监测和冗余切换。产生载波检测信号(CS)和信号品质错误信号(SQE)反馈给上层,用于判断帧是否有效,依据线路上的有效帧和无效帧来对线路进行选择。

(3)WTB定时器、中断、寄存器

从用户使用角度考虑,该WTB总线控制芯片IP核中设置了多个参数寄存器,根据用户的需求对寄存器参数进行相应设置实现相应的功能。在WTB总线控制芯片IP核中设置了延时定时器、线路监测定时器等多个定时器用于监测网络运行。信号接收完成、信号发送完成、定时器、MAU报告等通过中断及中断状态寄存器反馈给用户。

(4)存储转发

随着列车总线长度的增加,列车通信必须面对信号衰解所引起的问题。针对该问题,该WTB总线控制芯片IP核采用存储转发功能块实现信号的再生与放大,延长了信号的传输距离,起到一个中继器的作用。该存储转发功能块根据上层控制信号和输入信号质量对信号采样存储转发。根据用户需要,可以设置该功能是否有效。

(5)WTB物理层控制模块

WTB物理层控制模块是HDLC链路层和物理层之间的接口;主要用来协调物理层各模块配合工作,传递上层的指示信号和反映物理层状态。

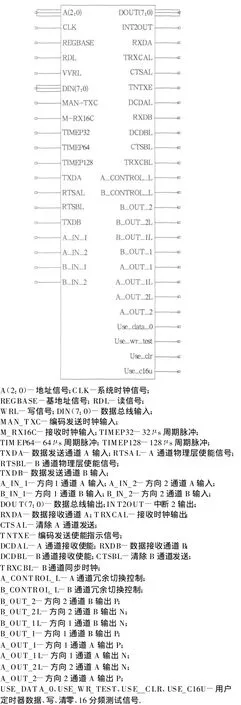

(6)接口说明(见表2)

6 结束语

针对WTB总线控制器,现有的技术一般都是采用FPGA来实现物理层的曼彻斯特编解码以及冗余线路的控制等功能,对于链路层的帧收发采用HDLC专业收发芯片来实现,该方案通用性差,随着8位HDLC收发芯片的退市,这种方案几乎无计可施。而本设计就完全脱离这种思路,从WTB总线控制器的全局着手,开发出通用的WTB总线控制器,在满足物理层的各项功能的基础上能实现链路层的帧收发功能。通用性能好,不受专用的 HDLC收发芯片的限制,便于开发各种WTB的功能设备。该WTB总线控制器IP核已经得到广泛应用,批量装车于上海地铁、出口伊朗的TM3电力机车、7 200 kW大功率电力机车等,通过了时间和运行里程的考核,得到了验证,各项功能及可靠性指标都已达标。

表2 WTB物理接口

[1] IEC 61375.Part 1:Train Communication Networks[S].

[2] ISO/IEC 3309-1993信息技术.系统之间电信与信息交换-高级数据链路控制规程-框架结构[S].

[3] 应三丛,张 行.基于FPGA的 HDLC协议控制器[J].四川大学学报,2008,40(3):116-120.