基于DSP Builder的伪随机序列发生器设计及FPGA实现

杨 东,王建业

(空军工程大学 导弹学院,陕西 三原 713800)

基于DSP Builder的伪随机序列发生器设计及FPGA实现

杨 东,王建业

(空军工程大学 导弹学院,陕西 三原 713800)

简要分析了伪随机序列中应用广泛的m序列,Gold序列及平衡Gold码的概念、原理和应用。提出了一种基于Altera的DSP Builder工具箱的伪随机序列产生器设计方法,并通过设计实例,说明这种方法在简化设计难度、提高设计速度和灵活性等方面的优点和应用价值。并提出了其仿真和FPGA实现的基本方法。

DSP Builder;m序列;Gold序列;平衡 Gold码

在扩展频谱通信系统中,伪随机序列起着十分关键的作用。在直接序列扩频系统的发射端,伪随机序列扩展信息序列的频谱,在接收端,伪随机序列将扩频信号恢复为窄带信号,进而完成信息的接收。因此,伪随机序列产生器是扩频系统的核心单元。伪随机序列具有理想随机序列的性质,易于产生,具有随机性和尽可能长的周期,使第三方难以从扩频码的一小段去重建整个码序列,具有双值自相关特性等。理想随机序列在工程上无法应用,实际上所用的均为伪随机序列。伪随机序列主要有:m序列、Gold序列、R-S码、复合码以及混沌序列等。

1 m序列基本原理

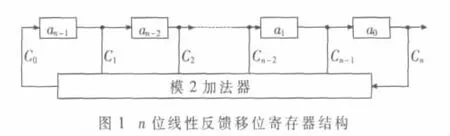

m序列又称最长线性反馈移位寄存器序列,它具有平衡性、移位可加性、游程特性及很好的相关性能,广泛应用于直接序列扩频系统。一个典型的m序列组成如图1所示。

由反馈移位寄存器产生的序列,取决于反馈系数,对于此反馈移位寄存器,反馈逻辑为:

上式即为序列的特征多项式。(cn,cn-1,…,c0)为反馈系数,其取值为“0”或“1”,“1”表示该反馈支路连通,“0”表示该反馈支路断开。m序列的反馈系数与其寄存器级数对应关系可由查表获得,据此,便可以构造任意级m序列。

2 Gold序列基本原理

扩频通信中,不仅要求伪随机序列具有随机性好、周期长、不易被敌方检测等特性,而且要求有尽可能多的可用的伪随机序列,以便进行多址通信和组网运用。Gold序列便具有此特性。GOLD R指出:“给定移位寄存器级数为n时,总可以找到一对互相关函数值最小的码序列,采用移位相加的方法构成新码,其互相关旁瓣都很小,并且自相关函数和互相关函数都是有界的”。这一对互相关函数最小的序列称为m序列优选对,是指在m序列集中,其互相关函数最大值的绝对值小于某个值的两个m序列。设序列{a}是对应于n阶本原多项式 f(x)产生的 m序列,序列{b}对应于 n阶本原多项式 g(x)产生的 m序列,当它们的互相关函数值 Rab(τ)满足不等式(2):

则由f(x)和 g(x)产生的m序列{a}和{b}构成一优选对。m序列优选对可由查表获得。

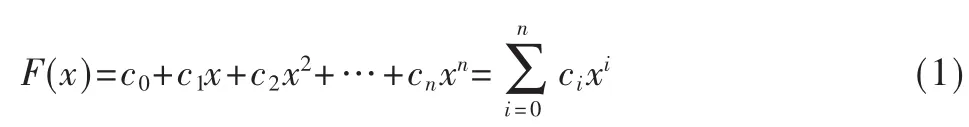

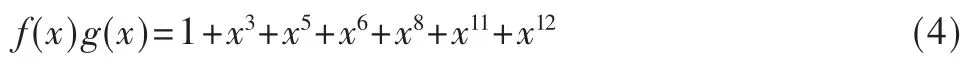

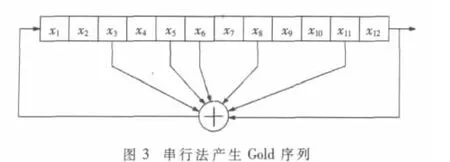

Gold序列的产生方式有并行和串行两种方式。由两个码长相等、码时钟速率相同的m序列优选对模2和构成Gold序列的方法为并行方式,每改变两个m序列相对位移就可得到一个新的Gold序列。将产生两优选对m序列的本原多项式相乘,展开后,按此多项式构成2n级Gold序列产生器的方法为串行方式。以n=6级Gold序列产生器为例,其优选对m序列的本原多项式为:

并行方式如图2所示。

由于:

可得串行方式如图3所示。

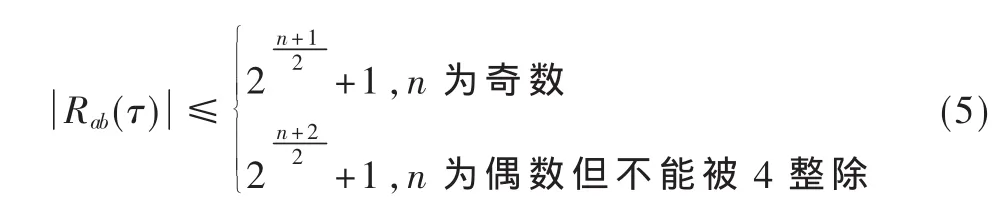

Gold序列族中任意两个Gold序列满足如下的互相关特性:

这一特性使得Gold序列中的任意码都可以作为地址码,因而大大增加了地址码的数量。

3 平衡Gold码

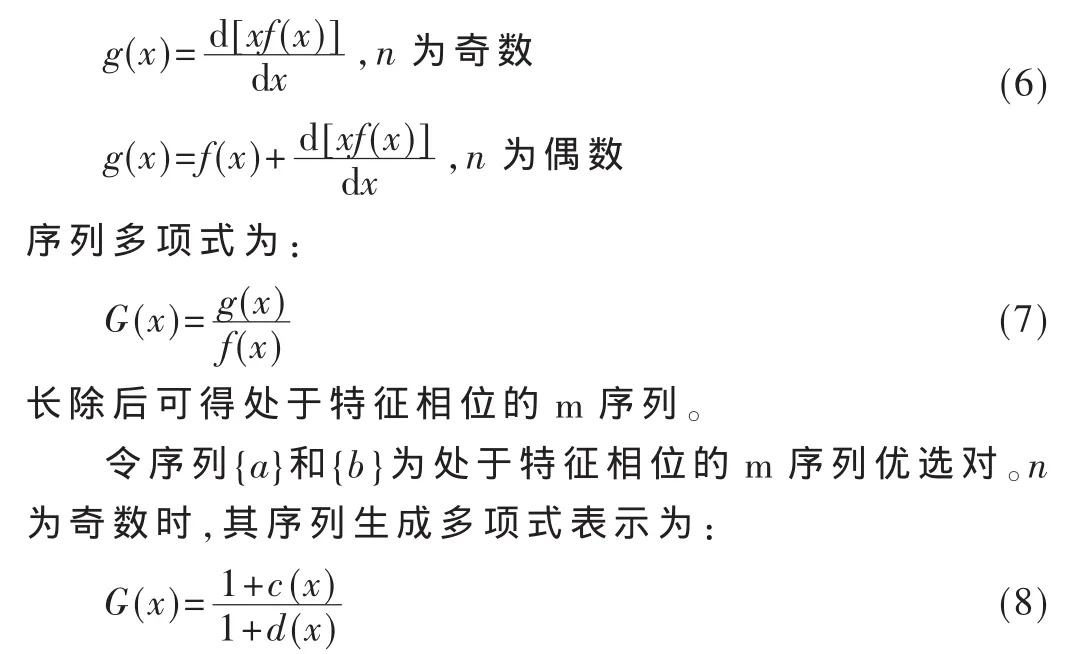

扩频通信系统中,对系统质量影响因素之一就是伪码的平衡性(即序列中的“0”、“1”均匀性),平衡码具有更好的频谱特性。在DS系统中,码的平衡性对载波抑制有密切的关系,码不平衡会造成载波泄漏,破坏扩频通信系统的保密性、降低其抗侦破能力。序列中“1”和“0”的码元数量相差等于1时为平衡码,而大于 1时为非平衡码。为寻找平衡Gold码,首先要确定特征相位,当序列处于特征相位时,序列每隔一位抽样后得到的序列与原序列完全一样。设序列特征多项式f(x)为n级线性移位寄存器产生m序列的本原多项式,序列的特征相位由g(x)/f(x)的比值确定。g(x)计算如下:

d(x)的阶数为 n,c(x)的阶数小于 n,长除后的结果为 1+d1x+d2x+…的形式。

因此,处于特征相位上的序列{a}和{b},以{a}序列为参考序列,移动{b}序列,使之第一位为“0”,对应于{a}序列第一位为“1”。两序列相加后得到的序列必定是平衡Gold码。那么,移动{b}序列的第一位为“0”的序列的前k位为相对相位。

产生平衡Gold码的一般步骤为:

(1)选一参考序列,其本原多项式为 fa(x),求出其生成多项式ga(x);

(2)由 G(x)=ga(x)/fa(x),求出序列多项式,使序列{a}处于特征相位上;

(3)求位移序列{b},使位移序列的初始状态的第一位为“0”,即处于相对相位,对应于序列{a}第一位“1”;

(4)将处于特征相位的序列{a}和处于相对相位的序列{b}模2加,就得到平衡Gold序列。

4 利用DSP Builder设计伪随机序列发生器

4.1 DSP Builder介绍

Matlab工具一般作为DSP算法的建模和基于纯数学的仿真,其数学模型无法为硬件DSP应用系统直接产生实用程序代码,仿真测试结果也仅仅是基于数学算法结构。而传统的FPGA基于硬件描述语言(HDL)的设计由于需要考虑FPGA的硬件延时、VHDL的递归算法的衔接、补码运算和乘积结果截取等问题,相当繁杂。DSP Builder是美国Altera公司推出的一个面向DSP开发的系统级工具,为Matlab的一个Simulink工具箱,以帮助设计者完成基于FPGA的DSP系统设计的整个流程,它充分体现了现代电子技术自动化开发的特点与优势。基于DSP Builder的设计流程如图4所示。

4.2 利用Simulink建立各序列模型

DSP Builder设计中首先是在Matlab/Simulink中进行设计输入,即在Matlab的Simulink环境建立一个MDL模型文件,用图形方式调用Simulink库中的模块,构成系统级或算法级设计框图(或称Simulink建模)。建立的m序列、Gold序列和平衡Gold序列产生器模型如图5所示。

图5中主要模块功能为:

(1)The Delay block:延迟模块,起延时作用,在硬件上可以采用寄存器来实现。此模块可接受任意类型的数据输入。

(2)The Logical Bit Operator block:位逻辑运算模块,能实现单个位输入数之间的逻辑运算,能实现多种功能:AND,NAND,OR,XOR,NOR,NOT。

(3)SignalCompiler:DSP Buider的核心,将 Simulink设计转换成可综合的RTL级VHDL代码,并产生各种测试和仿真矢量文件。

(4)The Testbench block:通过测试平台模块,可自动运行Modelsim,对比仿真结果。

5 各模型仿真及FPGA实现

5.1 Simulink模型系统级仿真

Simulink中进行的仿真属于系统验证性质的,是对mdl文件进行的仿真,而对VHDL代码进行仿真则需要使用ModelSim,如图6所示。

5.2 使用ModelSim进行RTL级仿真

ModelSim是一个基于单内核的Verilog/VHDL混合仿真器,是Mentor Graphic的子公司ModelTechnology的产品。主要用于对生成的RTL级VHDL代码进行功能仿真。 对应图 5中(b)、(d),经过 ModelSim功能仿真的波形如图7所示。

5.3 FPGA实现

在Matlab/Simulink中对设计模型进行编译,再用DSP Builder的Signal Compiler工具直接生成QuartusⅡ工程文件,再调用QuartusⅡ完成综合、网表生成和适配,直至完成FPGA的配置下载。本设计使用的FPGA芯片是Altera公司的Cyclone系列芯片EP2C35F672C6。

设计表明,在利用FPGA进行伪随机序列发生器设计时,利用DSP Builder能简化设计难度,加快设计速度,灵活选取精度,实现优化设计;DSPBuilder与QuartusⅡ软件的融合,实现了自顶向下的设计流程,充分显示了现代EDA开发的特点与优势。然而,该方法的应用在精度、速度和器件选择等方面也受到一定限制。

[1]何世彪,谭晓衡.扩频技术及其实现[M].西安:电子工业出版社,2006.

[2]潘松,黄继业,王国栋.现代 DSP技术[M].西安:西安电子科技大学出版社,2003.

[3]楮振勇,齐亮,田红心,等.FPGA设计及应用.西安电子科技大学出版社,2006.

[4]张洪润,张亚凡.FPGA/CPLD应用设计200例[M].北京:北京航空航天大学出版社.2007.

A DSP builder-based pseudo-random sequence and its FPGA implementation

Yang Dong,Wang Jianye

(The Missile Institute,Air Force Engineering University,Sanyuan 713800,China)

This text synopsisly analyzed the concept,principle and application of the m sequence,the Gold sequence and the equilibrium Gold code in the pseudo-random sequence.It put forward a designing way of pseudo-random sequence which based on the tool box of DSP builder in the Altera,and explained the advantages and values on simplifying the designing difficulty and advancing the designing speed and vivid through a solid example.It also put forward the basic method of imitating and carring out with FPGA.

DSP builder;m sequence;Gold sequence;equilibrium Gold code

TP331.1

A

1674-7720(2011)02-0096-04

2010-01-16)

杨东,男,1986年生,硕士研究生,主要研究方向:数字专用集成电路设计。