基于FPGA的915 MHz射频读卡器设计*

杨碧华,文张斌

(1.暨南大学 信息科学技术学院,广东 广州 510632;2.暨南大学 信息技术研究所,广东 广州 510075)

基于FPGA的915 MHz射频读卡器设计*

杨碧华1,文张斌2

(1.暨南大学 信息科学技术学院,广东 广州 510632;2.暨南大学 信息技术研究所,广东 广州 510075)

参照ISO/IEC 18000-6 Type B协议设计了一款工作频率为915 MHz的射频读卡器,采用FPGA完成协议中规定的数字信号处理,C8051F020单片机作为主控器。利用Verilog HDL硬件描述语言,搭建FPGA内部各个小模块及系统的验证平台,选用Altera公司Cyclone系列的EP1C6Q240C8芯片为目标器件,使用Quartus II进行综合,并通过时序和功能验证。实验结果表明,该读卡器符合ISO/IEC 18000-6 Type B 协议要求,具有结构灵活、体积小、升级容易等优点。

射频识别;读卡器;FPGA;C8051F020

射频识别(RFID)技术是一种非接触式的自动识别技术,通过射频信号自动识别目标对象并获取相关信息。通常RFID系统主要由应用软件、射频卡以及读卡器三部分构成[1]。相对于低频段的RFID系统,工作在860MHz~960 MHz的超高频段(UHF)RFID系统有着读取距离远、阅读速度快等优点,是目前国际上RFID技术发展的热点[2]。读卡器的设计是RFID系统设计中的关键部分,设计方案有很多种。FPGA[3]具有开发简单、静态可重复编程和动态在线编程的特点,已经成为当今应用最广泛的可编程专用集成电路。目前生产RFID产品的很多公司都使用自己的标准,可供射频卡使用的几种标准有ISO/IEC 11784、ISO/IEC 14443、ISO/IEC 15693 和 ISO/IEC 18000等。其中应用最多的是ISO/IEC 14443、ISO/IEC 15693和 ISO/IEC 18000这三个标准[4]。本文基于 ISO/IEC 18000-6 Type B协议设计了一款工作频率为915 MHz的读卡器。

1 读卡器的硬件设计

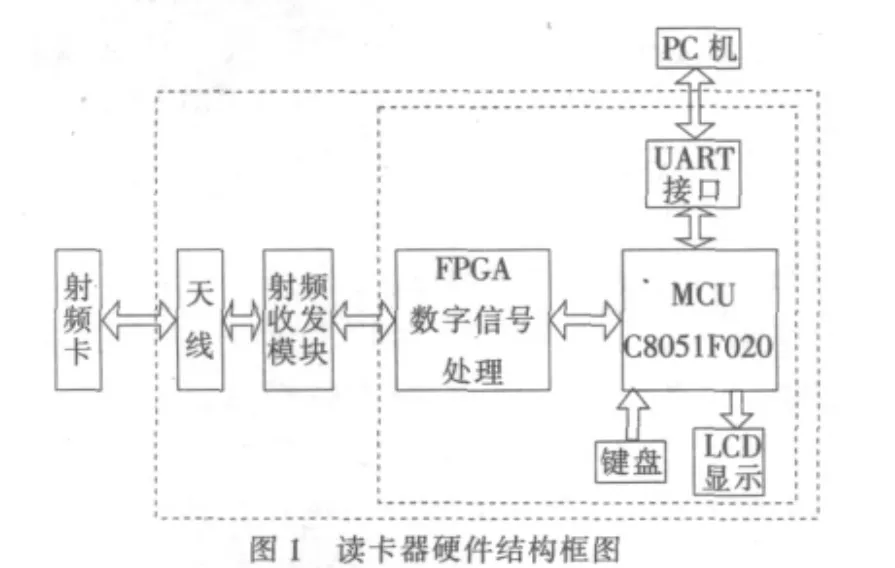

读卡器的硬件可以分为三大模块:FPGA数字信号处理模块、MCU及人机接口模块和射频收发模块,其结构框图如图1所示。FPGA数字信号处理模块用来实现ISO/IEC 18000-6 Type B 协议中规定的基带数据编解码,MCU及人机接口模块用来实现指令的跳转控制和返回数据的显示等一些操作接口,射频收发模块用来处理前端的超高频信号。

1.1 FPGA数字信号处理模块

FPGA数字信号处理模块包含时钟分频模块、FIFO、曼彻斯特编码器、CRC生成校验、FM0解码器、串并变换电路及对应的帧发送接收控制器,其结构框图如图2所示。

该模块的内部工作流程如下:

(1)发送部分

①数据通信接口8 bit并行接收来自MCU的命令数据,数据在FIFO中缓冲。

②数据做并行到串行的转换。

③在发送控制器的控制下,串行数据通过CRC模块,生成16 bit的CRC校验值,并附加在原数据的后面。

④根据ISO/IEC 18000-6 Type B协议规定,把上述的数据进行曼彻斯特编码。

⑤把已经过曼彻斯特编码的数据引向一个已预置帧头的移位寄存器,数据一到便启动移位寄存器,然后把输出数据传送给射频收发模块。

(2)接收部分

①从射频收发模块接收一帧基带信号,用移位寄存器来检测帧头。若检测到帧头,则发一个收到帧头的信号给接收控制器。

②若接收控制器接收到帧头的信号,则马上启动FM0解码。

③解码后的数据传送给串/并行的转换电路,转换后的数据暂存在FIFO。

④同时解码后的数据也送给CRC模块进行校验,若校验结果错误,则清除存于FIFO中的数据,通知MCU其接收的数据错误;若校验结果正确,则把FIFO中的数据传送给MCU。

1.2 MCU及人机接口模块

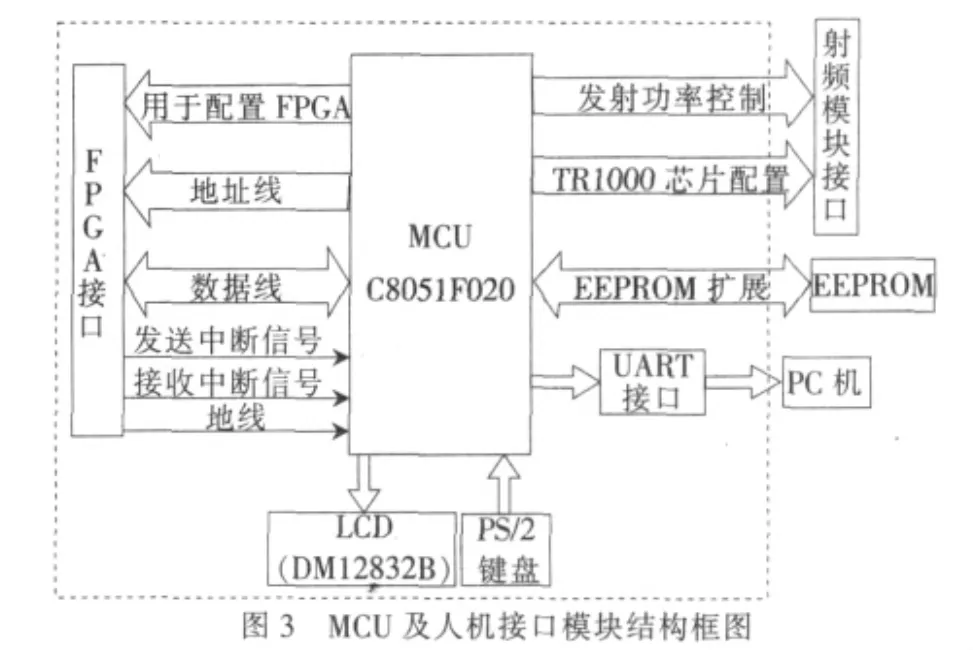

MCU及人机接口模块以C8051F020单片机[5]为核心,由 FPGA接口、LCD、PS/2键盘、UART接口以及JTAG接口等外围电路组成,其结构框图如图3所示。

该模块实现的功能有:(1)C8051F020负责整个读卡器内各部分的协调工作(包括与计算机的数据通信);(2)在启动时向FPGA传送配置数据,初始化FPGA;(3)在读卡过程中向FPGA传送读卡命令,然后通过INT1中断启动接收FPGA信号;(4)处理接收回来的射频卡信息(卡号、密码等);(5)实现二进制树形防碰撞功能;(6)驱动LCD,显示系统的提示信息;(7)扩展一个 PS/2键盘,可以输入数据及命令;(8)控制 TR1000芯片,设置 OOK发射方式或ASK接收方式;(9)控制发射功率大小;(10)扩展EEPROM,存储读出的射频卡的信息。

1.3 射频收发模块

超高频段射频收发模块的开发一般可以采用两种方案:一是采用分立元件搭建射频电路;二是采用无线射频收发模块以实现基带信号的调制解调[6]。由于第一种方法的电路调试比较麻烦,而且会占用很长的开发时间,所以本设计采取第二种方案。

ISO/IEC 18000-6 Type B 协议规定读卡器到射频卡端的射频调制方式为调制深度为99%的ASK调制,也就是可以近似看作为OOK调制;而射频卡到读卡器端的射频调制方式为反向散射调制,其调制方式与ASK调制类似,所以在解调端可以按照ASK方式解调。射频收发模块的核心芯片采用RFM公司的TR1000芯片。TR1000是一款单片OOK/ASK通用无线射频收发器芯片,适合高稳定、小尺寸、低功率、低价格的短距离无线数据通信和无线控制应用。

2 读卡器的软件系统设计

软件设计采用模块化和结构化的编程思想,在初始化的时候由单片机配置FPGA。考虑到C语言可读性强,移植性好以及MCU的实际情况,本设计采用C语言对C8051F020进行编程。读卡器的软件系统大致可以分为:读写卡操作程序、防冲突程序和串行通信程序。

2.1 读写卡操作程序

读写卡操作程序完成基于ISO/IEC 18000-6 Type B协议的基带信号编解码,其程序设计流程图如图4所示。

具体工作过程如下:(1)上电复位,系统初始化,包括单片机时钟、端口、LCD、定时器的初始化,配置FPGA和开中断。(2)等待接收上位机或键盘发送的指令。(3)对指令进行判断,如果为多卡操作,则进入防冲突子程序;如果为单卡操作,则直接进行读卡、写卡、值操作和中止操作。(4)若操作成功,所得数据回传给上位机,同时驱动LCD显示操作成功信息;若操作失败,则驱动LCD显示操作失败信息。

2.2 防冲突程序

当读卡器对射频卡进行多卡操作时,在其天线覆盖范围内的所有射频卡将被激活,并处于识别状态,造成了多张射频卡读写冲突。所以解决冲突是多卡操作的关键。ISO/IEC 18000-6 Type B协议详细规定了防冲突机制,其程序设计流程图如图5所示。该防冲突机制的原理是利用随机产生的0和1信号实现二进制树形搜索,并且设定了成功命令,进一步提高了搜索的效率,是一种二进制树形的防冲突算法[7]。具体实现过程为:首先,射频卡进入读卡器的工作范围,从离场掉电状态进入就绪状态。读卡器可以通过 GroupSeleet命令和GroupUnseleet命令让读卡器工作范围内处于就绪状态的所有或部分的射频卡参与防冲突过程。针对该模式的防冲突机制,射频卡应该具有如下两种硬件电路:一个8 bit的计数器和一个0、1随机数发生器。当射频卡进入识别状态(ID状态)后,将其内部的计数器清 0,其中的一部分可以通过接收GroupUnselect命令重新回到就绪状态,其他处于识别状态的射频卡则进入了防冲突执行的过程中。被选中的射频卡开始下面的循环:(1)所有处于识别状态并且内部计数器为0的射频卡将发送其识别码;(2)如果有一个以上的射频卡发送识别码时,读卡器将检测到冲突而发送Fail命令;(3)所有接收到Fail命令并且内部计数器不等于0的射频卡将把本身的计数器加1;所有接收到Fail命令并且内部计数器等于0的射频卡(即刚刚发送过应答的射频卡)将产生一个1或0的随机数。如果选择了1,射频卡将把自己的计数器加1;如果选择了0,射频卡将保持计数器为 0并且再次发送它们的识别码。在接下来的过程中会出现4种可能的情况;(4)情况1:如果有一个以上的射频卡发送,将重复步骤(2);(5)情况 2:如果所有的射频卡都随机选择了1,读卡器将接收不到应答,此时,读卡器将会发送Success命令,所有的射频卡的计数器减1,然后计数器等于 0的射频卡开始发送,接着重复步骤(2);(6)如果只有一个射频卡发送并且它的识别码被读卡器正确接收,读卡器将发送包含识别码的DataRead命令,射频卡正确接收该条命令后将进入数据交换状态,开始发送它的数据。此后,读卡器将发送Success命令,使处于识别状态的射频卡的计数器减 1;(7)情况 3:如果只有一个射频卡的计数器等于0并且返回应答,重复步骤(5)读卡器发Success命令或重复步骤(6)发送DataRead命令;如果有一个以上的射频卡返回应答,重复步骤(2);(8)情况4:如果只有一个射频卡返回应答,并且它的识别码未被正确接收,读卡器将发送一个Resend命令。如果识别码被正确接收,重复步骤(5)。如果识别码被重复几次的接收(这个次数可以基于系统所希望的错误处理标准来设定),就假定有一个以上的射频卡在响应,重复步骤(2)。

经过如上的防冲突过程,射频场内的射频卡将可以逐一被识别并进行数据交换。

2.3 串行通信程序

系统使用PC机作为上位机,读卡器作为下位机。上位机与下位机之间的通信采用基于RS-232-C的串口通信。RS-232-C是一种串行通信总线标准,是数据终端设备(DTE)和数据通信设备(DCE)之间的接口标准,不同厂家生产的设备,只要它们都具有RS-232-C标准接口,则不需要任何转换电路,就可以互相插接起来。

串行通信程序是MCU与PC机通信的控制程序。发送程序采用查询的方式设计,即把待发送的数据先送到缓冲区中,然后查询串口发送中断标志是不是有空,若有空就发送下一个数据。

接收程序采用中断的方式设计,即当PC机要发数据给MCU时,主动向MCU申请中断,接收中断标志有效,则PC向MCU传送数据。

3 验证方案

3.1 验证平台的建立

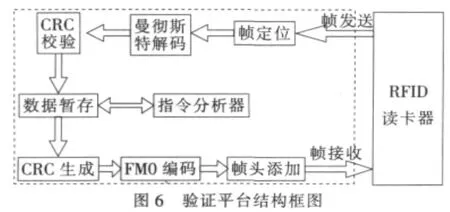

为了验证所设计的读卡器能否完成预期的功能,设计了相应的验证平台[8]。验证平台由数据解码通道、数据编码通道以及指令分析器三部分组成。数据解码通道是对读卡器发送出的数据帧进行解码,提取指令的原始数据;指令分析器是对收到的指令数据进行判断,同时返回相应的数据并发送给数据编码通道;数据编码通道则是对发送来的数据进行编码,再发送给读卡器。

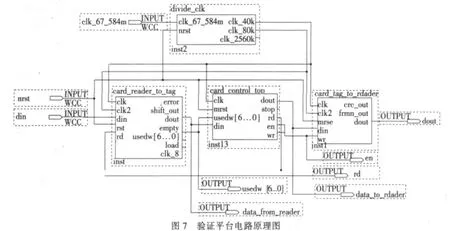

平台采用Verilog HDL硬件语言搭建,选用Altera公司Cyclone系列的EP1C6Q240C8芯片为目标器件,使用Quartus II进行综合验证,其结构框图和电路原理图分别如图 6、图7所示。

3.2 测试结果分析

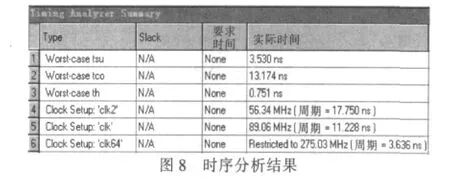

(1)时序分析

通过运行QuartusII 7.1自带的时序分析器,可以得到时序分析的一些参数:tsu(输入建立时间)、tco(时钟到输出延时)、th(保持时间)分别为 3.530 ns、13.174 ns、0.751 ns。基频时钟clk最大可以达到89.06 MHz,而ISO/IEC 18000-6 Type B协议规定的基频时钟为40 kHz。从分析本系统的时序结果显示,完全符合协议要求。具体的时序分析结果如图8所示。

(2)功能分析

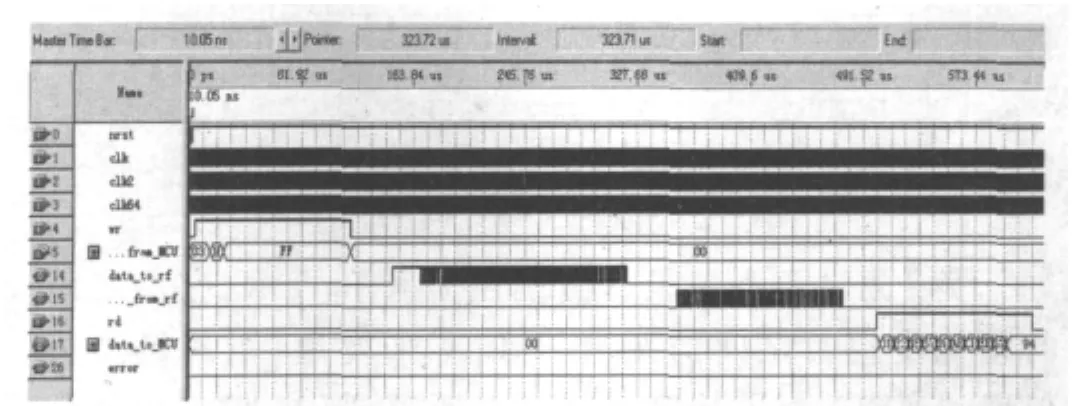

功能分析以GROUP_SELECT_LT命令为例。GROUP_SELECT_LT命令是多卡操作中的组选命令,射频卡接到此命令,卡内指定地址的数据与帧中提供的数据进行对比。若卡内数据较小,则返回射频卡的64 bit序列号,否则不作任何响应。GROUP_SELECT_LT命令的命令号为 03,地址设为 0F,掩码设为 FF,64 bit数据全设为F,所以从MCU传给FPGA的命令数据为03_0F_FF_FFFF_FFFF_FFFF_FFFF。原始数据经过FPGA数字信号处理模块处理后,就成了一帧基带数据信号。验证平台将读卡器发来的数据帧进行解码,然后判断指令并返回射频卡的64 bit序列号,经编码后成一帧数据帧发送给读卡器。读卡器收到此帧后即解码,并进行CRC校验,若都没有错,则把解码后的数据传输给MCU。

GROUP_SELECT_LT命令仿真波形图如图9所示,实验证明可实现ISO/IEC 18000-6 Type B协议。

图9 GROUP_SELECT_LT命令仿真波形图

随着RFID相关国际标准的确立 (如ISO/IEC 18000)RFID的研发已成为国际性的课题。在诸多RFID工作频段中,UHF频段的RFID技术前景最为看好,也成为现今RFID技术领域研究的热点。

[1]周晓光,王晓华.射频识别(RFID)技术原理与应用实例[M].北京:人民邮电出版社,2006.

[2]倪荣生.超高频RFID系统的发展和趋势分析[J].中国防伪报道,2007(11):41-47.

[3]刘韬,楼兴华.FPGA数字电子系统设计与开发实例[M].北京:人民邮电出版社,2006.

[4]ISO/IEC JTC1/SC31/WG4N0722.ISO/IEC FDIS 18000-6:2003(E)[S].Geneva:ISO copyright office,2003.

[5]张迎新,雷文,姚静波.C8051F系列SOC单片机原理及应用[M].北京:国防工业出版社,2005.

[6]范佳林.915MHz RFID阅读器设计[D].大连:大连理工大学,2006.

[7]陆永宁.非接触IC卡原理与应用[M].北京:电子工业出版社,2006:94-97.

[8]CILETTI M D.Verilog HDL高级数字设计[M].张雅绮,李锵,等译.北京:电子工业出版社,2005.

Design of 915 MHz radio frequency reader based on FPGA

Yang Bihua1,Wen Zhangbin2

(1.College of Information Science and Technology,Jinan University,Guangzhou 510632,China;2.Institute of Information Technology,Jinan University,Guangzhou 510075,China)

Based on ISO/IEC 18000-6 Type B protocol,a 915MHz RFID reader was designed.FPGA was used to process the digital signal that was based on the protocol and C8051F020 was used as the controller.Each module in FPGA and verification module were designed by Verilog HDL.They were synthesized by Quartus II with EP1C6Q240C8 CMOS chip of the Altera as the target device,and they were verified on both timing and function.The result showed that it could satisfy the technology index of ISO/IEC18000-6 Type B requests and possesses the advantages of flexible structure,small size,easily upgrading and so on.

RFID;reader;FPGA;C8051F020

TP338.1

A

1674-7720(2011)03-0022-04

国家自然科学基金项目(60505018);广东省自然科学基金项目(8451063201000361)

2010-09-01)

杨碧华,男,1983年生,硕士生,主要研究方向:智能建筑,网络技术与系统集成。