基于ADSP-21992的电力系统准同期装置的设计

王洪坤,马玉荣,聂晶

(1石河子大学机械电气工程学院,石河子832003;2石河子天富水利水电工程公司,石河子832000)

基于ADSP-21992的电力系统准同期装置的设计

王洪坤1,马玉荣2,聂晶1

(1石河子大学机械电气工程学院,石河子832003;2石河子天富水利水电工程公司,石河子832000)

为保证电力系统的安全及经济运行,必须依靠先进的自动装置。本文以ADSP-21992为核心,设计实现了电力系统准同期装置的硬件电路及准同期软件系统。首先以实现同期功能为目的,设计实现了准同期装置的硬件电路,包括数据采集模块、外部接口模块,然后设计实现了装置的同期主程序及中断服务子程序。经功能试验测试,能够满足准同期装置性能要求。

准同期;ADSP;数据采集;接口电路

随着我国智能电网的不断发展,研制电力系统自动控制装置越显必要和急迫,并成为电力系统研究领域中新的热点。

由于社会的发展和工业规模的不断扩大,对电能质量和供电可靠性的要求也随之不断提高。最早简单的手动同期指示装置及采用分立晶体管元件搭建硬件电路模拟式准同期装置现在已经基本被淘汰[1-3]。

目前的微机自动准同期装置,一般采用单片机作为主控器件,但普通单片机包括16位单片机不能快速地完成复杂算法。DSP处理器的价格与普通单片机相近,但其性能却远远超过了普通单片机[4-6]。DSP处理器的突出特点就是采用多总线技术实现了并行机制,有独立的加法器和乘法器,有灵活的寻址方式,有更高的运行速度和更方便灵活的指令系统[7-9],从而能够以非常快的速度处理复杂算法,为完成准同期装置的功能提供了极大的方便。

1 准同期装置的硬件电路设计

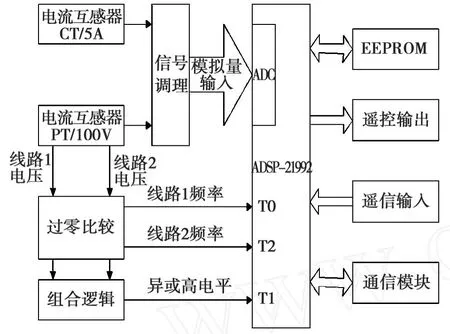

自动准同期装置在硬件上以ADI公司ADSP-21992数字信号处理器为核心,具有运算速度快、内存容量大、抗干扰性能好等优点。准同期装置的硬件结构如图1所示。

ADSP-21992是准同期装置的核心,装置的软件存放在BOOT ROM内,定值存放在 E2PROM内。交流量经过高精度互感器,经过信号调理,由14位AD 8路同步采样。交流信号波形变为方波后,采用硬件抗干扰机制后送入80 MHz为计数频率的DSP时钟口,由DSP计算出方波的频率及频率变化率[10]。

图1 准同期装置的硬件结构图Fig.1 The Hardware Structure of Synchronizing Device

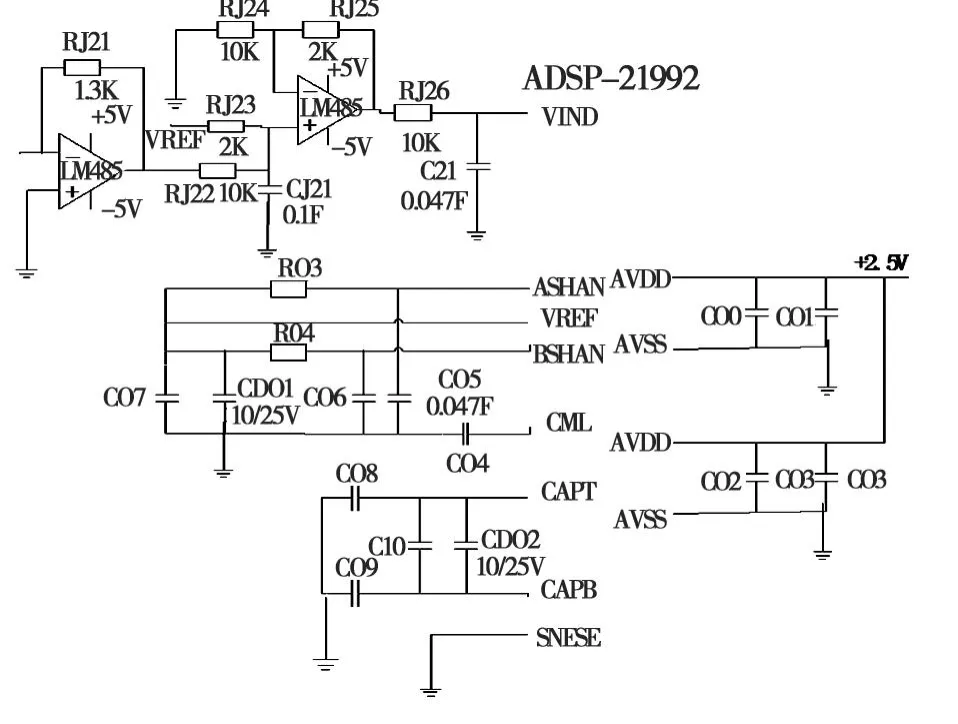

1.1 A/D转换输入配置电路

模拟量采集电路的设计包括电压信号和电流信号采集[11-12],电压、电流互感器将较高的电压信号和较大的电流信号转换为-5 V~+5 V的低电压信号,送入 ADSP-21992ADC模块的接收端进行采样。ADSP-21992集成了1个快速精确的多通道A/D转换器。本设计中的电压和电流模拟量采集及A/D转换输入配置设计如图2所示。

图2 模拟量采集及A/D转换接口配置电路Fig.2 Analog Acquisition and A/D Conversion Interface

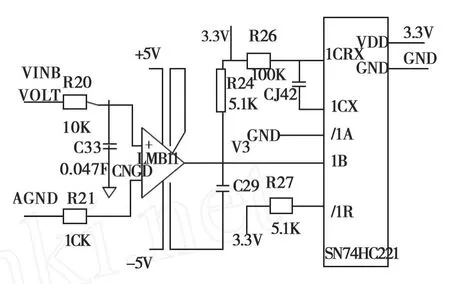

1.2 频率测量采集电路

图3 为频率测量电路。该电路输入0~5 V电压信号,电路中由LM311组成电压比较器用于检测交流信号的过零点,采用触发器SN74H211改善方波质量,一方面稳定方波幅度使方波上下沿变陡,另一方面使方波占空比可调,有利于可靠计数。

图3 频率测量电路Fig.3 Frequency Measuring Circuit

2 ADSP-21992外部存储模块驱动设计

2.1 SPI外设接口

ADSP-21992有一个独立的、标准的串行外设接口SPI,可以广泛的与SPI兼容外设器件进行I/O接口。本装置SPI外设为定值存储芯片X5043,首先对X5043进行片选,将 SPIFL G寄存器的 FLS4位设置为“1”,使能 PF4;设置 SPI波特率寄存器,写入0x50,则SCK频率为0.5 MHz;设置SPI控制寄存器SPICTL为“0x5c08”,分别设置 SPI从选引脚使能,以及SPICL K低有效,SPI模块为主机。相关程序如下:

sysreg_write(sysreg_IOPG,SPI0_Controller_Page);//选择IO页

io_space_write(SPIFL G0,0xff10);//使能 PF4

io_space_write(SPIBAUD0,0x50);//设置波特率

io_space_write(SPICTL0,0x5c08);//SPI为主机,设置SPI控制寄存器

2.2 外部RAM扩展

外部存储器接口EMI提供了DSP内核与DSP外围之间或DSP内核与片外存储器之间进行8位、16位或24位数据传送功能。根据本设计的要求其外部存储器接口寄存器的设置如下:

1)控制寄存器EMICTL。控制寄存器 EMICTL是一个7位寄存器,其赋值为1111000,总线请求延迟未使能,外部总线宽度选择16位,读写逻辑为负逻辑,DSP能读/写MSxCTL、BMSCTL和IOMSCTL寄存器。

2)引导存储器选择控制寄存器BMSCTL,其赋值为100001101101,完成一次外部数据传送所需要等待的I/O时钟周期数为5;只用内部等待状态;EMICL K与 HCL K时钟分频比率为1∶1。

3)I/O存储器选择控制寄存器 IOMSCTL,存储器选择控制寄存器MSxCTL与BMSCTL设置相同,其赋值为100001101101。

4)外部接口状态寄存器EMISTAT。外部接口状态寄存器是一个只读寄存器,它保存着外部接口的状态。

3 准同期装置的软件系统设计

软件设计采用模块化的设计思路,构成装置的软件系统分为主循环程序和中断处理子程序两大部分。中断处理子程序主要有确2个:一个是1 ms定时中断,主要负责时间的刷新、遥信扫描及 COS、SOE记录、遥控信号时间的控制、同期信号的有关时间的控制等;另一个是AD采样中断,负责交流采样和录波。

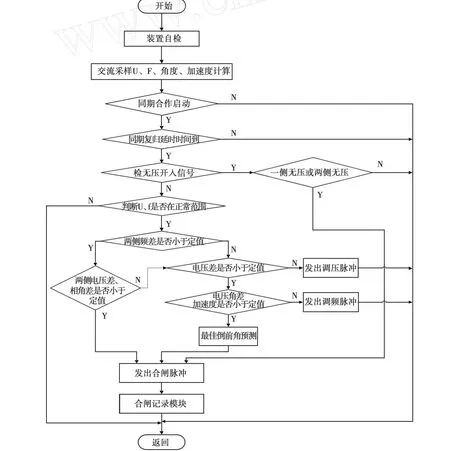

设计同期主循环程序流程如图4所示。

图4 同期主程序流程图Fig.4 The Main Program of Same Period

3.1 1 ms定时中断

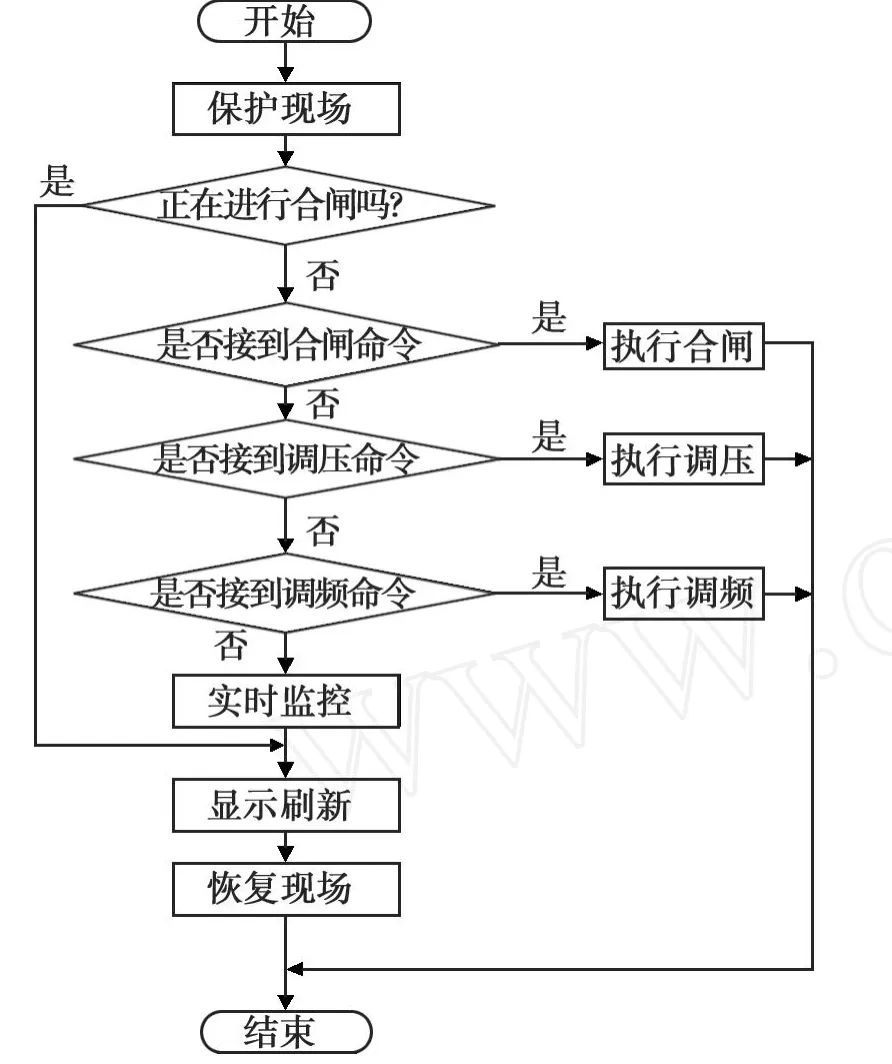

1 ms中断服务程序是一个底层程序,它由均频、均压、合闸和显示等处理模块组成,实现1 ms的定时服务程序接收其它中断服务程序和主程序给它发送的各种控制命令和显示代码,完成各种控制作用,并根据各自软件定时器的状态输出控制脉冲。

1 ms定时中断程序流程如图5所示。

图5 1 ms中断服务程序流程图Fig.5 1 ms Interrupt Service Program

3.2 AD采样中断

数据采集模块主要完成数据的采集、存储和相关的处理任务。系统运行后,初始化定时器,配置A/D转化器控制寄存器 TRIGSRC=000,确定AD的采样启动方式为PWM同步信号的上升沿。通过设置A/D转化器控制寄存器MODSEL=000,确定ADSP-21992的2个模拟量被同时采样的采样模式,在每一对模拟输入转化结束后,ADCSTA T寄存器中相应的位被置1,所有8个A/D转化数据寄存器都存储有效的转化结果。当所有数据被写到ADC0-ADC7中时,就会产生一个专用的ADC中断。AD完成一次转换后,触发中断,进入中断程序读取AD的8通道的转换数据,分别存入相应的数据缓冲器中,同时判断数据缓冲器是否溢出。如果数据缓冲器溢出,则停止A/D数据转换,对采集到的数据进行数据运算处理后,清空数据缓冲器,然后重新启动定时器,开始新一轮的数据采集。

4 准同期装置的测试

为达到电力系统同期装置的要求,装置具有一条线路的完备测控功能,能够测量三相电压、电流、相位;2路独立遥控,8路外部遥信。装置除具有准同期功能外,还具备检无压(一侧无压或两侧无压)快速合闸功能。设计要求的电压电流测量精度为±0.2%;频率测量精度为±0.001 Hz;相角差测量精度为 ±0.1°。

4.1 遥测功能测试

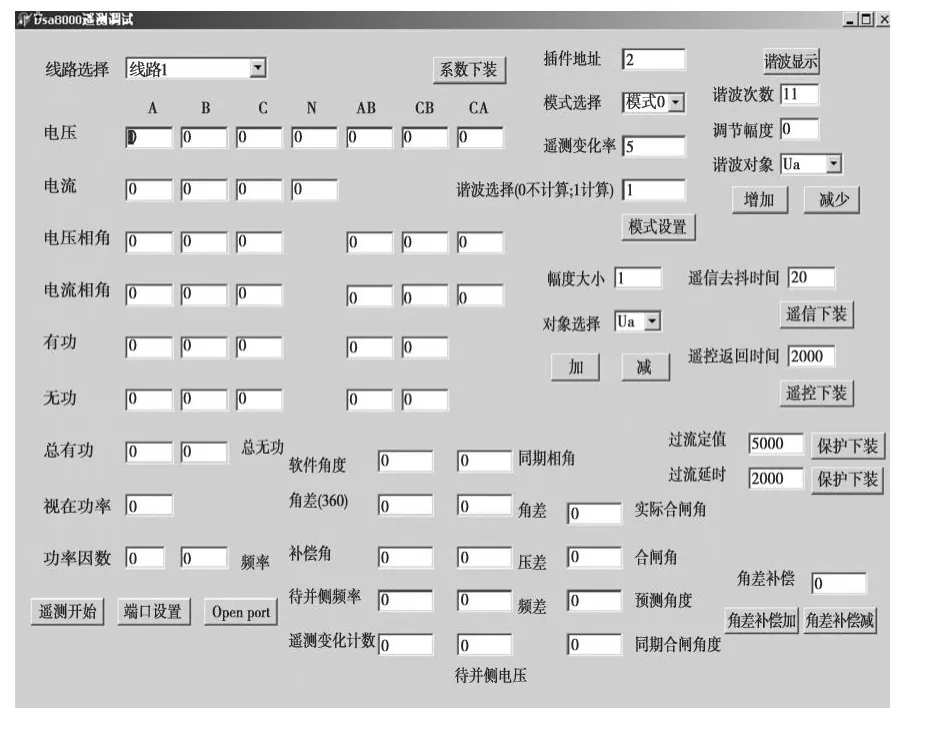

遥测功能测试通过准同期装置的485口进行。装置与计算机通讯连接后,运行同期测试工具软件,出现测试工具软件界面(图6),然后可对遥测的每一项数据逐项进行测试。

准同期装置有同期电压和同期频率,界面中的角差、压差、频差和待并侧频率就是与同期电压有关的几个测量值,其电压电流的测量精度为±0.15%;频率的测量精度为±0.001 Hz;相角差的测量精度为±0.05°,满足精度要求。

图6 测试工具软件界面Fig.6 Interface of Software Testing Tools

4.2 准同期遥信及遥控功能测试

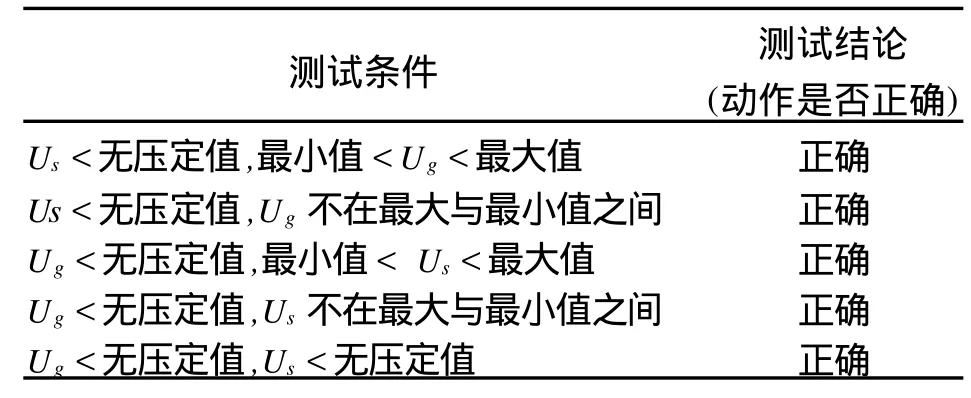

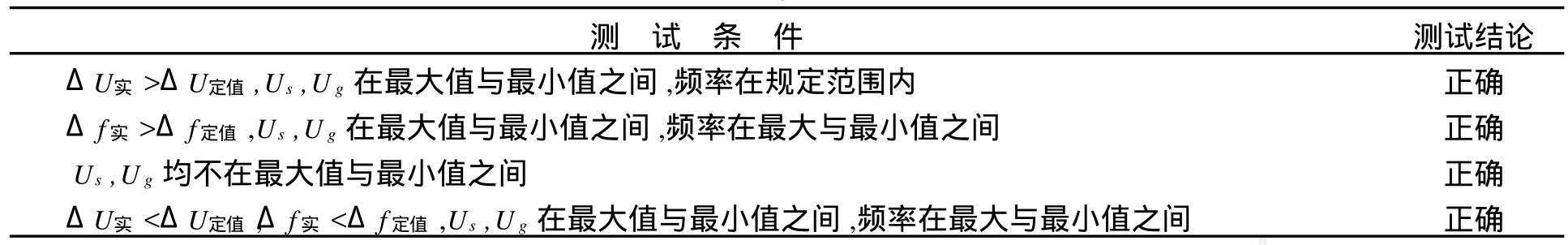

根据同期遥控功能的合闸条件,进行同期检无压功能、同期闭锁功能、同期环并网功能3项测试。同期检无压功能和同期闭锁功能的测试结果分别见表 1、表 2。

表1、表2结果表明:该装置动作正确,满足同期遥控功能,测量数据精度高,遥控合闸动作可靠、实现了同期闭锁功能及检无压功能,具备自动准同期装置的基本功能,测试结果达到了测试要求与设计要求。

表1 同期检无压功能测试Tab.1 voltage-check Function test

表2 同期闭锁功能测试Tab.2 Blocking Function Tests

5 结语

本设计源于现场工程实践,从准同期的原理出发,结合目前系统运行的各种新状况,利用新型32位微处理器ADSP-21992,对传统的微机准同期装置进行了改善,完成了基于ADSP-21992嵌入式系统的新型自动准同期装置的设计与开发。但由于装置还在开发过程中,其抗干扰性和迅速反映能力还需经实际的电力系统进一步的检验。

[1]叶念国.由我国同期装置的现状所引发的思考[J].电网技术,1998(2):74-77.

[2]刘佩芬,朱雅清,李宏.大型同步发电机的自动准同期[J].西北电力技术,2004(1):52-54.

[3]杨冠城.电力系统自动装置原理[M].上海:上海交通大学,2005:10-50.

[4]李继晟,郑蔚,叶艳军.一种新型的综合测控装置中同期功能的设计实现[J].继电器,2005(5):56-62.

[5]王伟.基于DSP的自动准同期装置的研制[D].国电自动化研究院,2006:12-25.

[6]薛玉峰.基于DSP的中小型同步发电机综合测控装置研究与开发[D].西安:西安理工大学,2007,3-7.

[7]杨小铭,赵祥,蔡月明.基于DSP的智能准同期测控装置[J].农村电气化,2007(10):35-36.

[8]骆武,宁海涛.80C196KC单片机自动准同期并网装置的研究[J].继电器,1998(7):42-44.

[9]赵丽,刘昭.嵌入式 Internet监控系统在变电站通信中的应用[J].石河子大学学报:自然科学版,2007,25(3):394-396.

[10]王晓明,庄喜润,等.高性能工业控制控制DSP[M].北京:北京航空航天大学出版社,2005:50-75.

[11]王洪坤,马玉荣,谢江.基于GSM技术的配电变压器防盗系统的硬件设计[J].石河子大学学报:自然科学版,2006,24(3):329-331.

[12]张晓海,任杰,张宁等.单片微型计算机与 PC机串行通信的研究[J].石河子大学学报:自然科学版,2002,20(2):147-149.

[13]戴维德 F斯图特.运算放大器电路设计手册[M].北京:人民邮电出版社,2005:30-85.

[14]李涛,田敏.基于模糊自适应 PIO控制的水电站自功功率调节[J].石河子大学学报:自然科学版,2009,27(5):651-653.

Design and Implementation of Power System Automatic Quai-Synchronization Device Based on ADSP 21992

WANG Hongkun1,MA Yurong2,NIE Jing1

(1 College of Mechanical and Electrical Engineering Shihezi University,Shihezi 832003,China;2 Shihezi Tianfu Water Conservancy Engineering Company,Shihezi 832000,China)

Advanced automatic control technology and equipment can ensure power system’s safety,economic operation and power quality.This paper designs interface circuits of synchronization device in power systems based on a core of ADSP-21992,which contains data collecting unit and external interfaces of ADSP-21992.Finally,the software system of device is developed,which includes main procedure and interrupt service routine.Though testing,the device can meet the requirements of engineering design.

quasi-synchronization;ADSP;data acquisition;interface circuit

TP368.1

A

1007-7383(2011)02-0260-05

2010-11-29

王洪坤(1975-),男,讲师,西安交通大学,从事电力系统自动化研究;e-mail:wanghongkun@shzu.edu.cn。