基于Actel FPGA的正交解码方案

随着电子自动化和智能化的普及,电机的应用场合越来越多,这就使得正交解码器的应用越来越广泛。数控系统中如机器人、测量仪器、数控机床等领域中。用光栅传感器、旋转编码器、激光陀螺进行位置检测和位置定位。这类测量系统的输出一般为两路相位差90°的正交脉冲信号,通过该正交解码方案可从正交信号中获得测量系统所需要的位移或角位移等测量数据,从而构成闭环系统实现运动控制算法。

本文主要介绍采用高可靠性、低成本的Actel PPGA来实现正交解码系统,为大家提供一种正交解码的实现方案。传统MCU一般只支持一至两路正交解码,本方案是为了满足用户对多路正交解码以及特殊功能需求而设计,同时结合了Actel FPGA单芯片、上电即行、低成本、低功耗、高安全性和高可靠性的优点,使得正交解码系统在传统的MCU实现方式上得以衍生,可以应用在各种不同需求的场合。本文以单路功能介绍为主,多路仅是在单独基础上的重复。

1概述

(1)功能概述

·支持位置捕获和速度检测:

·支持正交相位模式和时钟/方向模式;

·根据需要可设计支持16、24、32位位置计数模式;

·支持正交错误、方向改变、索引检测等三种中断方式;

·根据需要可设计成对多路正交信号进行解码,实现多路正交解码;

·支持一路串口收发、地址管理、片选控制和AB相滤波处理等操作;

·系统频率为70MHz,超过一般MCU的采样频率;

·资源占用率低。单路24位模式、支持中断控制、支持正交相位和时钟/方向模式、支持位置捕获的正交解码可用Actel的A3P030实现,多路可用A3P060及以上器件实现,具体资源占用情况与实际功能需求有关;

·FPGA的可编程性使得功能设计非常灵活,可以根据用户需求定制特殊功能;

·真正完美的单芯片、低成本、低功耗解决方案;

·ActelFPGA的FlashLock和AES双重加密,保护您的设计;

·Actel FPGA的固件错误免疫使得系统可以工作于较恶劣的环境中,可靠性极高。

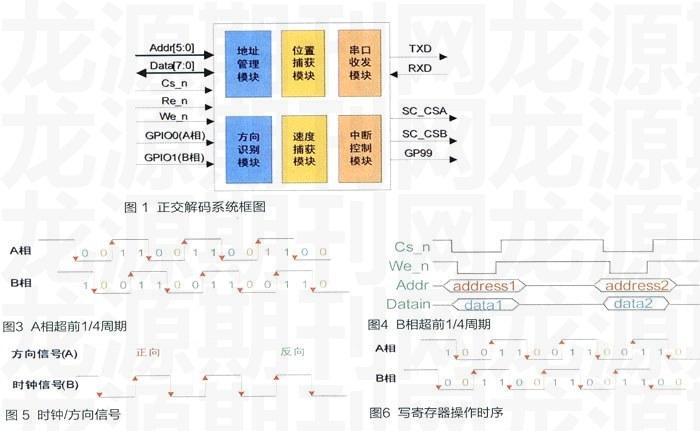

(2)系统框图

图1是基于Actel FPGA的正交解码系统结构图。该正交解码系统采用模块化设计,主要由方向识别、地址管理、位置捕获、速度捕获、中断控制和串口收发等模块构成。萁中,方向识别模块主要完成将外部输入的A、B相信号进行细分和辨向:地址管理模块用于管理系统内部的寄存器地址:位置捕获模块用于跟踪外部电机的旋转位置:速度捕获模块用于检测外部电机的旋转速度:中断控制模块用于管理正交错误中断、方向改变中断、索引检测中断的使能和触发:串口收发模块主要用于本系统与PC机、以及本系统与MCU之间的数据传输。

按照接口类别划分,可以把整个系统的接口分为:基本接口、地址接口、数据接口、控制接口、串口接口、正交接口等。详细的接口信息如表1所示。

2各功能模块介绍

(1)方向识别模块

方向识别模块只有在正交相位模式时才会用到,而在时钟/方向模式时不会用到,除此之外,两种模式完全一样。在正交相位模式中,编码器产生两个相位差为90度的时钟信号,它们的边沿关系被用来确定旋转的方向。设A相超前时为正向计数,则B相超前时为反向计数。由图2和图3两个正交信号时序网可以得出,正向时AB状态分别以01、00、10、11循环出现。我们人为对这几个状态编号使AB状态为0l时对应1:AB状态为00时对应2;AB状态为10时对应3;AB状态为11时对应4。不难得到正向计数时、对应自然数的变化规律为1、2、3、4、1、2、3、4……循环变化,下一状态减去前一状态所得到的值只有两种情况(1或是,3)。同理,反向计数时AB状态变化对应的自然数为3、2、1、4、3、2、1、4……循环变化,下一个状态减去前一个状态所得到的值也只有两种情况(-1或是3)。通过下一状态和前一状态的差值可以判断出正交信号的方向信息。

(2)位置捕获模块

位置捕获模块的核心部分是根据A、B相的边沿进行可逆计数。在正交相位模式下,A相的边沿超前B相的边沿时,位置计数器在每检测到一个边沿就加1;A相的边沿落后B相的边沿时,位置计数器在每检测到一个边沿就减1。

在时钟/方式模式下,编码器产生一个时钟信号和一个方向信号来分别表示步长和旋转方向,当方向信号为高电平时,位置计数器在每检测到一个边沿就加1;当方向信号为低电平时,位置计数器在每检测到一个边沿就减1。具体的时钟/方向信号如图4所示。

(3)地址管理模块

地址管理模块包括写寄存器地址管理和读寄存器地址管理。写寄存器地址管理主要是根据MCU发送的写寄存器地址来进行相应寄存器的更新。读寄存器地址管理主要是根据Mcu发送的读寄存器地址来把相应的寄存器值传送到数据接口。典型的读写操作时序如图5和图6所示。

(4)速度检测模块

在该正交解码系统中,速度检测采用定时一分钟,并在一分钟内检测A、B相的边沿个数,MCU通过读取速度寄存器的值就可以得知一分钟内的边沿数,从而变相测出速度值。实际定时时间可根据需要进行设定。

(5)中断控制模块

该正交解码系统支持正交错误、方向改变、索引检测三种中断方式。每个中断都有相应的中断使能位和中断标志位。只有在中断被使能时,中断条件满足时才会产生相应中断。当中断标志位为1时,通过向该中断标志位写1可清除中断标志位,否则中断标志位一直保持。

(6)串口收发模块

该正交解码系统中,串口发送模块的功能是:当MCU判断FPGA当前没有数据发送时,可以发送数据给FPGA的串口寄存器,FPGA再把相应的数据通过串口发送给PC机。串口接收模块的功能是:当PC机通过串口发送数据给FPGA时,FPGA接收数据并置数据标志位,并通知MCU把数据读走。由此看出,FPGA在PC机和MCU之间起数据链路的作用。

3市场应用

正交解码器在电机控制市场占有率较大,它主要用于一些需要电机控制的数控系统中,如机器人、测量仪器、数控机床、轨道控制、自动化生产线等领域。随着电子自动化和智能化的普及,电机的应用场合越来越多,这也使得正交解码器的应用越来越广泛。该正交解码系统的典型应用如图7所示。

4小结

本文主要介绍了基于Actel FPGA的正交解码系统的功能和应用。敬请关注周立功公司的网站www.zlgmcu.com以获得更多的信息。我们有着一个接近30人的FPGA团队提供强有力的售后服务和技术支持,解决用户在产品使用和研发过程中遇到的困难。若有更多的需求可以与我们联系,我们将会竭诚为您服务,并请关注下期的FPGA专题技术讲座。