基于低功耗的BIST测试生成结构优化设计

姚丽婷,谈恩民

(桂林电子科技大学 电子工程学院,广西 桂林541004)

现今的SOC测试设计中,面临着许多问题,尤其是在降低功耗方面。由于在测试模式下,功耗消耗比正常模式下高很多[1],为了解决测试功耗问题,许多学者从许多不同的角度进行了各种改进尝试。在VLSI电路设计中,低功耗问题已成为测试问题的首选。在电路测试过程中由于测试向量的伪随机特性导致测试效率随测试向量的增加迅速下降,要达到一定的故障覆盖率必须需要产生很长的测试向量集,测试向量的伪随机特性和无效测试向量(对故障覆盖率没有贡献的测试向量)导致测试功耗增加。因此,在测试模式下电路的功耗要比正常工作模式下要高很多,可以达到两倍以上。由于CMOS电路的测试功耗主要由电路节点的翻转引起,过度频繁的翻转将带来成本、可靠性、性能和验证等方面的问题。由于功耗的增加,为了散发产生的热量则必然要采用散热性好但成本高的封装工艺,增加了产品成本。同时集聚的热量会导致硅晶失效、电子迁移等,降低了系统的可靠性[2]。

在BIST中常用线性反馈移位寄存器(LFSR)作为测试模式生成器(TPG)。LFSR必须产生很长的测试矢量集才能满足故障覆盖率的要求,但这些矢量消耗了大量的功率。在系统工作模式下,应用于给定电路的连续功能输入矢量具有重要的相关性,而有LFSR产生的连续测试向量之间的相关性很低。因此,在测试期间会增加电路中节点的翻转活动,导致功耗的增大。

1 功耗分析

CMOS电路的功耗一般由静态功耗和动态功耗两部分组成。在CMOS电路中由于各种泄漏电流的存在,从而导致了CMOS的静态功耗,因为CMOS的电路结构决定了上下两只互补晶体管只在翻转时才全部导通,其他时候则总有一只处于截止状态,所以静态功耗的影响并不大。而动态功耗则是由电容充放电和短路电流功耗所构成。对于现在的CMOS电路而言动态功耗是电路功耗的主要部分,因此降低测试功耗的前提是分析和估计动态功耗。

下面介绍几个有关功耗的概念[2-3]:

1)总功耗 测试模式下电路节点翻转次数的总和。对于电池供电的设备,它影响电池在上电自检测试模式下的使用时间。

2)平均功耗 一段时间内总功耗的平均值,即总功耗与时间之比。平均功耗的增加会导致热载效应,如不及时散发热量将导致硅片、焊点以及封装的结构性损坏。

3)瞬时功耗 在任意特定时刻的测试功耗,一般是指一个同步时钟周期的功耗。瞬时功耗过大可能会引起功率分配系统过载,导致供电停止。

4)峰值功耗 在任意特定时刻的最高功耗值,它决定了电路的电气特性和热特性的界限以及封装形式。如果峰值功耗超过一定的界限,电路将不能正常工作。时间上,电路峰值功耗的时间窗口与该电路的热容量有关,有时定义这一时间窗口为一个时钟周期只是简单的假设。例如,对于一个被测电路在某个时钟周期达到峰值功耗而其他时间都小于热容量界限,则电路不会轻易损坏,这是由于一个周期的峰值功耗还不能将温度提升到电路热容量的界限,除非该峰值功耗远远超过正常值。要损坏电路硅片,高功耗必须持续多个周期。

CMOS电路的功耗主要由功能跳变、短路电流、竞争冒险和漏电流引起的,前三种称为动态功耗,它是由电路器件翻转时负载电容充放电及短路电流构成,被认为是电路功耗的主要来源,某一节点的动态功耗[4]:

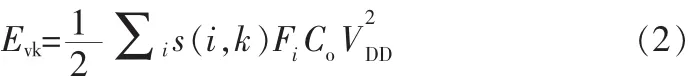

式中,Si为此节点翻转的次数,Fi为该节点的扇出数,Co为单位输出的负载电容,VDD代表电源电压,SiFi称为节点i WSA(Weighted Switching Activity)。

根据式(1)的推导,在测试过程中,若输入一对连续的测试向量(Vk-1,Vk)时电路消耗的功耗为:

式中,i指电路中的所有节点,s(i,k)是测试向量 Vk使节点 i产生的翻转数。

如果T表示时钟周期,则瞬时功耗Einst(Vk)就是单位时间内连续测试向量所产生的功耗,即为:

若假设伪随机测试序列的长度为Lengthtest,那么在测试过程中电路消耗的总功耗就是k个测试向量在被测电路上所产生的功耗之和,表示为:

同时平均功耗为总功耗与总测试时间的比值,即:

而峰值功耗就是瞬时功耗的最大值,即:

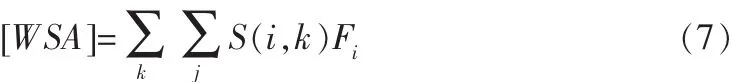

由于电源电压和单位输出负载电容是定值,SiFi是功耗分析中唯一可变因素,所以WSA可作为衡量功耗的标准。考虑电路总的测试矢量集 TP=(V1,V2,…,Vn), 电路总的 WSA 为:

其中 i包括电路中所有的节点,S(i,k)为矢量 TPK引起节点i翻转的次数。为了最大限度地降低CUT输入端的跳变率,可以采用在LFSR生成的每两个相邻向量之间插入n个向量(n为LFSR的位数),使它们中的每一个与其前驱向量只有1位不同,这样就可以获得准单输入的伪随机测试向量集(仅在LFSR产生下一个向量时是单跳变),使得平均功耗由于Si的减小而降低。同时保持测试集的长度不变、即测试时间t不变,故电能消耗也得到缩减。

2 低功耗设计

基于以上所述,为提高测试矢量间的相关性,降低测试功耗,对LFSR结构进行改进,达到减少跳变的效果,即在相邻向量之间插入3个向量,这种设计没有降低原序列的随机特性,却减少了被测电路输入端的变化,所以达到了降低功耗的效果[5-7]。

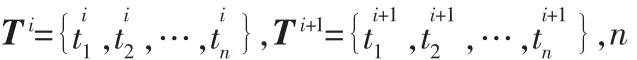

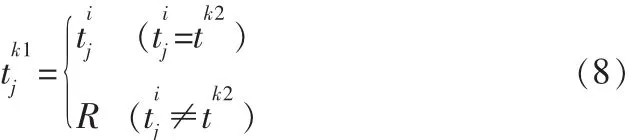

式中, j∈{1,2,…,n},R∈{0,1}。

Tk2也可以按照相同的方法得到。如果Ti和Tk2对应位相同,那么Tk1的相应位也取此值;如果不同,取随机的R值,这种方法称作R注入。

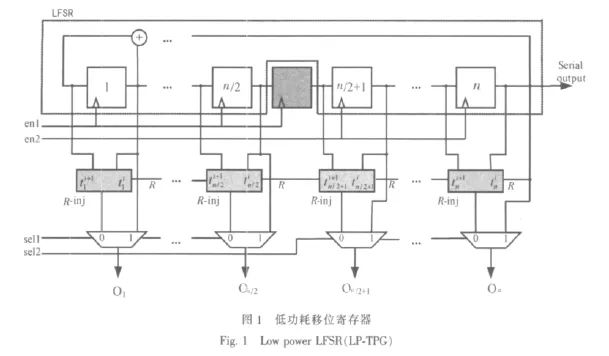

图1为LP-TPG结构即Low Power LFSR,它是由en1,en2,sel1,sel2共同作用下进行工作的。工作流程如下:

1)en1en2=10,sel1sel2=11。 LFSR 的前半部分激活,后半部分处于空置状态。选择sel1sel2=11,使LFSR的全部状态得到输出,即 Ti。

2)en1en2=00,sel1sel2=10。 LFSR 全部 处于空置 状态。LFSR前半部分的状态被输送到输出端O1到On/2,而R注入电路的输出被输送到输出端 O(n/2)+1到 On。 即生成 Tk1。

3)en1en2=01,sel1sel2=11。 LFSR 的后半部分激活,前半部分处于空置状态。LFSR的全部状态得到输出,即Tk2。

4)en1en2=00,sel1sel2=01。LFSR全部处于空置状态。前半部分的R注入电路输出被输送到输出端O1到On/2,LFSR后半部分的状态直接输出到输出端 O(n/2)+1到 On。即生成Tk3。

5)返回步骤 1)生成 Ti+1。

8位LFSR使用LP-TPG生成向量的结果如表1所示。

表1 8位LFSR使用LP-TPG生成的向量Tab.1 Vector generated by 8-bit LFSR with LP-TPC

3 试验结果

将这种低功耗测试生成方案在ISCAS基准电路上进行试验,测试性能分析所用到的工具是:组合电路确定向量生成工具atalanta,组合电路并发故障仿真工具fsim。

试验前用C++编程模拟上述测试生成过程,将得到的测试向量集施加给待测电路,再计算电路功耗和故障覆盖率。由于在测试模式下电路的功耗要比正常工作模式下要高很多,而主要是由电路节点的翻转所引起的,所以经过对LFSR结构的改进后,可以提高测试序列间的相关性,减少测试序列长度的同时也降低输入跳变。表2中给出了传统LFSR以及改进后的LP-TPG所产生的测试矢量个数以及WSA值的对比,表3则是对两种方案所得到的结果进行比较,从而计算出相对的降低幅度。

表2 两种不同方案的测试生成结构比较结果Tab.2 Results for two different test generation methods

表3 LP-TPG较LFSR功耗的降低比率Tab.3 Changes in test length,average and peak WSA compare to LFSR

从表3中的分析结果可以看出,经过LFSR改进的LPTPG结构的测试矢量个数、平均功耗、峰值功耗都较之前得到了相对的提高。可见传统的LFSR结构经改进后,性能得到提高,对测试长度,测试功耗都有所改善,具有一定的发展前景,对比前后测试方案,本文提出的方案存在一定优点。

4 结 论

本文提出在测试模式期间降低平均功耗和峰值功耗,利用增加测试矢量之间的相关性,提高输入矢量的跳变率,从而达到降低功耗的效果。LP-TPG所产生的测试序列之间的跳变较少,不但可以降低平均功耗,而且也降低了测试中的峰值功耗,同时并不影响故障覆盖率。因此,LP-TPG相对于传统的LFSR结构更高效。

[1]Zorian Y.A distributed BIST control scheme for complex VLSI devices[J].In Proc:VLSI Test Symp,1993(VTS’93):4-9.

[2]Girard P.Survey of low-power testing of VLSI circuit[J].IEEE Design&Test of Computers,2002,19(3):82-92.

[3]Girard P,Guiller L,Landrault C,et al.A modified clock scheme for a low power BIST test pattern generator[J].In Proc:VLSI Test Symp,2001(VTS’01):306-311.

[4]Wang S,Gupta S.DS-LFSR:A new BIST TPG for low heat dissipation[J].In Proc.Int.Test Conf,1997,(ITC’97):848-857.

[5]LI Jie.A new BIST structure for low power testing[J].in Proc.IEEE.2003:1183-1185.

[6]何蓉晖,李晓维,宫云战.一种低功耗BIST测试产生器方案[J].微电子学与计算机,2003,20(2):36-39.

HE Rong-hui,LI Xiao-wei,GONG Yun-zhan.A low-power BIST test generator program[J].Microelectronics and Computer,2003,20(2):36-39.

[7]陈卫兵.一种新的低功耗BIST测试生成器设计[J].集成电路与元器件,2004,11(2),62-63.

CHEN Wei-bing.A new low-power BIST test generator design[J].Volume IC and Components,2004,11(2),62-63.