一种数字钟的设计

于莹莹 林喆

辽宁装备制造职业技术学院( 沈阳 110161 )

0 引言

数字钟是一种用数字电路技术实现时、分、秒的计时装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更长的使用寿命,因此得到了广泛的使用。

数字钟可用典型的数字电路实现,其中包括组合逻辑电路和时序电路。目前,数字钟的功能越来越强,也有多种专门的大规模集成电路可供选择。

1 数字钟的基本组成及工作原理

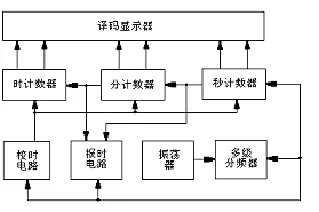

要想构成数字钟,首先应有一个能自动产生稳定的标准时间脉冲信号的信号源。还需要有一个使高频脉冲信号变成适合于计时的低频脉冲信号的分频器电路,即频率为1Hz的“秒脉冲”信号。经过分频器输出的秒脉冲信号到计数器中进行计数。由于计时的规律是:60秒=1分,60分=1小时,24小时=1天,这就需要分别设计60进制和24进制的计数器(或12进制的计数器,并发出驱动AM、PM的标志信号)。各计数器输出的信号经译码器/驱动器送到数字显示器对应的笔划段,使得 “时”、“分”、“秒”得以数字显示。数字钟的结构框图如图1所示。

图1 数字钟结构框图

2 振荡器的设计

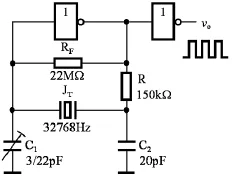

振荡器主要用来产生时间标准信号。数字钟的精度,主要取决于时间标准信号的频率及其稳定度,所以要产生稳定的时标信号,一般采用石英晶体振荡器。从数字钟的精度考虑,晶振频率愈高,钟表的计时准确度就愈高。但这会使振荡器的耗电量增大,分频器的级数也要增多。在确定频率时应当考虑这两方面的因素。我们选用了成型数字钟中使用的石英晶体频率f0=32768KHz。因其易购买、体积小、成本低。采用RC振荡器,该振荡器是由石英晶体、电阻、电容组成,其电路如图2所示。

图2 石英晶体振荡器电路

3 分频器的设计

分频器能将高频脉冲变换为低频脉冲,它可由触发器以及计数器来完成。由于一个触发器就是一个二分频,N个触发器就是2n个分频器。如果用计数器作分频器,就要按进制数进行分频。例如十进制计数器就是十分频器,M进制计数器就为M分频器。

若从市场上购买到石英晶体振荡器其频率为 32768Hz,要想用该振荡器得到一个频率为1Hz的秒脉冲信号,就需要用分频器进行分频,分频器的个数为 215 = 32768Hz,N =15 即有15个分频器。这样就将一个频率为23768Hz的振荡信号降低为1Hz的计时信号,这样就满足了计时规律的需求:60秒=1分钟,60分=1小时,24小时=1天。分频器可用JK触发器或计数器构成。

4 时分秒计数器的设计

有了“秒”信号,则可根据60秒为1分,60分为1小时,24小时为1天的进制,分别选定“秒”、“分”、“时”的计数器。在“秒”计数器中,因为是60进制,即有60个“秒”信号,才能输出一个“分”进位信号。若用十进制数表示需要两位十进制的数(个位和十位),这样,“秒”个位应是十进制,“秒”十位应是六进制,符合人们计数的习惯。将来便于应用8421码译码显示电路,“秒”计数器中通常用两个十进制计数器的集成片组成,然后再采用反馈归零的方法使“秒”十位变成六进制,以使个位、十位合起来实现60进制。

5 校时电路

当数字钟的指示同实际时间不相符时,必须予以校准,校时电路的基本原理如图3所示,即将“秒”信号直接引进“时”计数器,同时将“分”的计数器置0,让“时”计数器快速计数,在“时”的指示调到需要的数字后,再切断“秒”信号,校“分”电路也是按此方法让“秒”信号输入“分”计数器,同时让“秒”计数器置0。快速改变“分”的批示,并到等于需要的数字为止。校“秒”电路略有不同,选用的周期为0.5秒的脉冲信号,使“秒”计数比正常计“秒”快一倍,以便对准“秒”的数字。

图3 校时电路

6 译码显示电路

在数字系统中常常需要将测量或处理的结果直接显示成十进制数字。为此,需将以 BCD码表示的结果送到译码器电路进行译码,用它的输出去驱动显示器件。CD4511是BCD锁存/7段译码器/驱动器,可用它驱动数码管构成显示电路。

7 定时/报时控制电路的设计

定时/报时功能要求数字钟在指定的时刻发出信号,或驱动音响电路“闹时”;或对某装置的电源进行接通或断开“控制”。不管是闹时还是控制,都要求时间准确,即信号的开始时刻与持续时间必须满足规定的要求。其电路如图4所示。

图4 定时/报时控制电路

8 结束语

这种数字钟的结构简单,准确度高,成本低廉。在基本电路的基础上还可扩展其他的功能,如整点报时、触摸报时等。

[1]孙建三.数字电子技术.北京:机械工业出版社,2000.

[2]彭军.数字电路设计与制作.北京:科学出版社,1984.

[3]杨冰.数字电路设计与实践.武汉:华东师范大学出版社,1991.