基于Nios II处理器的视频字符叠加的设计与实现

熊 璟 ,刘 怡 ,唐 广 ,黄自力

(1.电子科技大学 电子工程学院,四川 成都 610054;2.西南技术物理研究所,四川 成都 610041)

责任编辑:任健男

1 引言

视频字符叠加就是通过一定电路产生字符或时间信号并与输入的视频信号进行叠加,使字符或时间在监示器的指定位置上与图像信号同时显示。用FPGA实现数字视频字符叠加不仅简化了电路结构,而且在现有成本的前提下充分利用了FPGA的资源[1]。它采用了参数化、模块化的设计方式,因此显示稳定;在显示格式、内容变动时容易修改。

Nios II是Altera公司开发的第二代可进行SoPC设计的RISC型处理器软核,具有高性能、参数可配置、可移植、可裁剪等特点,并且具有很高的灵活性、实用性,更能满足设计的要求。Nios II处理器可以通过AVALON接口采用“基地址+地址偏移量”的方式来访问某寄存器,从而实现对这个系统的控制。

笔者提出了一种基于Nios II的视频字符叠加实现的新方案,在Altera公司的Cyclone III系列的EP3C40F484I7器件上完成了硬件验证,用Nios II来替代串口的功能,给FPGA发送指令或数据以方便功能调试。该设计结合ADSP-BF561芯片,应用到某视频监控系统中。

2 设计框架

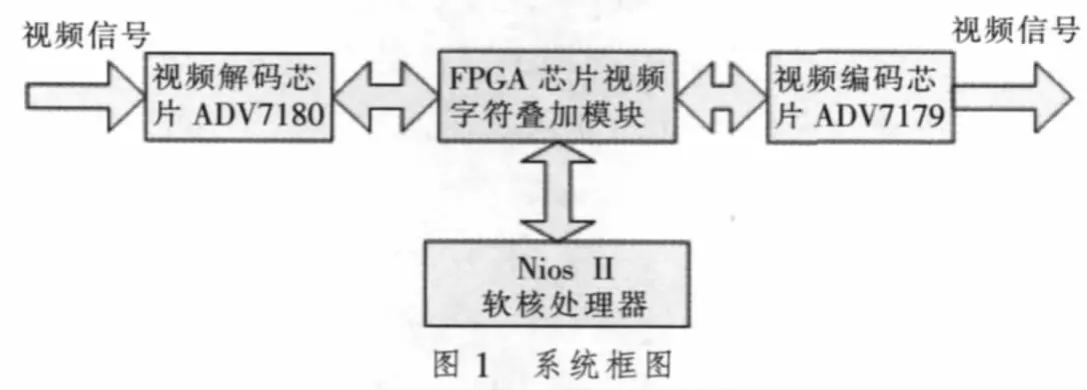

采用模块化进行设计,整个设计分为图像显示模块(包含视频字符叠加模块、图像十字中心线及波门跟踪框显示模块、ROM字符库生成等功能模块)、ADV7179和ADV7180的I2C实现、Nios II控制模块、时钟生成模块等几部分。其中,ADV7180是ADI公司生产的一款多格式SDTV解码芯片,可以支持包括NTSC,PAL以及SECAM电视格式,并将其转换为符合CCIR6564∶2∶2格式的视频数据,其并行数据输出与ADSP-BF561的PPI口通过2个通用I/O口采用I2C方式相连,接口电路简单,不需要外围器件,节省成本,增加了电路的可靠性。ADV7179是与视频解码芯片ADV7180相配套的单芯片PAL/NTSC视频编码芯片,用于ITU-RI BT601/BT656 YCrCb到PAL/NTSC的视频编码,采用3.3 V或2.8 V供电,可通过其接口I2C对芯片内部电路进行控制,并且每个DAC可以单独关闭,功耗极低,可以保证视频采集的质量和流畅性。ADV7180将模拟视频信号经处理后(8 bit)输出 720×576 的标准 CCIR6564∶2∶2数字信号,并产生相应的行、场同步信号HS和VS,以及与HS锁定的时钟信号LLC和LLC2。系统框图如图1所示。

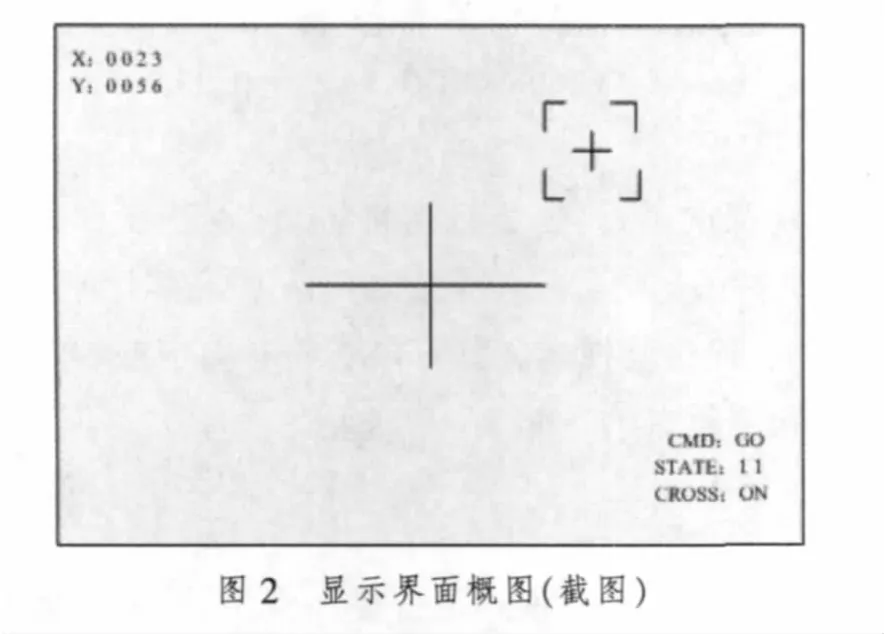

本设计采用的图像分辨力是720×576,图像采用隔行扫描方式。显示界面上所有字符字体为WST_Czec,字号为6号,大小为16×16。波门跟踪框和十字在图像上初始位置为360×288,波门跟踪框大小为128×128,小十字大小为32×32,大十字大小为200×200。显示界面如图2所示。

3 视频字符叠加各个功能模块的实现

图像显示模块的主要作用是利用视频行同步信号,在特定位置从FPGA的ROM中读出待叠加字符的信息,与视频信号叠加,产生有字符的视频信号。

对ADV7179和ADV7180的控制和I2C的实现,以及字符叠加功能的实现用Verilog编程实现。整个字符叠加功能的实现包括行/列计数器的生成、字符位置的确定、字符库的建立、查找地址、字符块显示模块、显示状态模块等。其中,行/列计数器由行/场信号决定;字符的位置由字符点阵大小、行/场信号和用户需求决定,图像中心十字线固定在图像中心位置,波门跟踪框位置由用户指令和跟踪坐标决定,参考图2的显示界面,本设计的特点是可以在视频的任意位置叠加字符和图像,内容变动时容易修改;由用户所给指令决定在某指令下各个字符和图像的显示或消隐,如果用户给出跟踪状态指令时要求不显示图像中心十字线、显示波门跟踪框和跟踪坐标及相应状态字符,就将图像中心十字线输出为输入视频信号,而其他待显示内容的相应位置为0xff时,就将其在图像上显示出来,其他位置则在图像上输出输入视频信号。

3.1 字符库的建立

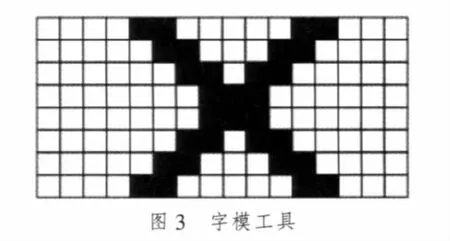

字符由16×8个像素构成,字符中的一个点对应显示屏的一个像素,由于本设计的图像扫描是隔行扫描方式,所以这样一个字符在屏幕上就是16×16个像素的阵列。因此,在屏幕上叠加字符就是把相应的像素叠加到指定的位置。本设计利用字模生成工具suki_v5.0来构造各个16×8点阵字符,以字母X为例,其中黑点代表二进制中的“1”,白点代表“0”,如图 3所示。用 16 bit表示该字符即为 0x0C18,0x0630,0x0360,0x01C0,0x01C0,0x0360,0x0630,0x0C18。

将各个字符用字模生成工具构造,在Quartus II的环境下,调用一个大小为16 bit×256 words ROM IP核,并建立一个字符库的.mif存储文件用来存放各个字符的数据,如图4所示。

3.2 字符块显示及查找地址功能的实现

由于字符的点阵值反映的是屏幕上被二值化后的某一点是亮还是暗的信息,而显示时需要的数据是某点的灰度级数,所以从字符里读出的每1 bit均需转化成0x00或0xff。每个字符的信息在显示时是一行一行读取的,并且视频信号的扫描方式是隔行扫描。每场图像在要叠加字符的行从ROM中读取字符信息,叠加允许位置为“1”,ROM中的数据为“0”,则直接输出视频信号;ROM中的数据为“1”,则输出相关的颜色信号。叠加允许位置为“0”,不读取ROM中的数据,直接输出视频信号[2]。这种方法的优点是各个字符是并行调用ROM,速度快,但占用ROM资源多;如果资源有限,且对其速度没有特别要求,可以采用以速度换面积的思想,用一个多路选择器,将所有要实现的字符的地址、位置作为选择条件,只调用一次ROM,面积减少了,但会增加一些复杂的组合逻辑,降低系统的工作频率。其主要思路是:基于每个字符显示位置的固定性及每个字符显示大小的固定和同一性,行列时钟计数器在某一范围便是某一字符的有效域,从而赋予某一值以确定读取的是第几个字符的点阵信息[3]。

另外,如果字符是数字,比如是4位十进制数abcd,而字符库里只存有0~9这10个数字,对其按式(1)进行一些简单的处理即可

如果是4位十六进制数,只须将其依次移位,或用d={4’b0,abcd[3:0]}描述即可实现每一位,并在ROM上找到每一位对应的地址。本设计为了方便查找地址,分别用0~9查找字符0~9的地址, 用a~f查找字符 a~f的地址,其他字符依次排序。

3.3 视频图像数据输出

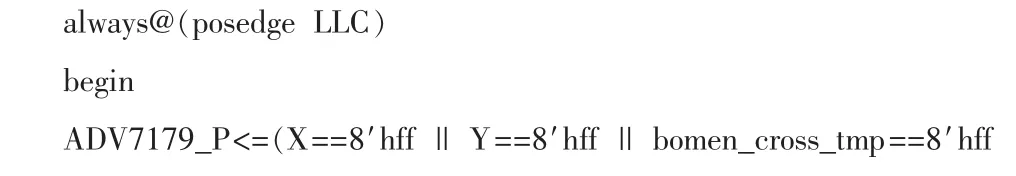

本设计采用的视频ADV7180_P输入数据信号是16 bit,但有效信号是8 bit,故将其有效位引出转换为8 bit数据信号 ADV7180_TEM,即 ADV7180_TEM={ADV7180_P[15:9],ADV7180_P[7]},输出视频数据信号ADV7179_P也是8 bit。本设计选用或(OR)门来实现视频数据输出,而不用IF-ELSE风格。因为选用后者在符合某行某列或是某区域时将此字符显示出来,会使有些字符或图像重叠。而使用或门就可以简单地解决这一问题,并使程序显得简洁不冗长。程序如下:

4 Nios II控制模块

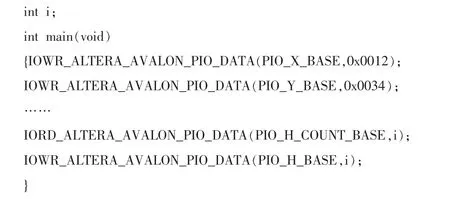

本设计利用Nios II的灵活性,将视频叠加字符模块中由用户给出的指令和参数引出来,在SoPC Builder[4]生成一个Nios II processor,并且添加On_chip_ram和PIO等模块,设置参数,并在工程顶层文件实例化所生成的CPU核,完成相当于与DSP通信的串口工作,这样就可以跳过DSP程序直接完成FPGA视频字符叠加的功能实现,方便又快捷。原本应由DSP在某约定地址写给FPGA的数据包括x,y坐标,状态信息,命令和显示状态等,现在均可在Nios II 8.1 IDE的编译环境中通过编写程序直接给PIO口定义的变量赋值实现。代码如下:

搭建调试平台,连接摄像机、硬件电路板和监视器(显示屏幕)等,将程序下载到FPGA中,在线调试字符叠加功能,通过监视器屏幕可以看到对应当前状态的视频图像和字符显示。

5 小结

笔者设计了一种视频字符叠加模块,并成功地基于Nios II对其进行控制、调试。设计中增加了电路的面积,但避免了复杂的组合逻辑,提高了系统的工作效率。

[1]孙涨波,顾红,苏为民.视频字符叠加技术的发展及四种实现方案[J]. 电子技术应用,2001(11):44-46.

[2]宋承杰,王景存.基于FPGA的视频字符叠加的设计与实现[J].电视技术,2009,33(12):24-27.

[3]刘桂芬,张长明,高升久,等.基于FPGA的视频字符叠加设计及其实现[J]. 国外电子元器件,2005(11):7-10.

[4]周立功.SoPC嵌入式系统基础教程[M].北京:北京航空航天大学出版社,2006.