基于FPGA的数字Costas环的设计与实现

吴仁彪,汪万维,胡铁乔,钟伦珑

(中国民航大学天津市智能信号与图像处理重点实验室,天津 300300)

扩频通信系统大多采用数字调制技术,其属于载波抑制系统。所谓载波抑制系统是指没有连续波环可跟踪残留载波分量的系统。对抑制载波信号进行跟踪通常需要采用一些特殊的锁相环路,常见的有平方环、同向-正交环(Costas环)、判决反馈环和通用载波恢复环等。Riter已经证明[1],跟踪低信噪比的抑制载波信号的最佳装置是Costas环和平方环,Holmes,J.K已经证明这两种环路是等效的[2],即有着相同的随机微积分方程。由于平方环自身的特点,载波提取需要在高频带上进行处理,这样势必会给环路的电路制作和调试带来一定的麻烦。

故对于扩频通信系统中的BPSK调制信号来说,一般均采用Costas环进行载波跟踪。由于笔者所从事的工程项目中接收的信号正好是BPSK调制信号,故采用之。

1 Costas环的基本原理

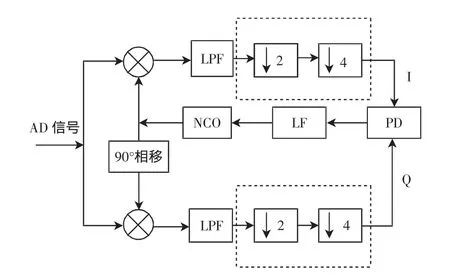

Costas环主要由NCO(数控振荡器)、LPF(低通滤波器)、PD(鉴相器)及环路滤波器(LF)组成。为了降低噪声对环路系统的影响,降低FPGA芯片的功耗,本文对环路数据依次进行了2倍移位抽取和4倍抽取,其原理结构如图1所示。

图1 数字Costas环结构图Fig.1 Structure chart of Costas

设输入的BPSK直扩序列扩频信号为

本地NCO的同向与正交支路的输出分别为

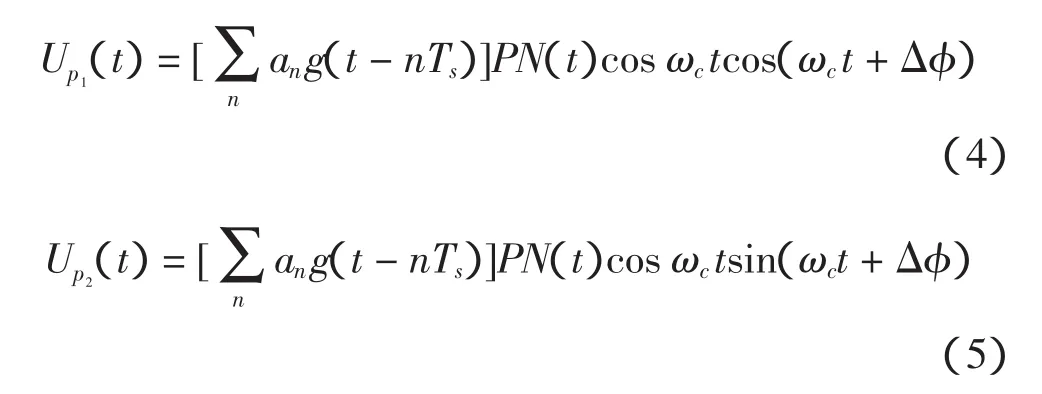

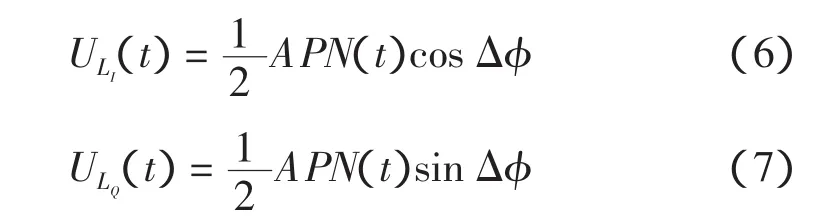

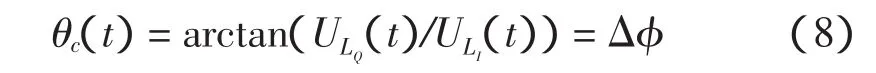

其中,Δφ为输入信号和本地NCO信号的瞬时相位差,则同向、正交支路与输入BPSK信号通过乘法器相乘后的两路输出分别为

经过LPF滤除高频分量后,可得到

其中,A为低通滤波器带来的常数增益。PD采用求反正切值的方式,其输出为

式(8)表明,NCO的输入是受Δφ控制的,环路滤波器输出为跟踪Δφ提供了所需的误差控制电压。Costas环路尚未锁定之时,θe(t)控制NCO的频率、相位,不断向减小跟踪误差的方向调整,直至跟踪上输入信号的载波频率。环路锁定后,Δφ很小,故从同向或正交支路可获得解调信息。

2 数字Costas环功能部件及参数设计

在笔者所从事的工程项目中,硬件平台采用成都傅里叶公司生产的FFT-SDR-V4软件无线电处理平台,FPGA芯片为Xilinx Virtex-4,集成开发环境为Xilinx ISE8.2i,开发语言为Verilog。试验数据为从一段正弦波抽取若干点,经过扩频后再经过BPSK调制的50 MHz中频信号,经过处理平台40 MHzA/D采样后载频变为10 MHz,SNR=35 dB。环路各模块工作的时钟频率为20 MHz。

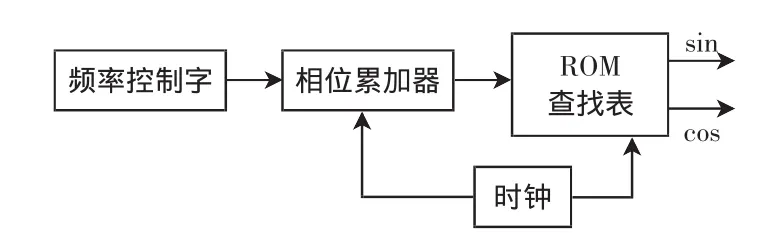

2.1 NCO设计

本地NCO采用DDS原理设计,DDS(直接数字频率合成)是一种新的频率合成技术,具有频率分辨率高、频率转换速度快且相位连续、输出信号精度高等优点。其结构如图2所示:

图2 NCO结构图Fig.2 Structure chart of NCO

具体实现采用ISE8.2i自带IP Core。输入数据位宽为32位,输出数据位宽为8位。由于使用1个通道进行相位累加,故地址控制字为00000,相位累加器位宽为32位,故NCO的频率分辨率为0.009 Hz。频率控制字计算如下

其中,fout=10 MHz为NCO的输出频率,N=32为累加器位宽,fclk=40 MHz为输入参考时钟频率,故Δθ′=1 073 741 824。本文使用可编程NCO,通过可变频率控制字跟踪输入信号的载波频率,故NCO最终的频率控制字为Δθ=Δθ′+Δφ(Δφ为鉴相结果)。

2.2 乘法器设计

主要完成输入AD信号与NCO输出的两路正交信号相乘,如式(4)和式(5)所示,为低通滤波和鉴相作准备。具体实现采用ISE8.2i自带IP Core。该乘法器为有符号乘法器,且是一级流水。一个输入是14位,另一个输入是8位,输出为22位。为了降低运算量,将输出结果截取为14位,且截取位可控。

2.3 LPF设计

主要滤除高频分量和带外噪声,最后得到如式(6)和式(7)结果。具体实现采用集成开发环境XilinxY ISE8.2i自带FIR滤波器 IP Core。滤波器系数由Matlab仿真生成后载入IP核,系数位宽为16位,大小为[-159,-53,727,572,-1 783,-1 999,5 066,14 148,14 148,5 066,-1 999,-1 783,572,727,-53,-159],阶数为16阶。滤波器输出数据可由相关控制字控制其输出大小。

2.4 PD设计

根据式(6)、式(7)特点,一般采用相乘的方式得出 sin(2Δφ)的乘积项,再用 2Δφ 近似代替 sin(2Δφ)的方式实现鉴相。而本文根据上式特点,采用求其反正切值的方式直接求出鉴相误差,如式(8)所示,鉴相精度较高。具体硬件实现采用ISE8.2i自带反正切值IP Core。由于反正切值仅在第1、3象限内,因此硬件实现时采用相位校正,通过最高位符号判别确定修正量,将鉴相结果修正到[-π/2,π/2]之间。

2.5 LF设计

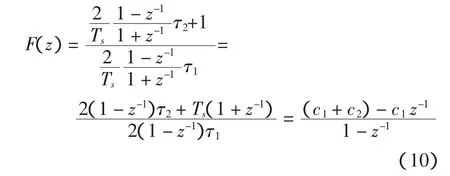

环路滤波器是一种具有低通特性的滤波器,其的主要作用就是抑制环路带外噪声,稳定环路的跟踪过程,而且对环路的捕获带宽和速度也有很大的影响,因此环路滤波器是数字锁相环设计中的一个非常重要的环节。二阶数字环路滤波器在直流增益为无穷大而频偏为常数的情况下,可以实现0稳态相位误差和频率误差,故使用之。

通过双线性变换,可得到二阶环路滤波器的数字域传递函数

式(10)中,c1、c2为滤波器的环路参数,对应环路滤波器的数字模型如图3所示。

图3 环路滤波器数字模式Fig.3 Digital pattern of loop filter

取环路固有频率ωn=2π×1 000,阻尼因数ξ=0.707,离散采样间隔 Ts=1/400 kHz,将 c1、c2左移 15位再取整得c1=719、c2=7,为了硬件实现方便,暂取c1=512、c2=8。

将以上各部分串联起来便组成了一个具体的锁相环路,如图4所示。其中的控制字说明如下:

图4 硬件实现过程Fig.4 Process of hardware implemention

dsp_config[31]:控制环路参数c2的大小。

dsp_config[30]:控制鉴相器的鉴相方式为反正切方式还是反余切方式。

dp_config[26:24]:3 位控制字,8 种工作方式,调整环路灵敏度。

phase_w:鉴相器的输出结果。

phase_com:经过相位校正后的输出结果。

phase_lf:经过环路滤波后的输出结果。

图1中的环路抽取通过一个3位计数器count_50控制实现,同时count_50还为各个模块预留充足的数据处理时间。当count_50=0时,鉴相数据I_dat和Q_dat的最高位分别进行两次移位寄存,当count_50=4时,对鉴相结果进行相位校正;当count_50=5、6时,进行环路滤波。整个处理过程,既保证各个模块有充足的数据处理时间,又对环路数据进行了8倍抽取,使环路的数据率降为5 Mbps。

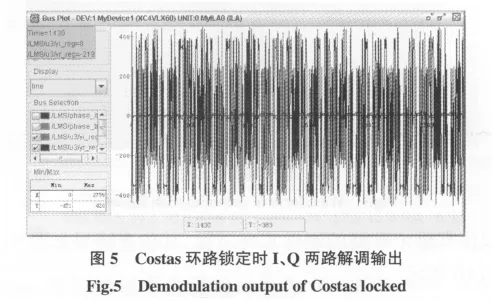

3 ChipScope Pro观测FPGA内部信号

用于同步的数据长度为16 384 bit,工作时钟为20 MHz,故环路能在819us时间内完成锁定。当环路锁定后,很小,由式(6)和式(7)可知,I路解调输出结果应该远远大于Q路解调输出结果。使用ChipScope Pro在线、实时读出FPGA内部的I、Q两路信号,在笔者从事的工程项目中,如果环路锁定,则接收端亦能稳定解调出发射端的信号。图5为使用ChipScope Pro观察I、Q两路信号的结果。

图5中幅度较高的包络表示I路信号,幅度较低的包络表示Q路信号,I路输出远远大于Q路输出,图6显示环路未锁定时的情形。图7中幅度较低的曲线表示phase_tmp引脚输出,幅度较高曲线表示引脚phase_lf输出,具体引脚含义如图4所示,两路输出鉴相误差接近于0。为了进一步验证解调是否正确,将解调后的0中频信号再调制至40 M,用示波器观察其输出波形,由图8可知,输出波形稳定且与发射信号波形一致,表明锁相环路锁定,且工作稳定。

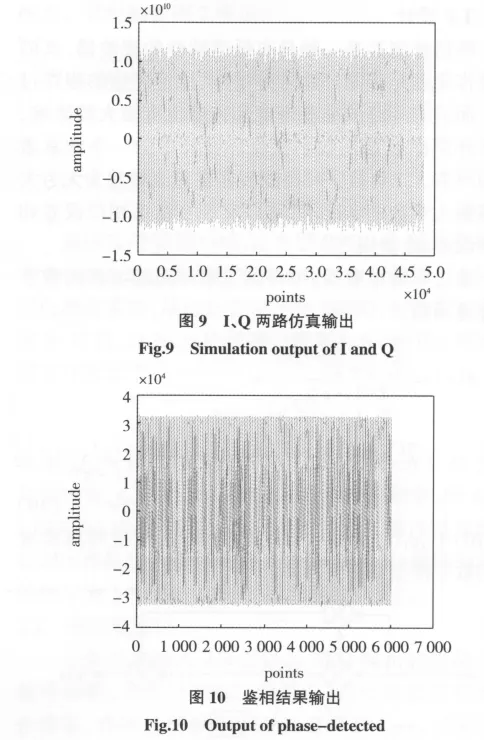

为了验证环路设计的正确性,本文还用Matlab模拟仿真整个环路的硬件实现过程,其仿真结果如图9、图10所示。

由图9可知,I路输出结果远大于Q路输出结果,由图10可知,环路滤波器输出包络稳定,表明鉴相误差已经收敛,环路锁定。由于Matlab仿真没有进行位截取,故其输出值远大于实际硬件实现值,从而证明硬件设计的正确性。

4 结语

本文采用求反正切值的方式进行鉴相,鉴相精度高。各主要模块主要采用ISE8.2i中自带IP core实现,一方面具体硬件实现时简单方便,另一方面,由于FPGA的可重配置性,使得采用FPGA设计十分灵活,根据锁定情况随时修改环路参数,以达到最佳锁定效果。试验结果表明,该锁相环路设计合理。

[1]RITER S.An optimum phase reference detector for fully modulated phase shift keyed signals[J].IEEE AES-5,1969,4(7):627-631.

[2]HOLMES J K.Coherent Spread Spectrum Systems[M].New York:John Wiley&Sons,1982.

[3]张 欣.扩频通信数字基带信号处理算法及其VLSI实现[M].北京:科学出版社,2004.

[4]林海都,高强.基于FPGA的全数字Costas环的设计与实现[J].嵌入式技术,2007(10):34-36.

[5]薛小刚,葛毅敏.Xilinx ISE 9.x FPGA/CPLD设计指南[M].北京:人民邮电出版社,2007.

[6]熊小莉.直接序列扩频信号数字科斯塔斯环的分析与设计[J].电视技术,2001(4):26-30.

[7]李 波,李玉柏,彭启琮.在FPGA中用costas环实现载波同步和数字下变频[J].广东通信技术,2006(3):66-70.

[8]张安安,杜 勇,韩方景.全数字Costas环在FPGA上的设计与实现[J].电子工程师,2006,32(1):18-20.

[9]庞 浩,王赞基.一种基于FPGA实现的全数字锁相环[J].自动化与仪器仪表,2005(5):28-30.