多功能数据采集处理系统实现

赵 磊

引言

数据采集与处理系统的设计是现代信号处理系统的基础,被广泛应用于雷达、通信、图像处理等领域。近年来,随着信息科学的高速发展,人们面临的信号处理任务越来越繁重,对实时信号数据采集处理系统的要求也越来越高。所用系统要求具有处理大量高速数据的能力,这就要求系统硬件达到很高的运算速度,并且软件处理程序也尽可能优化,以保证系统的实时性。同时,伴随着电子产品应用的多样化,电路设计的通用性也受到了大家的重视。

器件选型

A/D采样芯片

凌力尔特(Linear)的LTC2260是一种14 bit ADC,它具有105 Msps的采样率,功耗仅为106m,显著减少了用于高速数据采集的功率预算,同时集成有高性能采样保持电路,提供CMOS兼容的输出,输入信号和采样时钟均支持差分模式。LTC2260具有以下特点:信噪比73.4dB,无杂散动态范围85dB,单1.8V电源,满功率带宽800MHz,CMOS、DDR CMOS或DDR LVDS输出,可选输入范围1VP-P至2VP-P。

FPGA

在FPGA的选型中,通过对算法所需资源的估算和充分考虑器件的适用性,选用Altera公司StratixⅢ系列的EP3SE260。

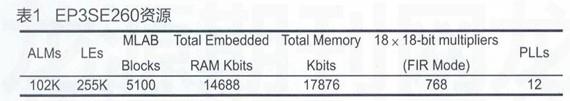

StratixⅢ拥有功能强大的DSP模块,速度高达550MHz,具有896个18×18的乘法器,支持可变位宽,支持基本乘法器、求和、累加、级联、取整、饱和以及桶形移位寄存器等功能。EP3SE260资源如表1所示。

DSP

本设计中DSP选用ADI公司的新一代ADSP TS201s数字信号处理器,兼有FPGA和ASlC信号处理性能和指令集处理器的高度可编程性,适用于大存储量、高性能、高速度的信号处理领域。ADSP TS201S采用超级哈佛结构,静态超标量操作适合多处理器模式运算,可直接构成分布式并行系统和共享存储式系统,专为大的信号处理任务和通信结构优化。

硬件电路设计

本系统中设计了四路A/D,采样后的数字信号送到FPGA进行预处理,FPGA同时为系统提供时钟、对A/D和D/A进行控制、与DSP进行数据交换、还要为CPCI接口的实现提供时序逻辑和通信接口,DSP做相应的算法处理,四路D/A可提供测试信号和自检信号,系统结构框图如图1所示。

A/D电路

高速A/D芯片的输入端通常采用差分输入,这种方式有以下优点:差分特性对来自电源和其他电路的外部共模噪声源具有抑制作用;能够抵消偶次谐波;每个差分输入所需电压摆幅仅为单端输入时的50%。可以降低对电源的要求。

本设计中运放采用的是ADI公司的AD8138,体积非常小巧,使得A/D芯片与信号输入点的距离可以很近,大大减少了外界噪声的影响,是理想的驱动芯片。单端转差分器件选用Mini-Circuits公司的宽带变压器ADT1-1WT,其工作频带为0.4~800MHz,配合简单的电阻网络及滤波电容就可以完成设计任务了。

LTC2260的工作时钟由FPGA提供,输出1.8V的并行数据到FPGA进行处理,FPGA采用2.5V的I/O电压。

FPGA和DSP的设计

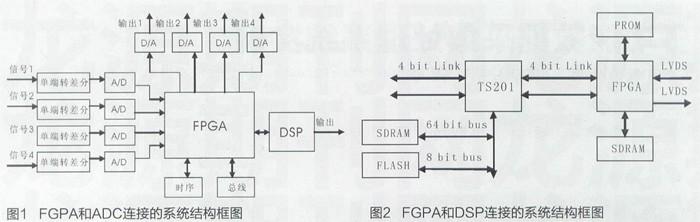

本系统采用松耦合结构设计,FPGA和DSP都有其各自独立的存储器,DSP和FPGA之间通过LINK进行互连,DSP与FPGA之间通信通过编写FPGA仿TS201 Lib/K逻辑完成,DSP还可通过LINK与外部交换数据,系统结构框图如图2所示。这种连接方式的优点在于:

(1)DSP和EIFPGA片间数据交换数据率更高,最高可达4GB/s;

(2)DSP和FGPA可以同时访问各自的外部存储器,系统总的存储带宽较大;

(3)DSP和FPGA访问外部存储器的同时可以通过LINK链路进行数传通信;

(4)系统硬件连线相对独立,易实现。

FPGA接口设计

FPGA主要提供3个逻辑接口,分别为与DSP的LINK接口、外部存储器sDRAM的接口以及系统的输入输出接口。与DSP的LINK接口采用IP核设计实现,接口能够稳定工作在500MHz速度上,为FPGA和DDSP之间提供4GB/s的数据传输能力。

FPGA到SDRAM接口逻辑自行设计,与DSP外部存储器相同采用4片K4SS11632M构成64bit的256MB存储空间。接口工作在80MHz时钟频率,数据率为640MB/s。

FPGA的输入输出接口连接到系统外,因此采用LVDS协议来保证信号的稳定、准确传输,双向备提供32bit数据宽度,采用250MHz的板间传输频率,可以提供2GB/s的传输能力。

DSP总线接口设计

ADSP TS201外部总线支持多种不同的协议,并且可以通过编程进行配置。外部总线接口支持流水线协议,SDRAM协议和慢速设备协议。TS201可以采用流水线协议访问存储系统。另外TS201有片上的SDRAM控制器,支持与sDRAM的无缝连接。本设计中总线上的外设分别为SDRAM以及DSP加载程序的FLASH存储器。

TS201处理器的sDRAM接口,支持1024、512、256字的页面长度,通过对sDRCON寄存器的编程可实现页面长度的选择。同时sDRAM占用TS201的外部存储空间地址,通过/MSSD3~0来确定SDRAM的地址空间范围。本设计选用的sDRAM型号为K4S511632M,页面长度为s12字,将四片SDRAM拼接成64位的总线宽度,实现与TS201的无缝接口的2S6MB存储空间。

DSP进行运算除了其外部存储器外,还需要对其自身进行程序加载的BOOT FLASH。本设计中使用AT49BV321,设计中FLAsH的cE信号需要使用DSP的BMS和MSO相与后给入,这样才能保证可以通过DSP的外总线给FLASH进行在线编程。

系统应用

本文设计的高速数据采集与处理系统,借助上面介绍的硬件平台,可以完成通用的数据采集与处理,其中关键的问题就是后续的处理系统设计,即后续的信号处理系统完成的算法与功能。针对输入信号的不同以及高速数据采集与处理系统的用途,后续的信号处理算法也具有多样性。

数字下变频

对于接收通道送来的中频信号,由于本系统采用了10SMsps的采样率,故可以直接采样后进行下变频处理,如图3所示。数字下变频器的组成包括数字混频器、数字控制振荡器和低通

滤波器,全部可以在FPGA中实现,医为通过软件进行运算,乘法器和低通滤波器可以做到完全一致,解决了I、Q通道幅度不平衡的问题,数字下变频器的控制和修改也更加容易。

脉压

在雷达回波信号处理中,通常利用线性调频信号脉冲压缩技术来获得高的距离分辨率,它可以在保证雷达作用距离的情况下提高雷达的距离分辨率。数字脉冲压缩就是利用数字信号处理的方法来实现雷达信号的脉冲压缩,分为时域和频域两种实现方式。一般而言,对于小时宽带宽积信号,用时域脉压较好,可以用专用的FIR滤波器或FPGA设计实现;但对于大时宽带宽积信号,用频域脉压较好,一般采用FFT方法在频域实现。由于DSP芯片具有很强的数据处理能力,完全能够满足雷达脉冲压缩信号处理实时性的需求。

动目标检测(MTD)

MTD是根据最佳滤波器理论发展起来的一种雷达信号处理技术。MTD滤波器是一组相邻且部分重叠的窄带滤波器组,覆盖整个重复频率的范围。由于固定杂波和运动目标回波的多谱勒频移不相同,利用多谱勒滤波器滤去固定杂波而取出运动目标的回波,就可以大大改善在杂波背景下检测运动目标的能力。采用加权法的每个滤波器具有较低的副瓣,可以抑制运动杂波,还有在零频附近的深凹口抑制固定杂波,具有较好的杂波抑制性能。MTD利用DSP内部的FFT运算实现相参积累,不但提高了系统输出的信噪比,还增强了雷达在各种杂波以及干扰条件下的目标检测能力。

上面举了一些应用方面的例子,诸如MTI、CFAR、积累、求模以及目标录取之类的应用,在本系统中也可以轻松地实现。

结语

本文提出了一种基于FPGA和DSP的高速数据采集处理系统设计方案。该设计具有一定的通用性和可扩展性,FPGA可完成高速数据的存储与相应的数据预处理,为DSP分担部分信号处理工作,且硬件实现速度快于DSP的数据处理;采用浮点DSP进行后续处理,提高了数据处理精度。该高速数据采集处理系统可以通过修改FPGA内部程序来实现其它功能扩展,并利用后续DsP的强大实时处理能力,完成更为复杂的数字信号处理,因此在工程应用上具有较强的通用性。

Tota IPON解决方案,适应多标准、多规范的电信市场应用

近日在北京举办的中国光网络研讨会上,PMC-Sierra&司带来的TotalPON产品是为电信领域提供的一种完整解决方案。TotalPON是一款单芯片产品,只需一颗芯片、一款软件,就可实现不同的PON标准,即目前市场上存在的两套标准GPON和EPON,以及PON的下一代标准10GEPON和XGPON。因为这些标准实际上存在很多共性,不论是标准层面还是物理层上,以及相应的一些应用。同时在实施层面上,单就线卡而言,GPON和EPON也有很多相似的地方,如都有相应的处理器、交换器,不同的只是PON在光模块这方面的差别,而这方面比较容易解决,因为都是可插拔的,这样就诞生了TotalPON。