基于FPGA的应答器上传链路FSK数字信号解调

田海燕

(沈阳铁路信号工厂,沈阳 110025)

1 概述

随着应答器设备在铁路系统的大量应用,应答器设备作为地对车信息传递的载体起到了重要作用。应答器设备具有信息传输速率高、信息量大、实时性强等特点,目前已成为铁路既有线提速以及高速新线建设的重要设备。

应答器设备采用电磁感应技术,车载主机通过机车天线连续向地面辐射能量,当机车驶过地面应答器时,地面无源应答器得到能量并启动工作。地面数据通过无线方式以FSK信号传向机车,机车天线接收到地面信号后经过车载主机解调译码,最后将数据信息传送给安全计算机。

FSK信号必须经过解调后才能通过解码单元解析。本文提出1种利用现场可编程门阵列(FPGA)对FSK信号进行解调的方案。

FSK:频移键控,就是用数字信号去调制载波的频率。FSK信号具有抗干扰能力强、传输距离远等优点,在日常生活和工业控制中被广泛采用。例如铁路系统和电力系统的载波通信中,也广泛使用其传送各种控制信息。

本设计中利用可靠性较高的FPGA芯片进行FSK信号的解调,用硬件描述语言智能分析FSK信号,从而满足比较高的频偏范围和高频解调要求,实现实时、稳定的FSK信号解调,具有解调电路简单、可靠性高、使用器件少、调试工作量小的特点。

2 系统结构

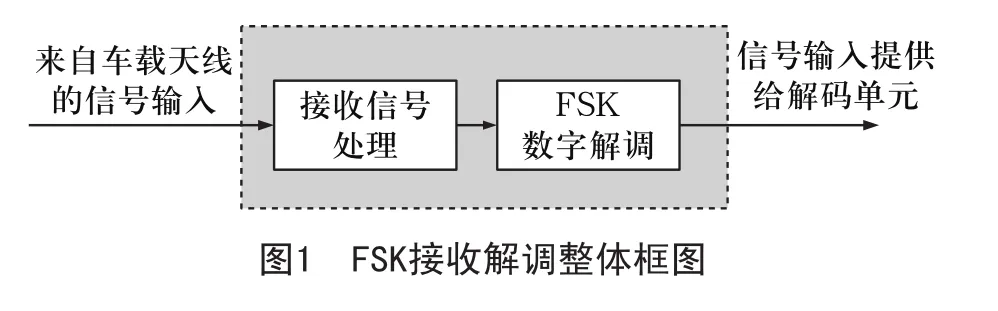

由车载天线接收到的信号,经过前期信号处理后,把FSK数字信号传送给FPGA进行数字解调,如图1所示。

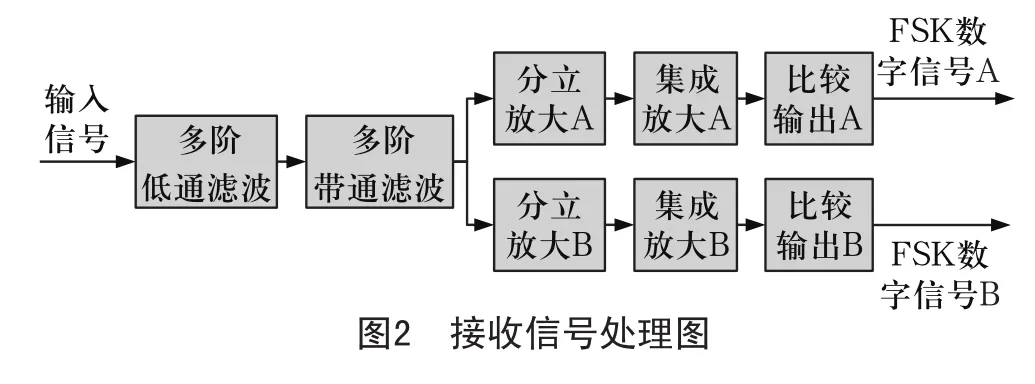

接收信号处理主要是对接收的信号进行滤波、放大等处理,形成FPGA可以识别的数字信号,可以对27.095 MHz能量信号进行隔离,对FSK信号进行选通放大,如图2所示。

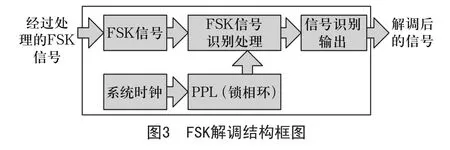

本设计的数字解调部分采用Altera公司的FPGA芯片,系统时钟选用频率为27.095 MHz的外部有源钟振。FPGA芯片完成的数字解调部分的框图如图3 所示。

3 系统实现

欧洲标准应答器的载波频率为282.2 kHz,键频移控分别为3.951、4.515 MHz,数据传输频率为564.48 kHz。根据A接口要求,中心频率为(fH+fL)/2=4.234 MHz±175 kHz,频率偏差为(fH+fL)/2=282.24 kHz±7%。

因此,在处理好基本解调的同时,还要在规定的频偏下实现解调。本文用硬件语言来实现对硬件电路偏差造成频偏的FSK信号的解调。

本文所介绍的解调为采样信号解调,因此采样频率必须足够高,这样可以明显区分两个频率的差异,以满足频偏要求。本系统采用钟振时钟27.095 MHz, PLL为8倍频。

整个处理过程为并行执行,即能实现FSK信号的实时采样。处理过程为采样到合法的信号时,进行片内存储,数据存储为双位存储(主要为满足频偏范围),当存储达到存储载频周期时间时,组合判断是否满足载频条件要求。此时处理采用延期1个采样周期处理形式,数据采样使用整体判断与逐个跳移判断结合,以便更好地进行数据采样分析。若合法(允许欧标条件要求偏差存在),则输出时钟和数据。当采样到非法频率(频偏超出欧标对FSK移频条件要求)时,抛弃采样信号,保证安全性。程序编写时,注意VHDL语言的使用,比如采样计数时,采用与或运算来代替简单的计数运算,以便更好地实现高频运行,防止时钟歪斜及抖动。二进制编码采用格雷码,以减少信号跳变,更好地解决高频下的毛刺和时钟抖动。对FSK信号的占空比要求仅为15%及以上,以减少硬件设计电路的设计难度,更好地满足硬件电路器件一致性和键频跳变特性。FSK信号识别处理原理如图4所示。

4 系统的实际应用及结果分析

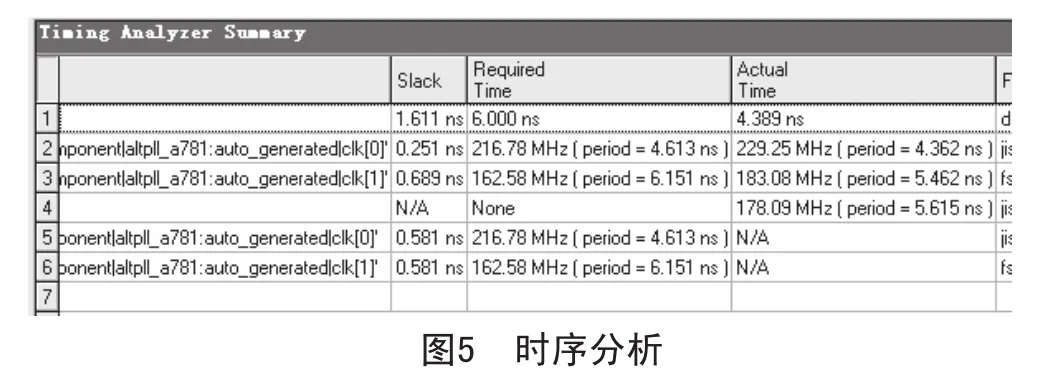

整个设计使用Altera公司的EP3C25E144I7芯片,在Quartus II软件平台上进行布局布线,时序约束。布线后时序分析如图5所示。

在图5中,采样信号频率实际为229.25 MHz,满足设计要求。

使用任意波形发生器输出FSK信号,频率为3.951 MHz,跳频为4.515 MHz,FSK信号速率为282.2 kHz,用Signal Tap观测,波形如图6所示。

用Signal Tap芯片内部观测,系统内部运行正常,符合设计思想,以下使用示波器观测实际输出波形。在以下波形图中,上排为输出CP,下排为TA。

将示波器设为小于最小观察量时间触发,观察波形如图7所示。

从图7可以看出,时钟周期和码元数据对照,满足设计要求。

调整任意波形发生器的FSK速率,可以观察到速率在260~300 kHz之间无明显差别,满足设计要求。

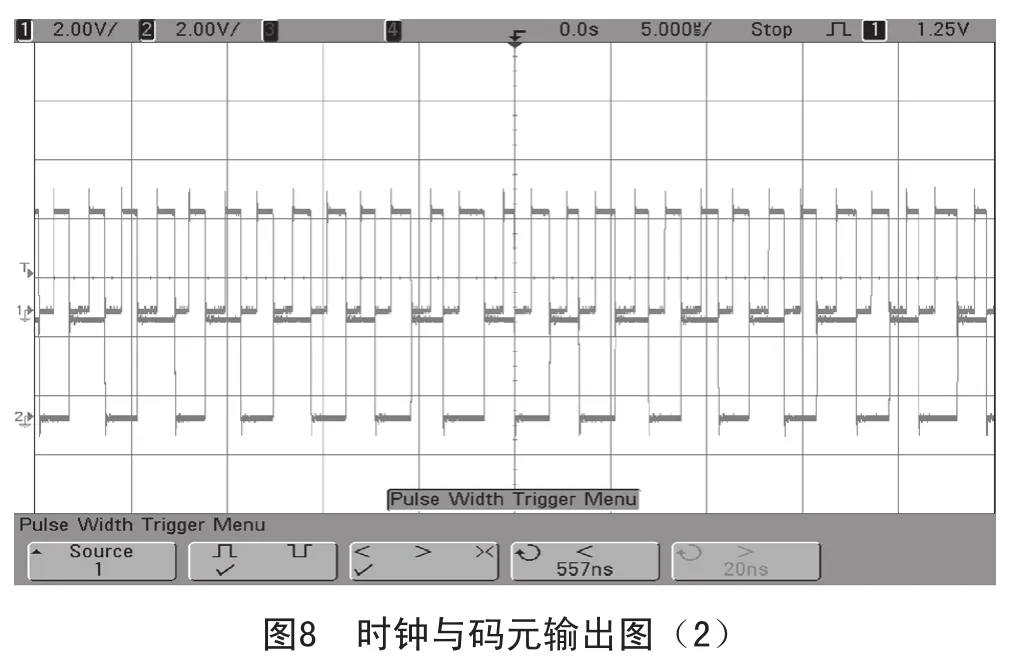

为了满足频偏范围,调整任意发生器的频率为4.126 MHz,跳频为4.691 MHz,观测示波器波形如图8所示。

从图8可以看出,无错码和丢码现象,满足设计要求。

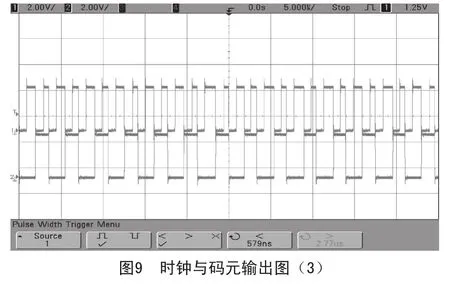

调整任意波形发生器的频率为3.776 MHz,跳频为4.346 MHz,观测示波器波形如图9所示。

从图9可以看出,无错码和丢码现象,满足设计要求。

调整任意波形发生器的频率为4.126 MHz,跳频为4.696 MHz,观测示波器波形如图10所示。

从图10可以看出,无错码和丢码现象,满足设计要求。

5 总结

使用FPGA来实现FSK解调,第一,考虑到实际接收到的FSK信号码元波形分为过渡区和稳定区,在解调时只使用码元稳定区中若干个载波周期内的采样值作解调判决,可以尽量减少误码率,以便在有限小的时间内,接收更多的有效位。第二,通过存储信息的智能判断,能够更好地识别高频FSK信号,并且可以减少硬件设计要求。第三,传统的FSK解调方式都是采用硬件电路实现,电路复杂,调试不便。文中采用硬件描述语言设计的基于FPGA解调,设计灵活,修改方便,有效减少了元器件的使用数量,增加了可靠性,同时系统采用VHDL语言进行设计,具有良好的可移植性及产品升级的系统性。第四,在工厂生产时,FPGA的解调比硬件解调电路省去了电路的调试,并且减少了加工工序,有利于工厂批量生产。

本方案已经在沈阳铁路信号工厂的应答器传输模块上使用,通过了实验室实验,FSK的解调良好,在应答器启动后,无错码和误码现象,完全满足产品设计要求。近期在武汉到襄樊线路350 km/h的运行条件下,接收庞巴迪应答器数据良好。各种实验和现场试用表明,使用FPGA芯片实现FSK解调,具有很大的优越性。

[1] FFFIS for Eurbalise SUBSET-036-v241 [S].2007.

[2] Test Specification for Eurobalise FFFIS SUBSET-085-v222 [S].2007.

[3] Altera Corporation.Development Tools Selector Guide,1999.

[4] 徐光辉,程东旭,黄如. 基于FPGA的嵌入式开发与应用[M],北京:电子工业出版社,2006.

[5] 褚振勇,翁木云.FPGA设计及应用[M].西安:西安电子科技大学出版社,2002.