一种高性能数字移相系统

邢燕,胡永辉

一种高性能数字移相系统

邢燕,胡永辉

(中国科学院国家授时中心,西安 710600)

阐述了一种用于时间同步系统的高性能数字移相系统的设计方案和实现过程,该系统采用直接数字合成(DDS)技术,其同步精度小于100 ns,移相精度可达5×10-10s,同时能够实现精度为10-6Hz的频率调节。该系统是为时间同步系统设计,并可广泛应用到军用、电力、通信等领域中。

移相;时间同步;直接数字合成(DDS)

时间同步系统的一个重要指标就是本地秒信号能够实现与标准秒的高精度同步,这就要求有一个可高精度移相的本地秒产生和保持系统。本文介绍的高性能数字移相系统就是专门为时间同步系统研制的高精度移相系统,它将原子频标输出的标准频率信号进行分频,产生标准的钟面信息(比如年、月、日、时、分、秒)、分脉冲信号(1 PPM)、秒脉冲信号(1 PPS),并可以通过调相的方式对本地的1 PPS进行移相,从而达到本地时间与国家标准时间或国际标准时间之间的同步,确保本地时间的准确度,同时还可以通过调频的方式对本地的频标进行校准,从而确保本地时间的准确度,达到守时的目的。

高性能数字移相系统的设计对时钟源有3个基本要求:1)频率、相位高精度;2)频率、相位高稳定度;3)频率、相位精确可调。现有的直接数字合成DDS(direct digital synthesis)技术是将先进的数字处理理论和方法引入信号合成领域的移相新技术,它结构简单,易于控制,具有频率、相位、幅度可精确控制的优势[1],适合应用于高精度移相系统之中。

考虑到实际的应用,该系统采用模块化设计,即可作为模块集成到时间同步系统中,也可以单独使用。它体积小、集成度高、对外接口简单,能够实现纳秒级的移相,在军用、电力、通信系统中有着广泛的应用。本文介绍了该系统的工作原理,给出了其设计方案和实现过程。

1 系统方案

系统采用单片机处理器作为控制核心,结合复杂可编程逻辑器件CPLD(complex programmable logic device)和高性能DDS芯片实现高精度移相和频率调节。系统主要运用了DDS相位连续和可以控制波形的初始相位的特性,它产生的本地秒信号经同步后,与标准时间信号的同步精度可达几十个纳秒;移相后,同步精度可达1~2 ns。其功能总框图如图1所示。

本地时间分频模块CPLD采用EPM7128芯片,对时钟信号采取计数的方式进行分频,EPM7128内部计数器计到某个阈值时输出宽度为10μs的秒信号,这个阀值根据需要可以被CPU更改。由于CPU可以修改这个阈值,所以输出的本地1 PPS信号就可以相对标准秒信号(同步秒)做±1s以内任意时间的移动(移相精度100 ns)。这种移相方式速度很快,但是无法满足高精度要求。

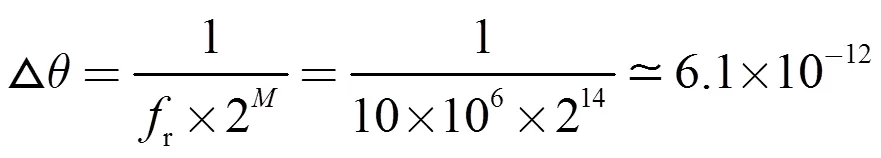

图1 系统总框图

精密移相系统中的DDS芯片AD9852内部有14 bit的相位偏置寄存器[2],CPU通过修改此寄存器的值,就可以改变AD9852输出的10 MHz时钟信号的初始相位。由于CPLD内部计数所使用的时钟是AD9852输出的10 MHz信号,所以AD9852输出的10 MHz信号相位的变化同时也改变了CPLD输出的本地1 PPS信号的相位,从而实现精密移相。由于系统采用了DDS芯片AD9852,因此在实现高精度移相的同时可达到的调频精度为10-6Hz,其稳定度与时钟源的稳定度一致。

CPU控制器响应EPM7128、AD9852、键盘和PC,并控制LCD显示。当串口或键盘有命令发出时,CPU对命令进行处理,并对EPM7128和AD9852进行相应的操作,同时刷新LCD的显示信息。

2 工作原理

AD9852对输入10 MHz时钟10倍频后作为内部时钟,因此其内部时钟为100 MHz。它的输出为两路相位始终相差π、频率为10 MHz的正弦信号[2],这两路正弦信号分别经过外部7阶椭圆滤波器后再送入AD9852的高速比较器,比较器的输出端就可以得到10 MHz的方波送到EPM7128。EPM7128对AD9852输出的10 MHz的方波信号进行分频,得到本地的1 PPS脉冲信号(就是本地秒信号)。

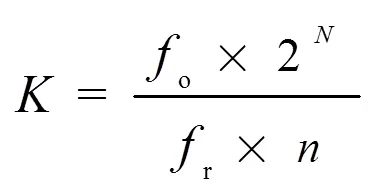

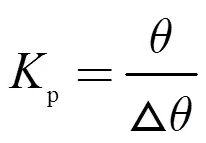

AD9852采用DDS技术,是一个全数字的开环系统。它的输出频率、相位和幅度可以精确地控制,在频率和相位调节过程中,输出相位是一个连续平稳的过渡过程。在外部参考频率不是精确的10 MHz时,可以通过修改频率寄存器的值来确保输出频率为精确的10 MHz。AD9852频率寄存器控制字的计算公式[3]如下:

3 系统设计

3.1 硬件设计

目前DDS技术多应用于频率合成和任意波形的产生,而本文介绍的高性能数字移相系统主要运用到了它可以控制波形的初始相位和相位连续的特性。虽然AD9852能实现输出1 PPS在±1 s以内的任意移相,但由于在移相过程中AD9852为避免相位突跳、保证输出相位稳定的10 MHz时钟信号,当移相数值越大时移相速度越慢。这样AD9852虽然实现了输出1 PPS在±1 s以内的任意移相,但相对速度较慢,特别是移相数值较大时,这个问题尤为突出。为了解决该问题,系统在硬件设计上采用CPLD和AD9852相结合的方式来实现移相,这样既保证了移相的精度又保证了移相的速度。

人机接口部分包括键盘和LCD显示,当有按键按下时,触发CPU外部中断,CPU在中断服务程序中读取键值。CPU每秒刷新钟面LCD一次,来更新钟面时间显示。系统每秒输出一个宽度为10μs的脉冲信号,同时输出一帧完整的时间信息,包括年、月、日、时、分、秒。此外,还可通过计算机串口发送命令的方式实现人机交互。

由表1可以发现,工程建设中,全过程造价管控具有深远意义,实施有效工程造价管控,在计划额内控制项目投资,提高资源分配率,特别是是利用造价管理有效协调施工各参与方,提高建筑项目管理的效益,以此为建筑企业创造更大的社会与经济效益。

高性能数字移相系统的稳定性和可靠性主要取决于系统参考时钟的性能,因此在硬件设计中对输入时钟做了相应的处理。时钟信号在接入数字移相系统前会有所衰减并受到干扰,因此设计中加入了放大和整型电路,以获得较好的频率特性和抗干扰能力。此外,硬件设计中还采取了以下措施来提高系统的性能:

1)数字地和模拟地采用一点共地,减少各个电路之间的相互耦合。

2)数字电源和模拟电源相互独立,减少电源之间的串扰。

3)电源部分采用了滤波电路,减少电源对系统的干扰;在电源和电源引脚附近加去耦或旁路电容。

3.2 软件设计

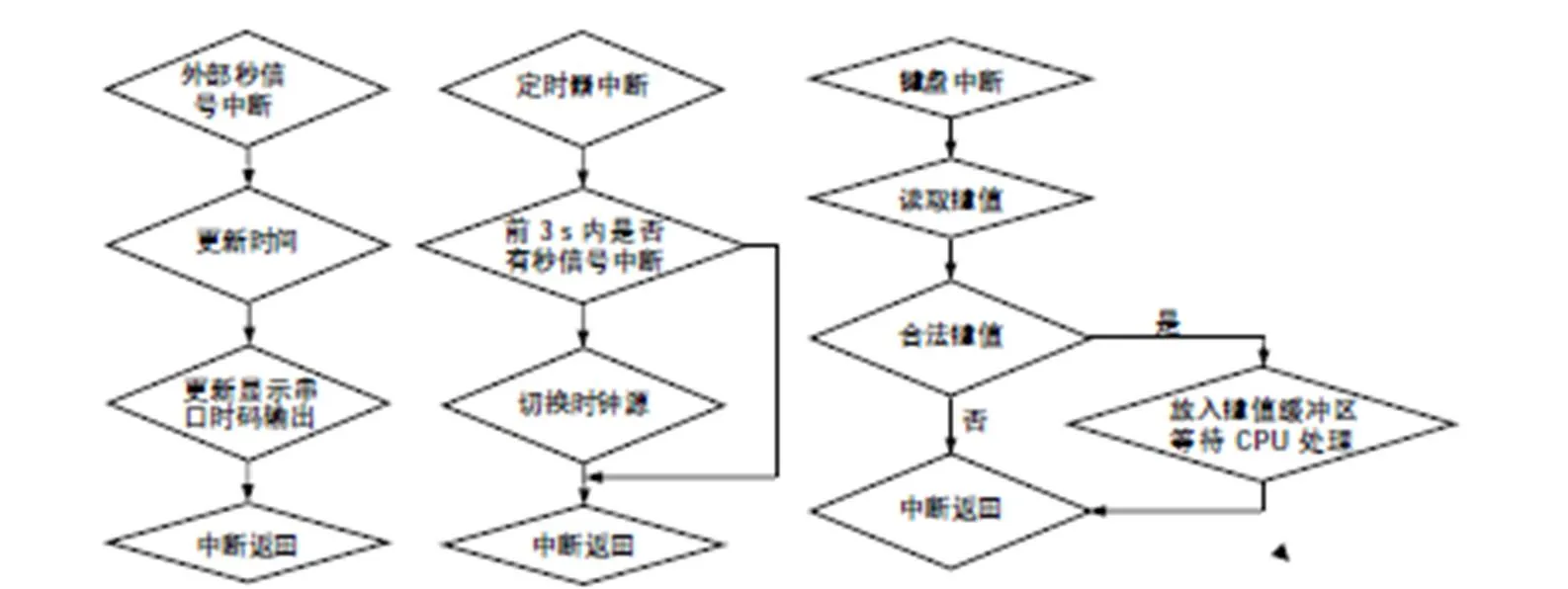

系统软件部分的工作主要包括:对系统进行初始化,响应键盘、PC机操作,显示LCD,串口接收和发送数据等。其软件流程如图2和图3所示。

作为系统的核心,CPU在上电或者复位后,首先进行系统初始化,初始化完成后,循环查询命令缓冲区是否有未执行的命令。命令接收是在中断服务程序中实现的,其中键盘操作命令是在外部中断服务程序中执行,每按下一个按键,CPU就将键值放入键值缓冲区,中断返回后由主程序判断当前键值缓冲区中是否有一个有效的命令帧。同样,CPU在接收到串口数据后,也把数据放入串口数据缓冲区,中断返回后由主程序执行相应的命令。

如果输入的命令合法,则将命令分解成不同的操作,分别发送给不同的执行单元。这些操作包括:

1)频率调节命令只发送给DDS芯片AD9852,由AD9852负责执行。

2)移相命令分解成两部分,大于100ns的部分发送给EPM7128执行,100ns以下的部分发送给AD9852执行。

3)初同步命令由CPLD执行。初同步可以使本地1 PPS与参考1 PPS之间的时间差小于100 ns。

4)对时间设置命令,由CPU直接将输入命令转换成时间信息,然后输出至LCD。

5)本地1 PPS连接到CPU的另一个外部中断输入端,在中断服务程序中,CPU对本地时间进行秒加一计算,然后把当前时间信息在LCD上显示,同时在串口输出。

图2 系统软件总流程图

图3 中断流程图

4 测试与结论

测试中,以中国科学院国家授时中心的频标作为高性能数字移相系统的时钟源,将其产生的1 PPS信号与国家授时中心的秒信号同步。开机后,将移相1 PPS与标准秒同步到1.5 ns左右,以标准秒作为开门信号,用SR620计数器采样比对结果[5],如图4所示。

图4 高性能数字移相系统输出1 PPS信号与中国科学院国家授时中心标准秒信号比对结果

图4给出了4个小时的测量数据,对数据分析后得出:高性能数字移相系统所产生的1 PPS信号的稳定性与时钟源的稳定性一致。当高性能数字移相系统用于时间同步系统中时,其小于100 ns的同步精度、5×10-10s的移相精度完全能够满足同步系统的要求,同时该系统可实现10-6Hz的频率调节精度。

整个系统以MCU处理器和CPLD作为开发平台,结合DDS技术和高性能的软硬件设计,保证了系统的性能指标。模块化的设计使得高性能数字移相系统能够很灵活地应用到不同的时间同步系统中,即可作为模块集成在时间同步系统中,也可作为单独的设备使用。当作为模块使用时,可通过串口对数字移相系统进行同步和移相;当作为单独的设备使用时,还可通过键盘对其进行操作。目前,它已经被应用到许多不同的时间同步系统中。

[1] 周林. 用AD9852与FPGA结合实现中频线性调相[J]. 电讯技术, 2002, 6: 72-75.

[2] Analog Devices Inc.Analog Devices AD9852 Data Sheet[Z]. [S.l]: [s.n], 1999.

[3] 潘炳松, 许明, 潘锦. DDS芯片AD9852及其应用[J]. 电子技术, 2002, 4: 46-48.

[4] 朱磊. DDS 芯片AD9852 的应用问题分析[J]. 电子器件, 2008, 31(4): 1141-1143.

[5] 刘春侠, 王改霞, 漆溢. 用于守时工作的时间间隔计数法与双混频时差测量比对法的比较[J]. 时间频率学报, 2007, 30(2): 111-117.

A High-precision Digital Phase-shift System

XING Yan, HU Yong-hui

(National Time Service Center, Chinese Academy of Sciences, Xi’an 710600, China)

The design and implementation of a high-performance digital phase-shift system based on DDS(direct digital synthesis) is introduced. For this system, the time synchronization precision is better than 100 ns, the phase-shifting accuracy is 5×10-10s, and the frequency-modulation precision is 10-6Hz. This system is designed for time synchronization system, and can also be used in martial system, electric system, communication system, etc.

phase-shift; time synchronization; direct digital synthesis (DDS)

2009-08-05

邢燕,女,硕士,工程师,主要从事时间用户系统终端设备的开发与研制的研究。

TN74

A

1674-0637(2010)01-0023-05