高速电路中的信号完整性及仿真

王寅

(电子科技大学自动化工程学院 四川成都 611731)

0 引言

现代的高速数字系统的时钟频率可能高达数百兆赫兹, 其高速变化的电平和极高的工作频率,以及很大的电路密集度,必将使得系统表现出与低速设计截然不同的行为, 出现了信号完整性(Signal Integrity)问题。信号完整性的破坏将直接导致信号失真、时序错误, 以及产生不正确的数据、地址和控制信号,从而造成系统误工作甚至导致系统崩溃,因此印刷电路板布线前和布线后的仿真显得非常重要。

1 信号完整性分析

信号完整性是指信号在信号线上的传输质量。信号具有良好的信号完整性是指信号在特定电路条件下,具有所必需达到的电压电平数值。差的信号完整性不是由某一单一因素导致的,而是板级设计中多种因素共同导致的。主要的信号完整性问题包括延迟、反射、振荡、电源噪声、串扰等。

1.1 延迟

信号在常见的FR4材料构成的PCB中的传输速度约为180ps/inch[1]。在高速信号中传输延时成为影响信号完整性不可忽略的因素,当信号在PCB走线上的传输延时超过芯片的最小建立和保持时间就会引起时序错误。传输延时受到走线长度,PCB介电质常数的影响。解决延迟问题的关键是尽量缩短信号从发送端到接收端的走线长度,对于时序相关的信号线走线长延时相差不能超过最小建立保持时间等。

1.2 反射

信号传输路径中阻抗发生变化时, 信号部分能量会被反射, 剩余的能量会继续传输。对于低速信号来说由于信号变化时间较长(一般在数十ns以上),信号在传输路径中每一点的电压可以认为是一致的。在高频电路中,当传输线长可能接近波长,不合适的终端匹配可能导致反射,引起逻辑问题或误触发。在高速PCB设计中反射来源于阻抗不匹配,意味着阻抗失配越大,反射就越大。衡量信号反射量的重要指标是反射系数,表示反射电压和原传输信号电压的比值。其定义为:。 其中:z1为变化前的阻抗,z2为变化后的阻抗。假设PCB线条的特性阻抗为25Ω,传输过程中遇到一个50Ω的电阻,若把电阻看成理想的纯电阻,那么反射系数为,信号有被反射回源端。如果传输信号的电压是3.3V电压,反射幅度就是1.1V。在实际布线中通常采用以下3个重要的措施[2]:使用可控阻抗的互连线;选择合理的布线拓扑结构;对传输线进行阻抗匹配。

1.3 串扰

串扰是指当信号在传输线上传播时,因电磁耦合作用对相邻传输线产生的不期望的电压噪声干扰,即能量从一网络耦合到临近一网络上,造成临近网络的信号在一定程度上的失真。串扰包括噪声电流和噪声电压,它们与噪声源信号的变化速率成正比:信号变化越快,即信号的上升/下降时间越短,则串扰的噪声越大。一般来说,串扰是通过电容耦合、电感耦合和辐射耦合3种途径产生。对于串扰,可以采取以下两种策略来抑制。一种方法是改变线路长度、线路之间的距离、电路板的分层位置等影响耦合的几何参量。另一种方法是利用终端,将单线改成多路耦合线。

1.4 电源地噪声

理想情况下我们认为电源是恒定不变的,实际上在系统中的电源和地经常受到外界和内部的噪声干扰使得电源表现出一定的波动会严重影响系统可靠性。抑制电源网络反弹噪声的影响,首先是设法减小电源的摆幅,可通过在布局时对系统进行分割,尽量减小系统中的各种电源之间的互相影响,如数字电模拟电源恰当的分区,用低速部分分隔高速部分和易受干扰的模拟部分,分割的目的是要重点保护高速部分。要抑制反弹另有一个方法是选择合适的位置放置去耦电容,摆放时要考虑不同电容的去耦半径,一般来说容量越小的越靠近电源和地引脚,加上适当的去耦电容能有效抑制电源和地线上的反弹噪声[6]。

1.5 振铃

如前所述,如果信号传输过程中阻抗发生变化,就会产生反射。这个信号可能是驱动端发出的信号,也可能是接收端反射回来的反射信号。信号在驱动端和接收端之间多次反射,其结果就是信号振铃。大多数芯片的输出阻抗都很低,如果输出阻抗小于PCB走线的特性阻抗,那么在没有源端端接的情况下,必然产生信号振铃。产生振铃的根本原因是由于阻抗不匹配,消除振铃首先要解决阻抗匹配问题[7]。

2 高速PCB设计的仿真分析

在传统的PCB设计流程中,PCB板的性能只有在制作完成后才能够通过仪器来测量评判其性能,采用传统的 PCB设计方法,由于在一个已有的PCB板上分析和发现信号完整性问题是一件非常困难的事情, 即使找到了问题, 在一个已成形的板上实施有效的解决办法也会花费大量时间和费用。

而应用了基于SI分析的高速 PCB设计后,能够在物理设计完成之前查找、发现问题并在电路设计过程中消除或减小信号完整性问题,在模型以及板级信号完整性分析正确的基础上,通常 PCB不需要或只需要很少的重复修改就能够最终定稿,从而可以缩短产品开发周期,降低开发成本。

本文中选择的仿真工具是Cadence Design Systems的 SpecctraQuest[6]。

3 高速PCB设计的仿真分析实例

以一块ARM9核心板为例,介绍SpecctraQuest仿真在高速电路设计中的应用, 系统的主芯片采用S3C2440芯片其外围有SDRAM、Flash等芯片。其中速度最高的是CPU和SDRAM之间的信号,因此保证SDRAM时钟的信号完整性将对整个系统的稳定性和性能产生重要影响。

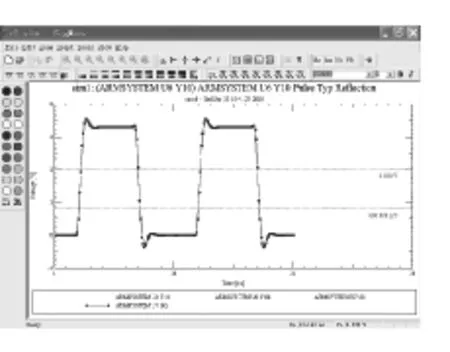

在第一版PCB设计中时钟信号从ARM引脚输出后直接连到SDRAM的时钟引脚,图1是通过SpecctraQuest从PCB文件中提取的CLOCK信号网络拓扑图。网络中U6为驱动端,U7为接收端。选择100MHz的激励源对这组对象进行仿真,可以得到如图2所示的仿真波形。

图1 第一版的电路拓扑结构图

图2 第一版的仿真结果

对仿真波形分析可以得出该信号在100MHz激励源下出现明显的过冲/下冲(Overshoot/Undershoot),过冲达到1.3V、下冲1.0V。由前分析可知信号的过冲/下冲是由于传输线的阻抗不匹配造成的。

解决阻抗匹配问题一般有两种端接方法:并联端接和串联端接。这里主要介绍串联端接法串行端接是通过在尽量靠近源端的位置串联一个电阻Rs(典型为10~75Ω) 来实现。此类端接法要求缓冲器阻抗和端接电阻值的总和等于传输线的特征阻抗。这种策略通过使源端反射系数为零从而抑制信号的反射。串行端接的优点在于: 每条线只需要一个端接电阻,无需与电源相连接,消耗功率小。当驱动高容性负载时可提供限流作用, 这种限流作用可以有助于减小地弹噪声。

图3是经过修改后的电路拓扑结构图。采用了串联源端接的方法,使用Cadence 仿真工具的扫描选择较好的阻值,在这里选用22Ω的电阻串联[3]。

图3 第二版的电路拓扑结构图

图4 第二版的仿真波形

图4 给出了阻抗匹配后电路的仿真结果,从图4可以看到仿真波形反射基本消除。信号的过冲降到了300mV以下,下冲幅度也小与400mV以下。

4 结束语

本文介绍了信号完整性的相关知识,通过EDA工具对一ARM核心板的布线后仿真,分析和解决了实际电路中由于阻抗不匹配引起的信号完整性问题。由此可见电路板级的仿真在高速PCB设计过程中对于解决信号完整性、电磁干扰、电源完整性等问题时是十分必要的。

[1]晁富邦,潘英俊,魏彪,解启瞻等.嵌入式ARM系统PCB设计中信号完整性的研究[J]. 电子测试,2008 (11):60-64.

[2]信号完整性:接收端容性负载的反射 [2009-04-21]http://sig007.com/bsjt/168.html.

[3]侯莹莹,胥佳.线形结构对差分传输线信号完整性的影响[J]. 电子测试, 2009(2): 1-5.

[4]张磊,唐继勇,杨峰. 高速电路中的信号完整性及仿真[j].中国测试技术,2008(3):63-66.

[5]沈惠敏. 基于信号完整性分析的高速数字电路仿真与验证[D].上海:上海交通大学,2009.

[6]Allegro PCB SI Tutorial[EB/OL][2009-05-01]http://www.cadencepcb.com/

[7]刘静.高速PCB 设计中的信号完整性分析及仿真策略[J]. 国内外机电一体化技术,2009(10):50-51.

[8]王守三. PCB的电磁兼容技术[M].北京:机械工业出版社, 2008:11-16.