F L E X 10 K的P S配置方式及E P C 2的应用

王新勇孙瑞利张利

(河南科技大学电子信息工程学院,河南洛阳471003)

1.引言

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。FPGA采用CMOS SRAM制造工艺,使用SRAM来存储编程数据,具有系统可编程特性。当掉电后,FPGA恢复成白片,内部逻辑关系消失,因此,FPGA能够反复使用。当需要修改FPGA功能时,只需换一片EPROM即可。这样,同一片FPGA,不同的编程数据,可以产生不同的电路功能。因此,FPGA的使用非常灵活。但使用FPGA时,每次上电之后都需要再重新下载程序,无疑是非常不方便的。因此在使用时需要对FPGA进行配置,即在每次系统上电时,必须用配置芯片对其进行配置,只有在配置正确的情况下,系统才能正常工作。配置数据可存储于片外的EPROM或其它的存储体上。本文所使用的FPGA芯片EPF10K10是Altera公司FLEX10K系列产品之一,包括可用逻辑门1万~25万,RAM 6114~4096位,512个宏单元,具有高密度、高速度的特点。配置芯片是Altera公司的可擦除芯片EPC2LC20,内部有1,695,680位。

2.配置方式

2.1 FPGA的配置方式

FPGA的配置方式有以下几种:

(1)EPC1配置该方法是使用Altera公司提供的专用EPC1 EPROM对器件进行配置,EPC1 EPROM存储配置数据,并产生同步时钟信号和控制信号,但该EPROM只能烧写一次,适用于产品定型后使用。

(2)被动串行配置方式PS(Passive Serial)

(3)被动并行同步配置PPS(Passive Parallel Synchronous)

(4)被动并行异步配置PSA

FPGA中有一些特殊管脚在配置过程中使用。

MSEL0、MSEL1为输入配置方式选择引脚,表1说明在二者选取不同值时的配置方式。

在本次设计中选择MSEL0、,MSEL1均为低电平。

nSTATUS为配置状态监测输出引脚,此信号需经1K电阻上拉。配置过程中,出现低电平表明配置过程出现错误,需重新配置。

表1 配置方案设置

nCONFIG为配置控制引脚。

DCLK为串行配置的时钟输入,用于锁存外部数据。

CONF_DONE为配置状态输入输出引脚,此信号需经1K电阻上拉。配置过程中,10K电阻将此信号拉低,成功配置完毕后,芯片释放端口,由上拉电阻将其电平抬高。

nCE为使能输入引脚。

nCEO为使能输出引脚。

2.2 EPC2存储器的配置

Altera的可重复编程逻辑器件EPC2满足了在系统编程的要求,具有Flash配置存储器,可用来配置5.0V、3.3V、2.5V器件。通过内置的IEEEStd 1149.1 JTAG接口,EPC2可以在5.0V和3.3V电压下进行在系统编程(ISP)。Altera公司的Quartus II和MAX+PLUS II软件均支持配置器件的编程,设计中软件自动为每一个配置器件产生POF文件。

(1)JTAG模式:JTAG边界扫描模式是采用JTAG接口方式对器件进行在系统编程。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。相关JTAG引脚的定义为:TCK为测试时钟输入;TDI为测试数据输入,数据通过TDI引脚输入JTAG接口;TDO为测试数据输出,数据通过TDO引脚从JTAG接口输出。

(2)EPC2引脚

EPC2的nCS和OE引脚控制DATA输出引脚的三态缓冲器、使能地址计数器和EPC2的振荡器。nCS引脚控制配置器件的输出。当OE引脚接低电平时,不论nCS为何状态,地址计数器复位,DATA引脚输出为高阻状态。当OE引脚接高电平时,如果nCS保持高电平,则计数器停止计数,DATA引脚保持高阻状态:如果nCS为低电平,则计数器和DATA引脚正常工作。EPC2中的nINIT-CONF引脚与FPGA器件的nCONFIG引脚相连;EPC2的DATA引脚与FPGA器件的DATA0引脚相连。存储在EPC2器件中的数据在其内部时钟的控制下顺序输出到DATA脚,然后在控制信号的控制下输出到FPGA器件的DATA0引脚。

EPC2与FPGA连接电路图1所示:

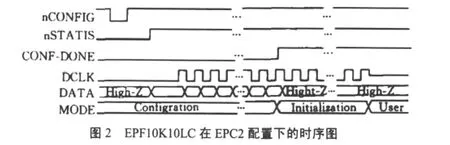

当NCONFIG产生下降沿脉冲时启动配置过程。在DCLK出现上升沿时,芯片将一位数据传入内部,直至所有数据都被移入。在配置过程中,系统需要实时监测,一旦出现错误,NSTATUS被拉低,系统必须能识别这个信号,并重新启动配置过程。配置数据全部正确地移入芯片内部后,CONF_DONE信号跳变为高,此后,DCLK必须再提供10个周期的时钟,确保芯片被正确初始化,进入用户工作模式。图2为单个EPC2器件配置EPF10K10LC的时序图。

3.下载步骤

在编译文件完成后,就需要下载文件,具体步骤如下:

(1)将要下载的文件置为顶层文件,然后点击主菜单Assigndevice…,在弹出的窗口中选择目标芯片。在Device Family中选择FLEX10K系列,在Device栏中选择EPF10K10LC84-3;然后点击Device Option。在弹出窗口中的Configuration EPROM栏中选择EPC2LC20,单击OK,回到Device画面,单击OK。

(2)执行一次“compiler”(编译)命令,产生新的*.pof文件。

(3)打开下载编译器,选择JTAG/Multi-DeviceJTAG Chain Setup。在弹出窗口中的Device Name和Programming File Name栏中分别选择器件和该器件对应的文件(1、EPF10K10对应*.sof文件,2、EPC2对应*.pof文件。注意应先输入EPC2所对应的*.pof文件,再输入EPF10K10对应*.sof文件,输入先后次序不能颠倒),选择一项后,点击“ADD”按钮(应注意不要点击“change”按钮),再选择另一项。然后单击“OK”按钮即可。

(4)选定完成后,对该项目进行编译。

(5)分别对器件进行编程,配置。

完成上述步骤后,就已将该文件配置到两个目标芯片中。当掉电后,程序会保存到EPC2器件中,上电后,EPF10K10把程序从EPC2中读入,从而实现了FPGA芯片中程序的掉电保持功能。

4.结束语

EPF10K10和专用配置芯片EPC2的电路连接较为简单,通过合理的下载配置电路能正确地将设计配置到FPGA器件中。该方法具有操作简单、系统稳定性高的特点。

[1]Alter corporation.configuring FLEX10K Device.Application Note 59,December 1995;1.

[2]张小平,赵不贿.Altera新型FPGA器件的配置方式[J].微处理机,2006,(4):93-95

[3]潘松,黄继业.EDA技术实用教程[M].北京:科学出版社,2002.

[4]王诚.Altera FPGA/CPLD设计(高级篇)[M].北京:人民邮电出版社,2005.