基于FPGA的数字IC交流参数测试系统研究

刘凤伟,詹惠琴,古 军

(电子科技大学自动化工程学院,成都 610054)

1 引言

随着电子技术的飞速发展,数字集成电路的应用日益广泛。同时数字集成电路测试工作在IC设计、验证、封装过程中占有非常重要的地位,而先进的测试流程和测试方法能有效控制产品在生产各个环节的质量和成本[1]。数字集成电路测试包括直流参数测试、交流参数测试和功能测试[2]。其中,数字集成电路交流参数是一项非常重要的指标,各个先进测试设备都有其交流参数测试的功能,如惠锐捷的V50,测试精度达到8.06ns,而泰瑞达的J750更是达到了66ps的测量精度[3]。各种高速器件的应用要求测试精度不断提高,所以开发出大范围、高精度、高效率的交流参数测试仪是一个充满机遇和挑战的课题,研究它具有非常现实的意义。

2 交流参数测试内容

在数字IC交流参数测试中,交流参数种类繁多,主要包括脉冲宽度(Tw),输入/输出脉冲上升时间(Tr),输入/输出脉冲下降时间(Tf),建立时间(Tset),保持时间(Th),最高时钟频率(fmax),输入电平到输出电平的传输延迟(Tplh、Tphl、Tpzh、Tpzl、Tphz、Tplz)等[4]。本设计的IC交流参数测量板结构如图1所示,包括可编程负载、激励信号施加单元、信号采集整形单元、时间间隔测量单元、RMS测量单元和控制核心单元。

2.1 测量 Tr、Tf、Tphl、Tplh

以测量输出延迟为例,设定比较电平Vref=50%Vpp,施加激励信号DataIn,检测DUT输出信号DataOut,通过采样整形电路把DataIn和DataOut信号采集,转换成Start和Stop脉冲,而后把Start和Stop脉冲输入给时间间隔测量单元测量,得出测量结果,显示在计算机界面上。

2.2 测量Tset、Th

针对时序器件,需要测量信号的建立时间和保持时间,此时需要功能验证测量板的密切配合,测量方法为:配置好负载电路,通过激励施加网络施加激励时钟Clk和脉冲输入信号DataIn。

测量Tset:通过延迟芯片调节DataIn提前Clk的时间,通过功能验证板的功能状态检测器,检测输出时序是否满足要求,从而测量出信号的建立时间Tset。测量Th:通过延迟芯片调节DataIn延迟Clk的时间,通过功能验证板的功能状态检测器,检测输出时序是否满足要求,从而测量出信号的建立时间Tset。

2.3 输出信号的T和F

对于输出信号为脉冲信号时需要检测输出信号的T或F,此时设计好负载电路,施加激励信号,信号整形模块采集输出脉冲,输入给时间间隔测量单元完成测量。

2.4 测量fmax

测量器件最大工作频率,通过激励施加单元施加脉冲信号,根据具体IC设置负载电路。调节脉冲的输出频率范围,通过功能验证板的功能状态检测器检测输出信号,做功能验证,看是否满足时序要求,从而测得器件的最大工作频率。

3 内插技术在交流参数测试中的运用

3.1 FPGA中内插技术的研究

时间间隔测量技术发展由来已久,有各种各样的测量方法:直接测量法、电流积分法、时间扩展法、游标卡尺法、内插技术法等。在1997年,波兰科学家Jozef Kalisz等人就开始了时间间隔测量技术在FPGA中应用的研究[5]。他们提出一种在Quick Logic公司PASIC系列FPGA上构建延迟线实现时间间隔测量的结构,精度达到了200ps[6]。该款FPGA为一次反熔丝结构。Jozef Kalisz领导的研究小组利用这一结构,构建了两条延迟线。Clk从/EN输入,Start和Stop脉冲从IN输入,设D~Q的延时t1,/EN~/ENOUT的延时t2,插值求得T1=N1(t2-t1),同理求得T2=N2(t2-t1);得时间间隔T=NT0+(N1-N2)(t2-t1),时间分辨力达到t2-t1(t2>t1)。由于FPGA独有的技术,内部逻辑门延迟t1和t2都非常小且非常稳定,致使该技术得到了很大的推广,各个研究团队分别在其他系列的FPGA上构建类似延迟线以实现精准的时间测量。近年来国内也有相关的研究,也多是基于该思想衍生出了多种构建延迟线的测量方法,更详细的介绍请参阅参考文献[7]和[8]。

3.2 FPGA内插技术在交流参数测试中的应用

本文基于Jozef Kalisz等人的基本思想,将其成功运用于Altera公司ACEX1K50系列FPGA当中。在FPGA中构建延迟线需要满足以下几个条件:首先,要求时间内插单元延迟t非常小,且随着器件工作温度的上升,延迟单元的时间稳定性要非常好,因为t直接决定了时间测量的分辨力和测量精度;其次,因为在FPGA内部需要构建精准的延迟线,这就要求FPGA内部必须有这样一种特殊结构,便于构建延迟线;最后,也应该考虑系统的开发成本和难度。

基于这几种考虑,经过查阅资料和仿真验证,最后选定ACEX1K50系列的EP1K50TC144-1这款器件。利用该款器件当中的专用时间进位链,因为该款FPGA中专用进位链延迟tcico=0.1ns,延迟链延时非常小且可以通过施加约束自动布线成级联结构,满足构建延迟线的基本要求。本设计基本延迟线的结构如图2所示,每一级延迟线为一个LE中的内部专用进位链,同时每一级锁存器与延迟线共存于一个LE当中,锁存延迟线上数据。布线时将寄存器和进位链约束于同一个LE当中,至此延迟线的数据就通过寄存器锁存到数据线上,然后再通过译码单元得出延迟线的数据。

本设计采用延迟线插值法,外部FPGA工作主时钟Clk为150MHz,在FPGA内部构建一个32位串行计数器,工作速度为150MHz,最小分辨力6.6ns,则最大计数值为6.67×232=28.6ns,计数范围为7ns~28s。为了获得更高分辨力,采用延迟线插值法,在FPGA内部利用专用时间进位链搭建延迟线,利用64个一位全加器级联构成。电路综合后,查看时序收敛延迟线电路如图3所示。

Start和Stop信号各搭建一条64级的延迟线。查器件手册得知EP1K50TC144-1中每个LAB中有8个LE,每个LE中的时间进位链延迟tcico为0.1ns,LE之间的延时为0,每两个LAB之间的延迟为0.1ns,且只有奇数列和奇数列搭建,偶数列和偶数列搭建,不能跨过中间的EAB,则可知最大可以搭建的延迟线长度为72(8×9=72)个延迟单元,最大延迟时间为0.1(71+8)=7.9ns,设计主时钟采用150MHz,插值单元大小为一个周期6.67ns,故为了方便,搭建了64级延迟线,插补范围为0.1(64+8)=7.2ns,7.2ns>6.67ns满足设计要求,同时设计了译码电路负责把延迟线电路输出Q1~Q64译码成十进制数据。最后的测量结果为T=NT0+0.1(N1-N2),同时从延迟线的结构可以看出:每一级延时下到下级延迟线的传输延迟在LAB内部为0,在LAB之间为0.1ns,而每一个延时链内部,延时模块到寄存器的输入端的延迟tpacked=0.2ns,测量分辨力大约为0.1+0.2=0.3ns。

4 仿真验证与结果分析

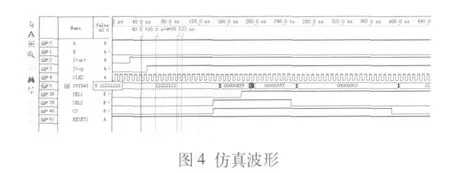

在FPGA综合设计仿真中,采用了Altera新一代综合仿真工具QuartusⅡ9.0,它是集设计、综合、布线、仿真于一体,功能强大、操作简单的FPGA专用设计软件。当然Altera也支持其他综合仿真设计工具,如Synplify、modelsim等。在QuartusⅡ9.0中建立工程,编辑设计文件,添加好管脚和特殊门电路约束,然后全编译。在仿真波形当中编辑输入波形文件,然后进行时序仿真,仿真波形如图4所示,改变输入波形文件得到各种测试数据,在此列出了10次测量的数据,如表1所示。从表1中可以看出插补单元的分辨力大约在250ps左右,基本符合前面的分析。

5 结束语

以上介绍了数字IC交流参数测试的基本内容,研究了FPGA的时间内插方法,并将其运用于数字集成电路交流参数测试工作中,最后通过仿真验证了这种方法的测试精度。结果表明利用最新的FPGA技术大大提高了集成电路交流参数测试精度,使测量方法更加先进有效,同时在降低了测试成本的基础上实现了测量精度高、动态范围广、测试方法方便有效和稳定可靠。

[1]谭伟.数字集成电路测试技术应用[J].微处理机,2008.8(4):1-2.

[2]潘曙娟,钟杰.基于ATE的IC测试原理、方法及故障分析[J].半导体学报,2006,12(27):1-2.

[3]李桂华,徐英伟,钟娜,等.集成电路交流参数测试方法研究[J].微处理机. 2000,8(3):1-2.

[4]张静,于祥苓,李海泉.浅谈集成电路交流参数的测试[J].微处理机,2008,6(3):1-2.

[5]J Kalisz, R Szplet, R Pelka,et al. Single-Chip Interpolating Time Counter with 200-ps Resolution and 43-s Range[J].IEEE TRANSACTIONS ON INSTRUMENTATION AND MEASUREMENT, 1997,46(4).

[6]J. Kalisz, R. Szplet, J. Pasierbinski,et al. Field programmable-gate-array-based time-to-digital converter with 200-ps resolution[J]. IEEE TRANSACTIONS ON INSTRUMENTATION AND MEASUREMENT, 1997,46.

[7]宋健.基于FPGA的精密时间-数字转换电路研究[D].合肥:中国科学技术大学. 2006.

[8]陈炳权.基于FPGA中专用进位连线的精密TDC设计[J].湘潭大学自然科学学报, 2008,3(1):2-3.