基于确定模式的伪单跳变测试矢量生成技术

刘建军,李铁军,邹立明

(1.集美大学 信息工程学院,福建 厦门 361021;2.上海普阅信息科技有限公司,上海 201203)

在现代电路测试方法中,内建自测试(BIST)由于具有许多优点已经成为超大规模集成电路测试中的一个最具前景的解决方法。伪随机模式测试是当前BIST中最受欢迎的测试方法,因为它不需要占用很大的存储面积开销,只需要有限个数的输入向量便可达到很高的故障覆盖率[1]。但是对于电路中剩余的难测故障所需要的测试模式的数量可能会很巨大,以致于不能实用,采用确定模式测试集来覆盖被测电路中剩余的难测故障就成为被关注的研究方向。折叠集合就是一种简单有效的确定模式测试集,基于折叠集的确定模式GIST提供了一种非常实用的BIST解决办法。

1 约翰逊折叠计数器的工作原理

约翰逊折叠计数器又称为可编程的约翰逊折叠计数器(简称折叠计数器)[2,3],它带有动态改变的状态转移函数,取决于计数器的状态和转移距离。一个初始状态s∈{0,1}n开始,产生一个 n+1状态序列 F(0,s),F(1,s),…,F(n,s),其中状态从 F(i,s)转移到 F(i+1,s)保持前 i位不变,翻转所有余下位。翻转仅仅由位置i和转移距离j决定。状态转移函数如下[4,5]:

表1 计数生成原始序列和改变顺序的序列的比较

2 伪单跳变测试矢量生成技术

LFSR编码最突出的特点是仅与测试矢量中确定位数有关[6],而与测试矢量中无关位无关。从而,如果测试矢量中包含大量无关位,则利用LFSR编码和约翰逊折叠计数器的特点就能对测试矢量进行优化,文中利用LFSR编码产生约翰逊折叠种子,再由编码的约翰逊折叠种子展开成约翰逊折叠序列,然后对其约翰逊折叠序列进行重排,使相邻间测试矢量跳变个数达到最少,而达到功耗减少的目的。整个编码流程图如图1所示。

图1 确定模式下的编码流程

为了便于理解,这里先利用实例来说明LFSR对约翰逊折叠种子的编码过程,如图2所示。

约翰逊折叠计数器状态矢量生成的计算公式在前面已经介绍。图2 LFSR对折叠种子编码进行压缩的实例,左边为给定的确定测试立方体,其中测试立方体中“X”表示无关位。中间为度数2的LFSR,编码测试立方所需的初始种子是“11”,生成的矢量为“s=110110”,将此矢量作为约翰逊折叠计数器的初始种子,按照前面给出的公式计算,得到图2右边的表格,从这个表格中可以看出给定的确定测试立方体,分别包含在折叠状态生成序列 F(0,s),F(3,s)和 F(5,s)中,因此,只要保存 LFSR的种子“11”,就可以生成完全覆盖确定测试集的矢量序列。具体编码LFSR种子和编码测试立方体作为折叠种子策略参见文献[7]。

图2 确定矢量编码过程

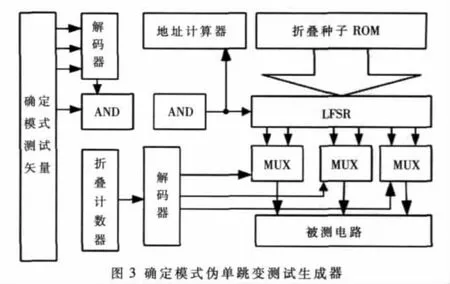

本文方案实质是一种将FAULTSIM产生的确定测试矢量与约翰逊折叠序列的特点相结合的测试方案,因此整个自测试方案的低功耗设计就是通过折叠控制器来进行测试矢量优化设计。本文给出的低功耗测试产生器方案也是以LFSR为基础的,其结构如图3所示。LFSR的级数为n,计数器为n+1进制累加计数器,其长度为[log2(n+1)],解码器对计数器的输出进行解码,输出的控制信号Y分别去控制相应的多路选择器MUX,从而选择LFSR内部的某一触发器的状态输出端Qi(Yi为1时)或其反相输出端Qi(Yi为0时)做为测试输入信号。只要合理地设计解码器就可以产生n个单输入跳变的测试向量。当计数器为 0时,Y0为 1,其余 Yi为 1,此时与门开放,LFSR的CLK输入有效,LFSR将产生一个伪随机测试向量,计数器从 1加到 n时,Y0为 0,与门关闭,LFSR的CLK输入无效,由解码器的输出Yi(i=1,2,…n)来控制MUX产生n个单输入跳变的测试序列。表1列出了当LFSR初始值为10111时产生的6个测试向量,在此期间,LFSR的值保持不变,直到计数器回0时,LFSR将产生一个伪随机测试向量。这个测试生成器是针对每周期测试的GIST设计的,产生的向量直接送往待测电路的输入端。经改造后LFSR和待测电路的活动性都大大降低,从而使得功耗进一步降低。

表2列出了当LFSR装入一个折叠种子值为10111时产生的折叠测试序列编码前后测试矢量的比较。

表2 编码前后测试的比较

为了降低功耗,可以对由折叠种子产生的折叠序列进行重新排序,使得相邻的折叠向量之间只有一位不同,从而产生单输入跳变的测试序列,这样可以使得被测电路 (CUT)输入端的相邻测试向量之间的相关性增强。例如折叠种子值为10111,产生的未排序的折叠序列为:10111→01000→00111→00000→00011→00010,经过排序后的单输入跳变序列应为:10111→00111→00011→00010→00000→01000,通过表2右半部分可以看出,只需要对解码器进行重新设计就可以实现这个排序功能,从而不需要对原电路进行大规模的设计修改。而且从表2可以看出解码器的输出Y0和Yi的数值是一样的,因此可以合并为一个输出,从而使得解码器进一步简化。其中折叠计数器与解码器在一起构成了折叠控制器。由不同的折叠种子产生的测试序列都是单输入跳变测试序列,只有在重新给LFSR置入种子时不是单输入跳变序列,这样整个的折叠测试序列就是伪单输入跳变测试序列。

在确定模式BIST的设计中折叠控制器起到了关键作用,开始阶段折叠控制器在LFSR生成的每两个相邻的伪随机向量之间插入一个向量 (为LFSR的位数),使插入的每一个向量与其前驱向量只有1位不同,这样就可以获得伪单输入跳变测试序列 (仅在LFSR产生下一个伪随机向量时不是单跳变)。在一定长度的伪单输入跳变测试序列生成后,开始由折叠控制器控制从ROM中取折叠种子装入LFSR,此时的LFSR只相当于一个寄存器,折叠控制器中的解码器完成对由一个折叠种子产生的原始折叠集的排序产生单输入跳变测试序列,然后再装入下一个折叠种子,折叠控制器接着产生下一个单输入跳变测试序列,这样直到所有的折叠种子都被装入为止,整个的由不同的折叠种子产生的折叠测试序列就是伪单输入跳变测试序列。最终可以发现两部分测试向量序列组成的完整的测试序列也是伪单输入跳变测试序列。

3 实验数据结果分析

将这种新的低功耗测试生成器在ISCAS85/89部分实验电路上进行了实验。实验前用C++编程模拟上述测试生成过程,再将得到的测试向量集施加给待测电路,再进行WSA和故障覆盖。这种方案是从降低CUT输入端的跳变密度着手进行设计的,在这种设计中,折叠控制器在完整的伪单输入跳变测试序列中发挥了关键作用。表3是以ISCA85标准电路编码前后WSA比较。

表3中第一列表示标准电路名称,第二列表示该电路的输入端口数,第三列表示本方案编码后需要存储的折叠种子个数,第四列表示本方案的故障覆盖率,第五列表示压缩后但没有经过约翰逊折叠计数器编码的各电路WSA统计值,第六列表示本方案的各电路WSA统计值,而第七列是参考文献[7]中的实验结果。通过结果的比较可以发现本方案的优越性。观察表3可发现本方案电路中产生的测试功耗大大低于参考文献[7]中的功耗值。由于本方案采用的是完全确定性测试,因此电路中的故障(除不可测故障外)均可测出,而参考文献[7]中由于采用的是伪随机测试,因此不能保证每个电路的高故障覆盖率。

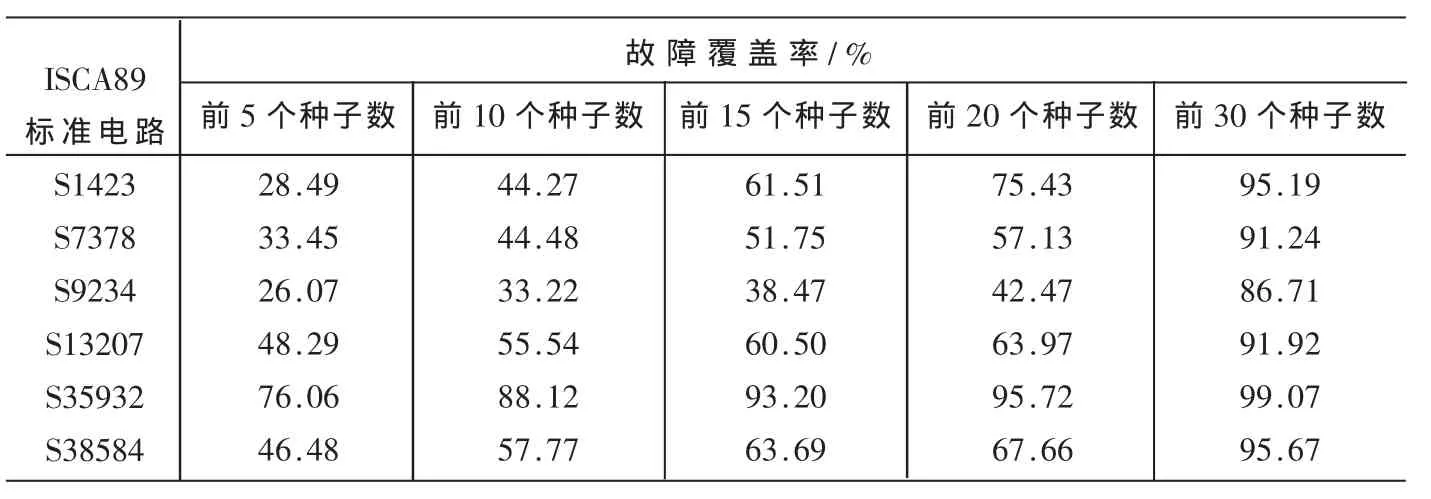

表4给出了种子数对故障覆盖率的影响,利用FAULTSIM对ISCA89电路进行了分析,结果表明,当测试矢量种子数达到30时,故障覆盖率很高,基本上可以代替其他的所有测试矢量。这样就极大地减少了测试矢量数,而达到低功耗的目的。

图4是以C432电路为例的仿真结果。

对比于文献[7]提出的测试方案,本文提出的方案存在突出的优点:(1)被测电路产生的测试功耗比文献[7]的测试功耗要小得多;(2)本方案的目标结构比混合低功耗GIST方案简单,而且开销比较小;(3)由于所有的故障都采用折叠序列测试,因此保证了峰值功耗比混合模式BIST低功耗小,而且更加有效地保护了被测电路。

本文利用参考文献[2]中的编码方案,结合折叠序列的特点,设计出完全确定性低功耗测试方案。不但保证了高故障覆盖率,而且在编码效率和解码结构上比常用的FDR编码优越。在功耗方面,不但可以降低平均功耗,而且可以降低测试中的峰值功耗。本文又利用控制电路来选择MUX的输入,实现了测试集的单输入跳变。该设计方案具有比类似LPTPG方案故障覆盖率高,面积开销小的特点,因而具有一定的使用价值及参考意义。

表3 ISCA85标准电路编码后WSA比较

表4 种子数对故障覆盖率的影响

[1]梁华国,聚贝勒.海伦布昂特,汉斯一邓西姆.冯特利希等.一种基于折叠计数器重新播种的确定自测试方案[J].计算机研究与发展,2001,38(8):931-938.

[2]ZORIAN Y.A distributed BIST control scheme for complex VLSI devices[A].In:1993 VLSI Test Symposium Digest Of Papers Eleventh Annual 1993 IEEE[C].Atlantic Cit,NJ,1993:4-9.

[3]GIRARD P,GUILLER L,LANDRAULT C.et al.A test vector ordering technigue for switching activity reducion during test operation[C].In:IEEE Great Lakes Sympon VISI,March 1999:24-27.

[4]HELLEBRAND S, RAJSKI J, TARNICK S,et al.Builtin test for circuits with scan based on reseeding of multiple polynormial linear feedback shift registers[J].IEEE Trans.On Computers,1995,44(2):223-233.

[5]KOENEMANN B.LFSR-ceded test patterns for scan designs.Eur Test Conf.1991:237-242.

[6]AHMED N,TEHRANIPOUR M H,NOURANI M.Low powerpattern generation for BIST Architecture[C].Proc.ofIEEE VISI Test Symposium,2001:329-334.

[7]GERSTENDORFER S,WUNDERLICH H J.Minimized power consumption for scan-based BIST.Test Conference,1999.Proceedings.International,1999:77-84.