基于Actel FPGA的UART应用

UART(UniversalAsynchronous Receiver/Transmitter)即通用异步收发传送器,工作于数据链路层,包含了RS-232、RS-422、RS-485串口通信。它具有传输线少、成本低和可靠性高等优点,广泛应用于通信、医疗及消费电子、汽车电子和工业及数据处理等领域。

Actel公司免费提供两种形式的UART IP核:CoreUART和CoreUARTapb。CoreUART使用普通的总线形式,用户可以很方便地将它和其他模块进行连接;CoreUARTapb基于APB总线形式,它的好处是可以连接到Core8051或者是CortexMl处理器上,方便用户进行soc设计,本文将主要介绍基于Actel FPGA的IP-CoreUARTapb,其内部的设计原理与CoreUAKT是一样的,区别仅在于接口部分。

1CoreUARTapb介绍

(1)UART协议简介

UAKT协议的工作原理是将传输数据的每个字符按比特位进行传输,之所以称它为异步的,是因为在传输数据时,不需要同时传送时钟。图1给出了它的工作模式。

其中各位的意义如下。

·起始位:发出低电平“0”的信号,表示传输字符的开始。

·数据位:紧接着起始位之后是数据位,数据的个数可以是5、6、7、8等,构成一个字符,通常采用ASCII码,从最低位开始传送。

·奇偶校验位:根据数据位“1”的个数确定为偶数(偶校验)或奇数(奇校验),以此位来校验数据的正确性。

·停止位:它是1位的字符数据结束标志。可以是1位、1.5位、2位的高电平。

·空闲位:处于逻辑“1”状态,表示当前线路上没有数据传输。

·波特率:衡量数据传送的速率,表示每秒钟传送二进制的位数。

(2)内部结构框图

如图2所示,CoreUARTapb的结构框图可以分为APB总线接口、波特率发生器、发送缓冲器、发送状态机、接收状态机和接收缓冲区模块。APB总线接口模块提供了UART和APB总线进行通信的接口;波特率发生器主要为发送和接收状态机提供时钟;发送和接收状态机模块主要完成数据的发送和接收的功能;发送和接收缓冲区提供了一个字节的发送和接收缓冲区。

CoreUARTapb分为两种模式:FIFO模式和正常模式。FIFO模式的结构框图如图3所示,FIFO模式和正常模式的区别是使用发送FIFO和接收FIFO代替了正常模式下的发送和接收缓冲区,保证了接收和发送数据的正确性。其发送FIFO和接收FIFO各为256字节。

(3)内部寄存器

CoreUARTapb的寄存器的地址映射如表l所示。

·发送数据寄存器(只写)

保存了要发送的七位或八位数据。

·接收数据寄存器(只读)

存放着接收的七位或八位数据。

·控制寄存器#1(读写)

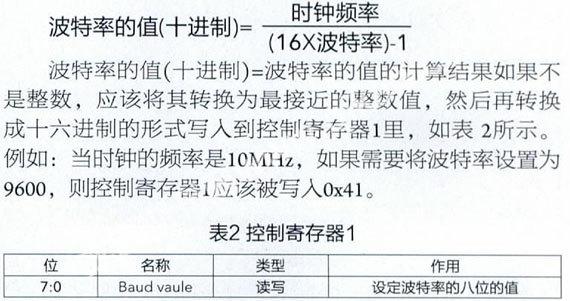

控制寄存器1包含了波特率的值,它是用来设置CoreUARTapb的波特率的值。波特率值的计算公式为:

·控制寄存器#2(读写)

它是用来控制CoreUARTapb的一些配置参数,如表3所示。

(4)时序图

·CoreUARTapb发送数据时序

CoreUARTapb发送数据是在PWRITE信号,PSEL信号和PENABLE信号为高,并且地址线上的地址有效时,将要发送的数据被锁存到发送缓冲区中,当TXRDY为低时。表明发送缓冲区已满,下一个时钟周期就可以开始发送数据,如图4所示。

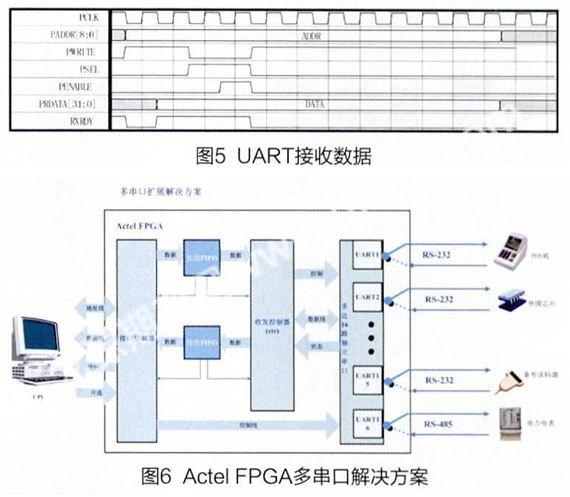

·CoreUARTapb接收数据时序

CoreUARTapb接收数据是在RX线上检测到一个开始位信号,数据被存入到接收缓冲区中。当RXRDY信号为高时,表明接收缓冲区已满;当PWRITE信号为低、PSEL信号和PENABLE信号为高,并且地址线上地址有效时,接收缓冲区中的数据才被总线取走,RxRDY信号同时也被拉低。如图s所示。

(5)应用场合

UART的通信被应用于多种场合,多串口的扩展便是其典型的应用之一。多串口扩展的普遍应用于电力集中抄表、便携式设备、自动化和制造进程控制以及智能家居行业等场合。采用Actel FPGA来实现的多串口扩展模块具有单芯片、小封装、扩展通道多、灵活性好、可裁减或添加用户自定义功能等优势,如图6所示。

2小结

本文主要介绍了基于Actel PPGA的UART Ip设计与应用,除了UART IP以外,Actel公司还提供了SPI、I2C、PWM、Timer等IP核,请关注周立功公司的网站获得更多的信息。我们有着一个强大的FPGA团队提供强有力的售后服务,解决用户在产品使用和研发过程中遇到的困难。若有更多的需求可以与我们联系。我们将会竭诚为您服务,并能关注下期的FPGA专题技术讲座。