基于嵌入式系统的数字扩频收发信机设计

摘 要:将扩频技术和嵌入式技术结合起来,设计了一种数字扩频收发信机,它是双通道的,每一个通道都包括硬件和软件两部分。硬件部分由语音编解码电路、嵌入式微处理器、电平转换电路、语音数据扩频解扩调制解调电路、锁存及控制信号产生电路、外部存储器和射频单元电路组成;软件部分由系统启动加载程序和收发机系统的主程序两部分组成。通过软件编程、调试、下载,硬件焊接连线,通电调试,发送通道实现了话音录入、扩频和BPSK调制、无线发送;接收通道实现了无线接收,BPSK解调、解扩和播放;两通道可同时进行;在无线传输时,最远传输距离可达1 km左右,表明达到了设计要求。

关键词:嵌入式系统;扩频;发射;接收

中图分类号:TN702文献标识码:B

文章编号:1004-373X(2009)05-093-03

Design of Digital Spread-spectrum Transceiver Based on Embedded System

LONG Guangli

(Shaanxi University of Tecnology,Hanzhong,723003,China)

Abstract:A sort of ditigal spread-spectrum transceiver is designed,which is hand in hand between the spread-spectrum technique and embedded technique.It is two-channels,each channel includs two parts:hardware and software.Hardware circuit includs voice codec circuit,embedded microprocessor,voltage switching circuit,voice data spread-despread spectrum and modulation-demodulation circuit,lock packing and signal controled circuit,external storage and radio frequency unit.Software includs two program: starting-loadding system program and master program of transceiver.Behind programming software,debugging program,downloadding software,weldding and linking Hardware circuit,switching on electrify and debugging circuit,the transmitting channel may realize voice-loginning,speading-spectrum,BPSK modulation and wireless transmitting;the receiviing channel may realize wireless receiviing,BPSK demodulation,despeading-spectrum and voice-playing.The two channel may run at one time and the farthest transmission range may approve 1 km.The result shows that it achieves the expected criteria of design.

Keywords:embedded system;spread-spectrum;transmit;receive

0 引 言

嵌入式系统就是一个具有特定功能或用途的计算机软硬件结合体,或指装入另一个设备并且控制该设备的专用计算机系统。嵌入式系统的最大特点是其具有目的性和针对性,即每一套嵌入式系统的开发都有其特殊的应用场合与特定功能。嵌入式系统包含硬件和软件两部分。硬件架构以嵌入式处理器为中心,配置存储器、I/O设备、通信模块等;软件部分以软件开发平台为核心,向上提供应用编程接口API,向下屏蔽具体硬件特性的板级支持包BSP。嵌入式系统中,软件和硬件紧密配合,协调工作,共同完成系统预定的功能[1]。

扩频通信是当今国际上高新技术热点之一 ,其理论基础是香农(C.E.Shannon)的信道容量公式[2]。该公式表明,在高斯信道中,当传输系统的信号噪声功率比SNR下降时,可用增加系统传输带宽W的办法来保持信道容量C不变;对于任意给定的信号噪声功率比,可以用增大传输带宽来获得较低的信息差错率。扩频技术正是利用这一原理,用高速率扩频码来达到扩展待传输数字信息带宽的目的。扩频通信系统的带宽比常规通信体制大几百倍至几千倍,故在相同信噪比的条件下,具有较强的抗噪声干扰能力。

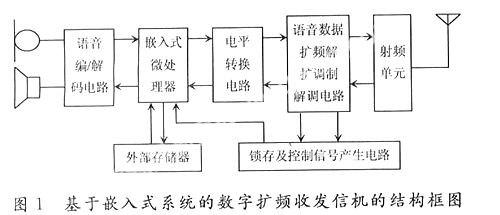

1 基于嵌入式系统的数字扩频收发信机的硬件设计

设计的基于嵌入式系统的数字扩频收发信机结构框图如图1所示。

该数字扩频收发信机是双通道的(图中只画出单一通道)。通道由语音编解码电路、嵌入式微处理器、电平转换电路、语音数据扩频解扩调制解调电路、锁存及控制信号产生电路、外部存储器和射频单元电路组成。

语音编解码电路采用PHLIPS半导体公司生产的低功耗立体声音频编解码芯片UDA1344TS。该芯片3.0 V电源供电,可工作在L3微控制器模式,也可工作在静态引脚工作模式,通过模式控制引脚MC1(8脚)、MC2(21脚)设置为静态引脚工作模式(均为高电平),在该模式下,可控制的特征有系统时钟选择、数据输入/输出格式设置、重低音和静音控制以及ADC控制,这些特征是由引脚MP1(9引脚)、MP2(13引脚)、MP3(14引脚)、MP4(15引脚)、MP5(20引脚)控制的。

嵌入式微处理器选用SAMSUNG公司为手持设备设计的低功耗、高集成度基于ARM920T核的微处理器S3C2410X。该处理器集成了16 KB指令和16 KB数据缓存、MMU、外部存储器控制器、LCD控制器、NAND FLASH控制器、4个DMA通道、3个UART通道、1个I2C总线控制器、1个I2S总线控制器、4个PWM定时器和一个内部定时器、通用I/O口、实时时钟、8通道10位ADC和触摸屏接口、USB主/从接口、SD/MMC卡接口等[3]。

语音数据扩频解扩调制解调电路选用Zilog公司研制的可编程单片直接序列扩频收发芯片Z87200。该芯片包括发送部分、接收部分和控制部分,它将扩频通信收发主要电路的各个部分都集成于一块100个管脚的芯片中。发送部分包括了发送数据的白化处理、串并变换、差分编码、PN码产生、扩频、QPSK/BPSK调制及发定时控制,完成由数据输入到已调中频信号输出的扩频、调制处理。接收部分包括中频到基带的数字下变换、PN码产生、数字匹配滤波、解扩、相关峰检测、差分解调、并串转换、去白化处理、数控振荡器及位定时处理等,完成由数字中频信号输入到数据输出的全过程解调解扩处理。此外,Z87200还设置了86 B的片内寄存器,用于对芯片功能的编程设置,使得对扩频系统的设置具有灵活性,芯片具有通用性,可与计算机或单片微处理器连接,完成对内部寄存器的编程控制[4]。

电平转换电路采用MAXIM公司的双向8通道电平转换芯片MAX3001E。由于嵌入式微处理器S3C2410X工作电压通常是3.3 V,而直序扩频收发器Z87200工作电压通常是5 V,所以可采用多个MAX3001E来连接这两个芯片,以实现它们之间的逻辑电平转换。

锁存及控制信号产生电路采用74LV373锁存器和复杂可编程逻辑器件EPM7128SLC84-15。在通过接口控制单元向直序扩频收发器Z87200读写数据时,为了确保数据的稳定,采用74LV373锁存器对要读写的数据先进行锁存,然后才完成数据的读写。EPM7128SLC84-15是ALTERA公司生产的一款MAX7000S系列的CPLD器件,用VHDL编程设计一个8位同步移位寄存器和一个9位同步计数器,在Max+PlusⅡ开发平台上进行编译仿真后下载在CPLD器件EPM7128SLC84-15上[5]。由于直序扩频收发器Z87200被设置为突发工作模式,为方便数据处理,可设置突发块的长度为8符号/帧,配合使用9位计数器和8位移位寄存器,每移位9次可得到真正需要的8位语音数据。

射频单元采用北京迅通科技公司的PTR8000(以nRF905作为数据无线传输芯片)高性能嵌入式无线模块,它专为点对多点无线通信设计,内置数据协议和CRC检错,可工作在430/868/915 MHz,工作电压在1.9~3.6 V之间,最大发射功率+10 dBM,高抗干扰GFSK调制,可跳频,数据速率50 Kb/s,独特的载波监测输出,地址匹配输出,地址就绪输出。由于与RF协议相关的高速信号处理部分已经嵌入在模块内部,PTR8000可与各种单片机配合使用,也可以与DSP等高速处理器配合使用;PTR8000提供一个SPI接口,速率由微控制器自己设定的接口速度决定,在RX(接收)模式中,地址匹配(AM)和数据准备就绪(DR)信号通知MCU一个有效的地址和数据包已经各自完成,微控制器即可通过SPI读取接收的数据。在TX(发送)模式中,PTR8000自动产生前导码和CRC校验码,数据准备就绪(DR)信号通知MCU数据传输完成。

外部存储器由一块8 MB的SDRAM(采用HY57V641620)和一块2 MB的FLASH(采用HY29LV160)构成,主要用于存放程序和数据。

2 软件设计

嵌入式系统的软件开发采用武汉创维特信息技术有限公司的ADT IDE集成开发环境,它提供高效、清晰、可视化的嵌入式软件开发平台,包括一整套完备的面向嵌入式系统的开发和调试工具:编辑器、编译器、链接器、工程管理器以及调试器等,它运行于Windows NT/95/98/2000/XP,采用类似Visual Studio界面风格,支持中、英文版本[6]。

在用户的应用程序之前,需要由专门的一段代码完成对系统的初始化,即系统启动加载程序。当ARM微处理器上电或者复位之后,处理器从0x0取值,在这个地址处安排的程序就是系统启动加载程序。由于这类代码直接面对处理器内核和硬件控制器进行编程,故采用汇编语言,其任务包括建立异常向量表、重构异常向量表、初始化存储器系统、初始化堆栈、初始化应用程序执行环境、屏蔽所有中断和呼叫主应用程序。

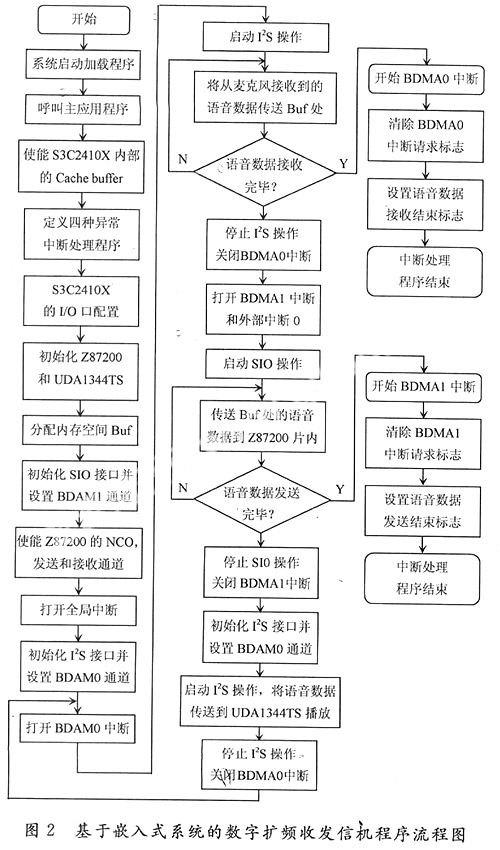

收发机系统的主程序主要完成芯片的初始化、接口的配置、语音数据流控制和中断处理等工作,使得收发机系统在嵌入式微处理器的控制下能有效地完成语音的录入、发送、接收和播放全过程,基于嵌入式系统的数字扩频收发信机程序流程图如图2所示。

3 实验结果

用汇编语言编写系统启动加载程序,用C语言编写嵌入式微处理器的数字扩频收发信机程序,在ADT IDE集成开发环境下添加源代码,保存后加入到工程中进行设置和编译,通过后经过JTAG简易调试器,将应用程序烧录到FLASH中,下载到SDRAM中。将语音编解码电路、嵌入式微处理器S3C2410X、电平转换电路、语音数据扩频解扩调制解调电路、锁存及控制信号产生电路、外部存储器和射频单元电路正确焊接在PCB板上,上电,运行程序。

在发送端,话音通过麦克风送入语音编解码芯片UDA1344TS,经过语音编码处理后,产生I2-bus格式的串行语音数据通过标准I2S语音接口传送到嵌入式微处理器S3C2410X。S3C2410X将得到的8位语音数据存储到预先分配好的数据区,接着将该数据通过同步串行接口SIO一位一位地发送到语音数据扩频解扩调制解调芯片Z87200片内进行扩频、BPSK调制等一系列处理后,得到8位数字中频语音信号;最后,通过射频单元PTR8000 无线发送出去。

在接收端,通过射频单元PTR8000无线接收到8位数字中频语音信号,送入Z87200片内进行解扩、解调等一系列处理,得到串行语音数据信号;该信号被送入CPLD器件EPM7128SLC84-15的8位同步移位寄存器;CPLD每得到一个8位语音数据就将该数据锁存并产生一个外部中断,通知嵌入式微处理器S3C2410X将这8位语音数据读走;最后在S3C2410X的控制下将语音数据通过I2S接口传送给语音编解码芯片UDA1344TS,解码处理后通过扬声器播放出来。

发送通道实现了话音录入、扩频和BPSK调制、无线发送;接收通道实现了无线接收、BPSK解调、解扩和播放。两通道可同时进行;在无线传输时,采用PTR8000高性能嵌入式无线模块,最大传输速率可达20 Kb/s,最远传输距离可达1 km左右。

4 结 语

阐述了嵌入式系统和扩频通信的含义,以嵌入式微处理器S3C2410X为核心,利用Z87200,UDA1344TS,PTR8000等模块设计出了数字扩频收发信机。该文创新点是将嵌入式技术和扩频技术融合在一起,同时采用ADT IDE集成开发环境调试嵌入式系统软件,用嵌入式微处理器对系统其他芯片进行编程控制,因而具有很好的灵活性和通用性;根据所提出的设计思路,可方便地设计其他无线通信系统,有广阔的应用前景和很好的经济效益。

参考文献

[1]曹非一,桑楠,熊光泽.嵌入式系统引导技术研究 [J].电子技术应用,2005,31(2):10-13.

[2]曾兴雯,刘乃安,孙献璞.扩展频谱通信及其多址技术[M].西安:西安电子科技大学出版社,2005.

[3]黎小玉,卢博友,杨亮,等.基于S3C2410和CF卡的FAT32开发[J].微计算机信息,2008,24(14):135-136.

[4]龙光利.直序扩频芯片的原理与应用[J].现代电子技术,2005,28(15):28-30.

[5]潘松,黄继业.EDA技术实用教程[M].2版.北京:科学出版社,2005.

[6]陈赜,秦贵和,徐华中,等.ARM9嵌入式技术及Linux高级实践教程[M].北京:北京航空航天大学出版社,2005.

作者简介 龙光利 男,1968年出生,陕西南郑县人,陕西理工学院副教授。主要研究方向为数字通信和电子技术应用。