利用现场可编程门阵列技术设计自动铃声系统

[摘要]随着数字电子技术和集成电子电路技术的飞速发展,掌握EDA技术、学会用VHDL语言设计设计电子电路是每个硬件设计工程师必须掌握的一项基本技能。用VHDL语言、MAX+plusII开发平台设计一个自动铃声系统,底层采用VHDL语言、顶层采用原理图输入的方法,在开发平台上进行编译、功能仿真、时序仿真,最后下载到FPGA开发板上进行实际调试。

[关键词]EDA VHDL FPGA 铃声系统

中图分类号:TP2文献标识码:A 文章编号:1671-7597(2009)0110036-02

一、引言

随着大规模集成电路技术和计算机技术的不断发展,在涉及通信、国防、航天、医学、工业自动化、计算机应用、仪器仪表等领域的电子系统设计工作中,EDA(Electronic Design Automation,电子设计自动化)技术的含量正以惊人的速度上升,电子类高新技术项目的开发也更加依赖于EDA技术的应用。因此,本文使用VHDL(Very high speed integrated circuit Hardware Description Language,甚高速集成电路硬件描述语言)进行程序编制,设计实现自动铃声系统,采用EDA设计软件MAX+plus II进行编译、仿真、综合,然后下载到FPGA上进行实际验证。

二、功能分析

系统应该具有基本计时、能设置当前时间、能调整起床铃时间、熄灯铃时间、能调整打铃时间长短和间歇时间长短等五项基本功能。为了能够同时查看当前年月日星期以及能够采用24小时制,在设计中加入年、月日的调整及与时间同步走时、切换12/24时制等三个功能。星期是与某一年月日相对应的固定参数,在年月日调整时设为不可见。于是八个功能组成八种状态,那么采用状态机进行各个状态的切换是最方便的。

本系统具有八个状态共八个参数,需要根据各个状态出现的顺序和打铃信号灯的亮、灭情况进行相应显示,那么可以设计“显示控制及打铃控制模块”来统一进行操作。

另外如果实验室开发板上没有按键消抖电路,那么有必要再加上软件消抖程序。于是本系统的原理框图如图1所示。

三、硬件设计

本设计采用的开发板是SpartanII开发系统。其原理图比较简单,如图2所示。

(一)状态机的设计原理

状态机的具体实现如前所述,8个功能模式对应8种状态,因此设定的状态如表1所示。

那么这8种状态的转移图容易得到如图3所示。图中默认处于正常计时状态timing,当按键changemode有效按一下就从timing开始转到箭头所指的状态adj_year。以此类推。状态机通过读入按键值进行状态切换并执行某些特定操作,所以这里应用Mealy型状态机。在这里将使用三个按键来执行相关切换。

(二)主要模块设计

1.计数器的设计

这里涉及3个参量即年、月日、时间的变化,因此可设置3个调整使能信号en1(调“年”使能)、en2(调“月日”使能)和en3(调“时间”使能),分别对应状态机的输出信号mode的mode[0]、mode[2]和mode[4]。

2.响铃时间设定

利用接口电路实现时间设定并进行仿真。

3.显示控制及打铃控制模块

该模块集中了前面几个模块的输出信号根据状态机所给出的状态分别进行显示。

4.按键消抖及同步化辅助模块

键盘的按键闭合与释放瞬间,输入端信号会有毛刺。如果不进行消抖处理,系统会将这些毛刺误以为是用户的另一次输入,导致系统的误操作。因为人按键的时间大约为10ms,不可能有更快的按键动作发生。这里将10ms作为分界,把小于10ms的按键动作视为抖动,而时间长达10ms及以上的视为有效按键。

四、结论

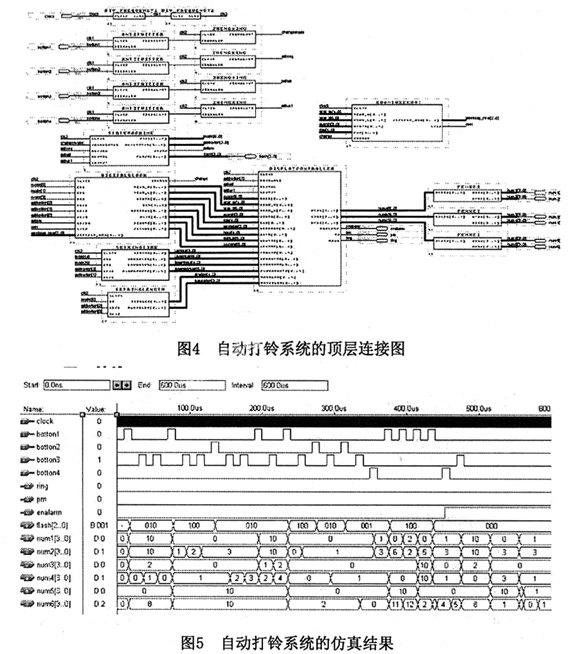

综上所述,最终的电路连接图如图4所示,根据对它进行的仿真,如图5所示,说明该系统能够正确实现其功能。本文增加了“年月日星期”的切换显示,并且其值可调,使得自动打铃系统已经不是单纯的计时器,而是一本“日历”,这样在功能扩展时可以做到:如果周末休息不需要上下课打铃,只需在“显示控制及打铃控制模块”里加上当星期weekday<=5时才执行下面的打铃功能。如果有条件可以考虑使用液晶显示屏进行多个参数“同时”显示,而铃声可使用专用芯片的真人发声或音乐提示,提高系统的人性化特征。同时要考虑其成本也会相应增加,这是在进行产业化设计中必须考虑的问题。

参考文献:

[1]侯伯亨、顾新,VHDL硬件描述语言与数字逻辑电路设计(修订版),西安电子科技大学出版社,2004.

[2]张展、王亚洲,基于EDA技术的自动打铃器设计,电子世界,2003,(04).

作者简介:

罗华阳,男,湖南邵东人,湖南铁路科技职业技术学院,讲师,研究方向:自动控制与通信技术。