基于EDA技术的数控分频器设计

韩丽英

[摘 要]数控分频器广泛应用在家庭数字音响、通信设备时序电路、数字频率计中。另外,近

年来已成为电子竞赛设计中常用的单元模块。本文论述了数控分频器的基本原理、设计思路

及小数分频器的原理及设计,并给出了一个2.5 分频器电路仿真波形。

[关键词]EDA技术 数控分频器 VHDL语言

[中图分类号]TN-4[文献标识码]A[文章编号]1007-9416(2009)11-0108-02

1 引言

数控分频器广泛应用在家庭数字音响、通信设备时序电路、数字频率计中。另外,近年来已成为电子竞赛设计中常用的单元模块。笔者在连续三年指导学生电子设计竞赛过程中都用到了数控分频器。

用传统的设计方法设计数控分频器时,典型的设计是采用具有预置数据输入端的通用计数器芯片按设计要求完成。但当分频系数较大时,需用多片集成计数器和设计更复杂的控制电路来实现,且设计成果的可修改性和可移植性都较差。尤其是对于参加电子设计竞赛的学生,在有限的3-5天时间内要完成一个指定功能的设计,尤其不适合采用这种传统的“固定功能的集成电路+连线”的设计模式。

基于EDA技术的数控分频器设计,采用的是用软件的方法设计硬件的EDA (电子设计自动化)技术。作为EDA技术重要组成部分的VHDL硬件描述语言是一种符合IEEE工业标准的建模语言。用它设计的数控分频器可作为一个模块,移植到很多数字电路系统中,且极易修改,只要修改程序中的某几条语句,就可使最大分频系数得到改变。整个设计过程简单、快捷。可从根本上减少硬件调试的时间,为总体设计完成争取宝贵的时间。

2 通用数控分频器的原理

数控分频器的功能就是当在输入端给定不同输入数据时,将对输入的时钟信号有不同的分频比,数控分频器可用计数值可并行预置的加法计数器设计实现。所以数控分频器功能的实质是分频电路,即将一个给定的频率较高的数字输入信号,经过适当的处理后,产生一个或数个频率较低的数字输出信号。

3 数控分频器的设计思路

在数字逻辑电路设计中,分频电路是一种基本电路其本质是加法计数器的变种,计数值由分频常数N=fin/fout决定,其输出不是一般计数器的计数结果,而是根据分频常数对输出信号的高、低电平进行控制。根据实际需要可分为整数分频和小数分频两种。

设计中通过对某个外部输入的或内部电路产生的给定频率进行分频,即可得到所需频率。整数分频器实现非常简单,可采用标准计数器,也可采用可编程逻辑器件设计实现。但在某些场合下,时钟源与所需频率不成整数倍关系,此时需采用小数分频器进行分频。如分频系数为2.5、3.5等半整数分频器。

4 小数分频器的原理及设计

4.1 小数分频器的原理

小数分频基本原理是采用脉冲吞吐计数器和PLL锁相环技术先设计两个不同分频比的整数分频器,然后通过控制单位时间内两种分频比出现的不同次数来获得所需要的小数分频值。如设计一个分频系数为10.1分频器时,可以将分频器设计成9次10分频,1次11分频,这样总分频值为: F=(9×10+1×11)/(9+1)=10.1。

从这种实现方法特点可以看出,由于分频器分频值不断改变,因此分频后得到信号抖动较大。当分频系数为N-0.5(N为整数)时,可控制扣除脉冲时间,以使输出成为一个稳定脉冲频率,而不是一次N分频,一次N-1分频。

4.2 小数分频器的设计电路

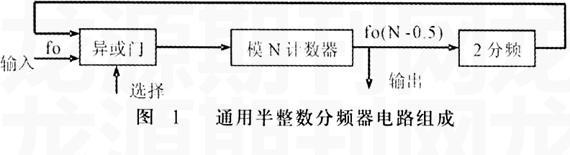

分频系数为N-0.5分频器电路可由一个异或门、一个模N计数器和一个二分频器组成。在实现时,模N计数器可设计成带预置计数器,这样可以实现任意分频系数为N-0.5分频器。图1是通用半整数分频器电路组成。

VHDL硬件描述语言,可实现任意模N计数器(其工作频率可以达到160MHz以上),并可产生模N逻辑电路。之后,用原理图输入方式将模N逻辑电路、异或门和D触发器连接起来,便可实现半整数(N-0.5)分频器以及(2N-1)分频如图1所示。

4.3 半整数分频器设计

4.3.1 模3计数器VHDL语言设计

该计数器可产生一个分频系数为3分频器,并产生一个默认逻辑符号COUNTER3。其输入端口为RESET、EN和CLK;输出端口为QA和QB。下面给出模3计数器VHDL描述代码:

entity counter3 is

port(clk,reset,en:in std_logic;

qa,qb:out std_logic);

end counter3;

architecture behavior of counter3 is

signal count:std_logic_vector(1 downto 0);

begin

process(reset,clk)

begin

if reset='1'then

count(1 downto 0)<="00";

else

if(clk 'event and clk='1')then

if(en='1')then

if(count="10")then

count<="00";

else

count<=count+1;

end if;

end if;

end if;

end if;

end process;

qa<=count(0);

qb<=count(1);

end behavior;

4.3.2 半整数分频器的设计

任意模计数器与模3计数器描述结构完全相同,所不同的仅仅是计数器状态数。通过设计一个分频系数为2.5分频器,用FPGA设计半整数分频器。该2.5分频器由模3计数器、异或门和D触发器组成。如图1所示。

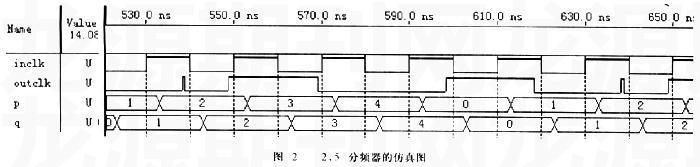

4.3.3 完整电路波形及仿真

将COUNTER3、异或门和D触发器通过图1所示的电路逻辑连接关系,并用原理图输入方式调入图形编辑器,然后经逻辑综合即可得到如图2所示的仿真波形。

由图中outclk与inclk的波形可以看出,outclk会在inclk每隔2.5个周期处产生一个上升沿,从而实现分频系数为2.5的分频器。设inclk为50MHz,则outclk为20MHz。因此可见,该电路不仅可得到分频系数为2.5的分频器(outclk),而且还可得到分频系数为5的分频器(q)。

5 结语

笔者在本设计过程中使用了MAX+ plusII、ispEXPERT、Foundation等EDA工具软件,并分别适配过当前国内FPGA/CPLD市场份额占有较大的三家公司Xilinx、Altera、Lattice的器件实现半整数分频的设计,经逻辑综合、仿真、并下载后运行效果都稳定、可靠。

[参考文献]

[1] 潘松,黄继业.EDA技术实用教程[M].北京:科学出版社,2005.

[2] 谭会生,张昌凡.EDA技术及应用.西安:西安电子科技大学出版社,2004.

[3] Xilinx inc.DATA BOOK Xilinx Incorporation San Jose Use,1999.