基于FPGA的TVP5150控制实现

郑培秋 董慧颖 张启东

[摘 要]介绍了视频输入处理芯片TVP5150的功能与特点,着重分析了基于EP1C20控制TVP5150的硬件接口及对具有ITU-R BT.656格式的数字图像数据读取与处理。

[关键词]EP1C20 TVP5150 数字图像 ITU-R BT656

[中图分类号]TN911[文献标识码]A[文章编号]1007-9416(2009)11-0006-02

引言

在图像处理系统的前端,多采用高度集成的视频解码芯片实现图像的采集功能。TI公司的视频解码芯片TVP5150以其卓越的性能和高性价比广泛地得到应用,它能将模拟视频信号转换成为符合ITU-R BT.656标准的数字信号,可以很方便的利用FPGA来进行信号处理。本文就是利用EP1C20配置成控制器通过IIC总线控制,设置TVP5150的工作状态,读取与存储标准的数据。

1 TVP5150的基本功能与特点

TVP5150是TI公司的一种可编程视频输入处理芯片,采用CMOS工艺。内部包含两路模拟处理通道,能实现抗混叠滤波、9位A/D转换、自动箝位、自动增益控制(AGC)、时钟发生(CGC)、多制式解码、亮度,对比度,饱和度控制(BCS)和多标准VBI数据解码等功能。

TVP5150是超低功耗、支持NTSC/PAL/SECAM等格式的高性能视频解码器,在正常工作时,它的功耗仅115 mw,并且具有超小封装(32脚的TQFP),因此非常适用于便携、批量大、高质量和高性能的视频产品。它可以接收2路复合视频信号(CVBS)或1路S-Video信号。通过FPGA配置成的IIC总线控制器设置内部寄存器,可以输出8位4:2:2的ITU-R BT.656信号(同步信号内嵌),以及8位4:2:2的ITU-R BT.601信号(同步信号分离,单独引脚输出)。

2 IIC总线简介

2.1 IIC总线的基本原理

IIC串行传输总线提供了比较完善的总线协议,以二根信号线(双向数据线(SDA)和串行时钟线(SCL))实现了完善的全双工同步数据传输,并且接口电路简单,可以极方便地构成多机系统和外围器件扩展系统,因而得到了广泛地应用。

IIC总线备用时SCL和SDL都必须保持高电平状态,只有关闭IIC总线才使SCL钳位在低电平。数据传输时,在SCL高电平期间SDL必须保持有稳定的逻辑电平状态,只有在时钟线SCL为低电平时,才允许数据线上的电平状态变化。总线上每一帧数据均为一个字节,但启动IIC总线后,传送的字节数没有限制,只要求每传送一个字节后,对方回应一个应答位。在发送时,首先发送的是数据的最高位,每次传送开始有起始信号,结束时有停止信号。

2.2 I2C总线信号时序

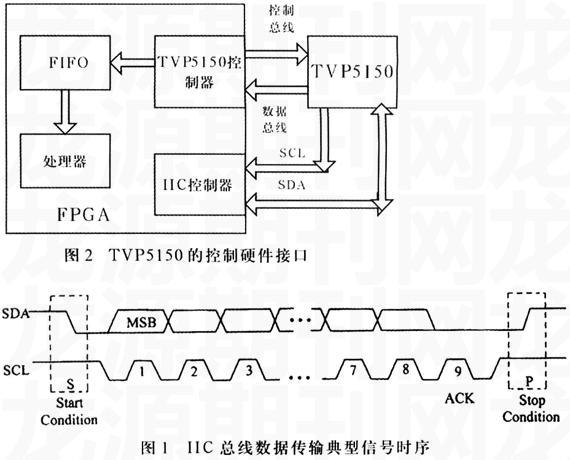

IIC总线是同步传输总线,总线信号完全与时钟同步。为了保证总线数据的可靠传输,对总线上的信号时序做了严格的规定,传输数据时有起始位(S),终止位(P),发送零及应答位(A),发送1及非应答位(A)。总线信号时序要求如图1所示。

(1)起始信号(s):在时钟SCL为高电平时,数据线SDA出现由高电平向低电平变化时,启动IIC总线。

(2)终止信号(P):在时钟SCL为高电平时,数据线出现由低到高的电平变化时,将停止IIC总线数据传送。

(3)应答位信号(A):IIC总线上第9个时钟脉冲对应于应答位。相应数据线上低电平时为“应答”信号(A),高电平时为“非应答”信号(A)。

(4)数据位传送在IIC总线启动后或应答信号后的第1—8个时钟脉冲对应于一个字节的8位数据传送。脉冲高电平期间,数据串行转送,低电平期间为数据准备,允许总线上数据电平变换。

3 FPGA控制TVP5150的硬件接口实现

FPGA具有体系结构和逻辑单元灵活、集成度高以及适用范围宽等特点。因此利用

FPGA的可编程实现视频解码器的控制是非常方便的,能根据所选解码器的不同编程实现各种功能。FPGA控制解码器的一般硬件接口如图2所示。

3.1 标准的BT.656并行数据结构

BT.656并行接口除了传输4∶2∶2的YCbCr视频数据流外,还有行、列同步所用的控制信号。一帧图像数据由一个625行、每行1728字节的数据块组成。其中, 23 ~311行是偶数场视频数据, 336~624行是奇数场视频数据,其余为垂直控制信号。

SAV和EAV信号有3字节的前导: FF、FF、00;最后1字节XY表示该行位于整个数据帧的位置及如何区分SAV、EAV。XY字节各比特位的含义为最高位为固定数据1;第六位F=0表示偶数场, F=1表示奇数场;第五位V=0表示该行为有效视频数据,V = 1表示该行没有有效视频数据; 第四位H=0表示为SAV信号,H = 1表示为EAV信号;第三位到最低位 P3~P0为保护信号,由F、V、H信号计算生成; P3 =V异或H; P2 = F异或H; P1 = F异或V; P0 = F异或V异或H。

3.2 TVP5150控制器在FPGA中的实现

根据BT.656的数据结构特点,利用内嵌信号EAV、SAV产生控制信号剔除完整帧中的无效的消隐信号。首先判断输入的数据是否含有三个前导字节FF、FF、00,因为含有这三个字节的数据可能是有效数据的开始或者结束,当判断到这个信号后,就可以开始接收有效数据。接收有效数据时必须严格按照从偶数场第一行开始,直到接收完完整一帧的数据,只有按照这个顺序接收数据才不会发生丢失数据等异常现象,这样做能够简化控制器的编程实现,详细的接收过程如图3所示。当接收满一帧后就存入FIFO中进行缓存,等待处理器进行处理。

4 结语

本文介绍了视频解码器TVP5150的特点,给出了FPGA控制该芯片进行BT.656格式数据的接收方法,该方法已经在FPGA某图像处理系统中验证过,这种接口的控制方便而简单,系统在整个数据传输中稳定可靠。IIC是一种简单的通讯协议,IIC总线是由数据线SDA和时钟SCL构成的串行总线可发送和接收数据,这在FPG中较容易模拟实现.

[参考文献]

[1] TVP5150PBS Ultralow-Power NTSC/PAL Video Decoder.Data Sheet.TI.2006

[2] 何立民.I2C总线应用系统设计.北京:北京航空航天大学出版社.1999.

[3] ITU2R BT.656-4.Interfaces for Digital Component VideoSignals in 5252line and 6252line Television Systems Operatingat the 4∶2∶2 Level [S].1998.