基于Σ-Δ ADC的伺服系统电流环带宽延拓技术研究

摘 要: 研究了基于Σ-ΔADC的伺服系统电流环带宽延拓技术,旨在提高电流采样精度和电流环带宽。设计了一种与PWM中心对齐的平均电流同步采样方法,以减少采样过程中的噪声和延迟。通过优化PWM更新时序并采用SINC3滤波器的同步策略,实现了电流采样时刻与PWM周期的精准对齐,从而降低了电流环中的谐波干扰。提出了PI分离控制策略,分别为比例控制器和积分控制器配置不同滤波器,以兼顾系统的动态响应和稳态精度。实验结果表明,所提方法使相电流中的谐波幅值降低了80%,转矩反馈波动降低了64%,电流过零点的延迟时间从1.5 ms缩短至0.5 ms,电流跟踪的正弦度显著提升,有效提高了伺服系统电流环的动态性能和稳态精度。

关键词: Σ-ΔADC; 电流环带宽延拓; 电流同步采样; PI分离控制; 伺服系统

中图分类号: TU852文献标志码: A 文章编号: 1674-8417(2024)09-0012-06

DOI: 10.16618/j.cnki.1674-8417.2024.09.003

0 引 言

Sigma-Delta型模数转换器(Σ-ΔADC)具有良好的微分和积分线性度,且只有1 bit数字输出,便于进行隔离处理,适合全数字伺服驱动系统使用。由于Σ-ΔADC的特性,后端需要通过滤波和抽取来实现多比特的信号重构,通常采用3阶SINC滤波器(SINC3滤波器)实现。SINC3滤波器的引入带来采样时间延长,且通常无法在每个PWM周期的固定时刻采样,造成采样到开关时刻或者死区时刻的虚假电流,引入电流噪声和外部扰动。此外,由于连续运行的SINC3滤波器的输出时刻与电流环使用该电流采样数据的时刻不同步,使得电流控制的延时无法补偿,电流谐波增加,电流环性能下降。为了获得低噪声高带宽的电流环性能,研究人员提出了新的SINC滤波器结构,优化同步策略,提高测量性能[1-2];Chen Li等[3]提出了基于卡尔曼滤波器的采样延迟补偿算法,提高系统的相位裕度和带宽。基于FPGA的电流采样和PWM更新时序优化方法,通过并行计算减少延迟,提高电流环带宽[4-7];连续时间可重构Σ-Δ调制器的低开关噪声高效率降压转换器技术则通过降低开关噪声,提高电流测量的精度和稳定性[8]。上述研究方法的算法复杂度较高,需要较多的计算和存储资源,通用性存在不足。本文提出一种基于Σ-ΔADC的中心

对齐电流同步采样方法,通过优化电流采样和PWM更新时序,降低电流采样的噪声,并通过PI分离的采样策略,延拓电流环的带宽。

1 中心对齐电流同步采样

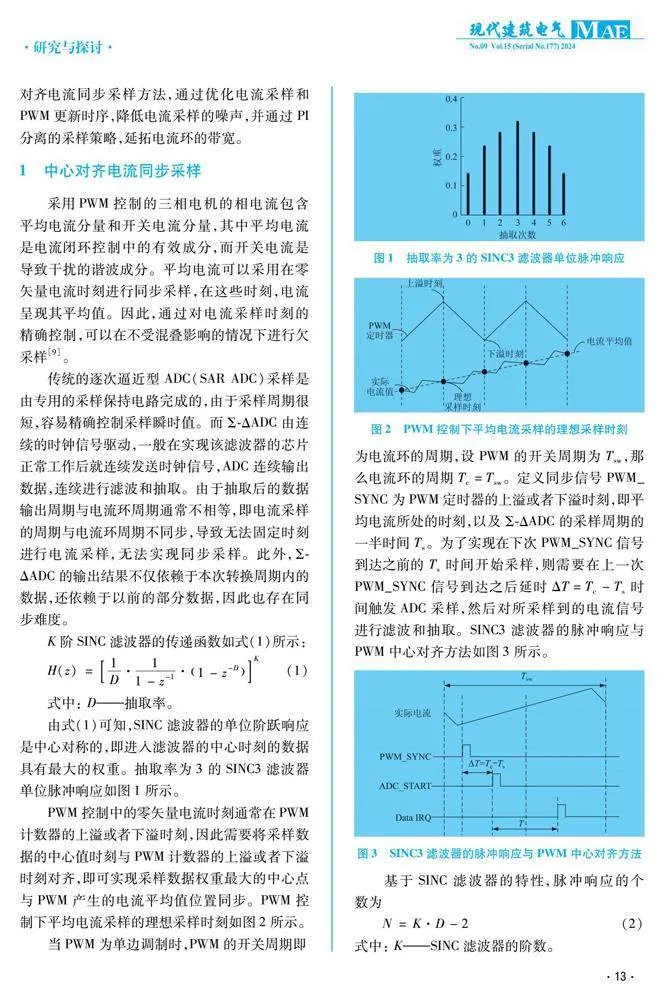

采用PWM控制的三相电机的相电流包含平均电流分量和开关电流分量,其中平均电流是电流闭环控制中的有效成分,而开关电流是导致干扰的谐波成分。平均电流可以采用在零矢量电流时刻进行同步采样,在这些时刻,电流呈现其平均值。因此,通过对电流采样时刻的精确控制,可以在不受混叠影响的情况下进行欠采样[9]。传统的逐次逼近型ADC(SAR ADC)采样是由专用的采样保持电路完成的,由于采样周期很短,容易精确控制采样瞬时值。而Σ-ΔADC由连续的时钟信号驱动,一般在实现该滤波器的芯片正常工作后就连续发送时钟信号,ADC连续输出数据,连续进行滤波和抽取。由于抽取后的数据输出周期与电流环周期通常不相等,即电流采样的周期与电流环周期不同步,导致无法固定时刻进行电流采样,无法实现同步采样。此外,Σ-ΔADC的输出结果不仅依赖于本次转换周期内的数据,还依赖于以前的部分数据,因此也存在同步难度。K阶SINC滤波器的传递函数如式(1)所示:

PWM控制中的零矢量电流时刻通常在PWM计数器的上溢或者下溢时刻,因此需要将采样数据的中心值时刻与PWM计数器的上溢或者下溢时刻对齐,即可实现采样数据权重最大的中心点与PWM产生的电流平均值位置同步。PWM控制下平均电流采样的理想采样时刻如图2所示。

当PWM为单边调制时,PWM的开关周期即

2 开关噪声消除滤波器

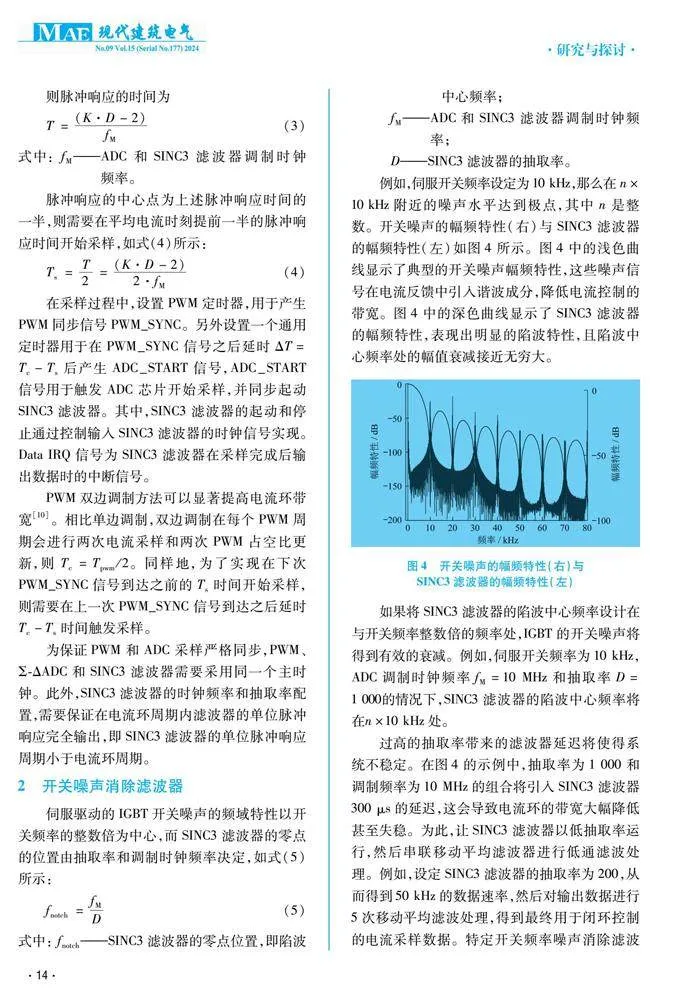

伺服驱动的IGBT开关噪声的频域特性以开关频率的整数倍为中心,而SINC3滤波器的零点的位置由抽取率和调制时钟频率决定,如式(5)所示:

3 PI分离电流采样

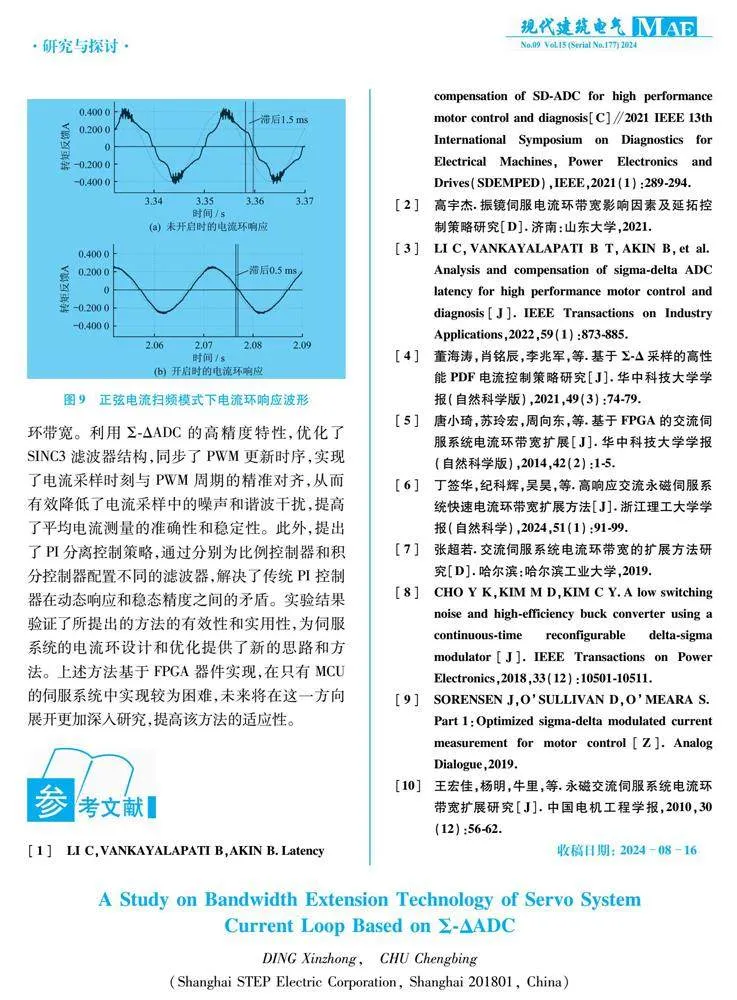

对于Σ-ΔADC而言,可以通过配置SINC3滤波器的抽取率在采样延迟和输出数据的精度之间合理选择。在高抽取率下,延迟较长但有效分辨率更高。在低抽取率下,情况相反。在比例-积分控制器(PI控制器)中,比例部分的作用是提供优异的瞬态性能,抑制负载变化,因此对反馈延迟敏感,但对反馈的准确度不敏感,宜采用低抽取率和低延迟的滤波器。而积分部分的作用是消除稳态误差,确保高精度的稳态性能,因此对于反馈的准确度有高要求,但对延迟不敏感,适宜采用高抽取率和高精度的滤波器。传统PI控制器的比例和积分部分都使用相同的反馈信号,这意味着信号需要兼顾两个控制回路的动态和静态性能,这对于SINC3滤波器而言是个矛盾。为此,将传统PI控制器中的比例部分和积分部分拆分,使用不同特性的滤波器输出反馈信号。基于PI分离电流采样的电流环控制器结构如图6所示。

分别对上述两种PI控制器结构进行频域分析。不同的电流反馈结构下电流环的闭环幅频响应如图7所示。图7(a)显示了传统PI控制器使用同一个反馈信号时的闭环幅频响应,SINC3滤波器延迟从0~80 μs的闭环响应。从图7中可见,随着延迟的增加,超调量越来越大,系统变得越来越不稳定。

使用PI分离采样的控制器结构时,设定比例控制器的SINC3滤波器的延迟为10 μs,仅改变积分控制器的SINC3滤波器的延迟,如图7(b)所示,可以看出延迟时间对系统的闭环稳定性影响很小。因此,PI分离采样的结构可以分别在电流环的动态性能、稳态精度和稳定性方面获得优异的闭环幅频特性。

4 实验验证

为了验证本文所设计方法的有效性,选用一套750 W的伺服驱动器和伺服电机作为被测对象,电机空载运行,使用伺服配套的上位机软件采样所需的信号。此外,为了进行性能对比,选用了30 m长的电机动力线缆和编码器线缆,由于更长的线缆会引入更大的寄生电容和寄生电感,使得IGBT的开关噪声更多地耦合到平均电流中。电机运行于零速或低速时,由于输出电流较小,所以基波电流中的谐波成分将占比更大,因此分别测试电机在零速和60 RPM下的相电流波形和转矩反馈的波形,用于验证中心对齐电流同步采样和开关噪声消除滤波器的效果。零速和60 RPM速度下的相电流和转矩反馈波形如图8所示。

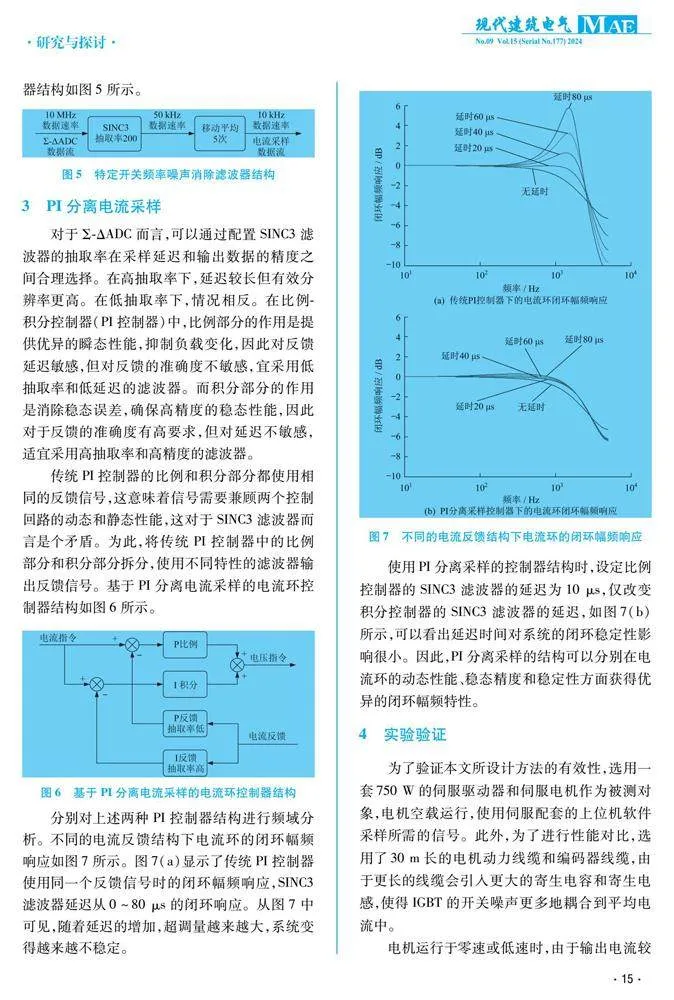

从对比实验数据可以明显看出,相电流中的谐波幅值衰减80%,转矩反馈的波动降低64%,且电机噪声明显降低。小电流下的电流跟踪性能决定了精密加工中的性能表现,实验中采用正弦电流扫频的方式测试10%额定电流下采用PI分离电流采样和中心对齐电流采样后的电流环瞬态性能。正弦电流扫频模式下电流环响应波形如图9所示。

实验结果可以看出,使用本文所设计的方法后,电流跟踪的正弦度大幅提升,且在电流过零点时的延迟时间从1.5 ms缩短到0.5 ms,电流环的小电流响应提高66.7%。

5 结 语

本文提出了一种基于Σ-ΔADC的中心对齐电流同步采样方法,并通过PI分离策略延拓电流环带宽。利用Σ-ΔADC的高精度特性,优化了SINC3滤波器结构,同步了PWM更新时序,实现了电流采样时刻与PWM周期的精准对齐,从而有效降低了电流采样中的噪声和谐波干扰,提高了平均电流测量的准确性和稳定性。此外,提出了PI分离控制策略,通过分别为比例控制器和积分控制器配置不同的滤波器,解决了传统PI控制器在动态响应和稳态精度之间的矛盾。实验结果验证了所提出的方法的有效性和实用性,为伺服系统的电流环设计和优化提供了新的思路和方法。上述方法基于FPGA器件实现,在只有MCU的伺服系统中实现较为困难,未来将在这一方向展开更加深入研究,提高该方法的适应性。

[1] LI C,VANKAYALAPATI B,AKIN B.Latencycompensation of SD-ADC for high performance motor control and diagnosis[C]∥2021 IEEE 13th International Symposium on Diagnostics for Electrical Machines,Power Electronics and Drives(SDEMPED),IEEE,2021(1):289-294.

[2] 高宇杰.振镜伺服电流环带宽影响因素及延拓控制策略研究[D].济南:山东大学,2021.

[3] LI C,VANKAYALAPATI B T,AKIN B,et al.Analysis and compensation of sigma-delta ADC latency for high performance motor control and diagnosis[J].IEEE Transactions on Industry Applications,2022,59(1):873-885.

[4] 董海涛,肖铭辰,李兆军,等.基于 Σ-Δ采样的高性能PDF电流控制策略研究[J].华中科技大学学报(自然科学版),2021,49(3):74-79.

[5] 唐小琦,苏玲宏,周向东,等.基于FPGA的交流伺服系统电流环带宽扩展[J].华中科技大学学报(自然科学版),2014,42(2):1-5.

[6] 丁签华,纪科辉,吴昊,等.高响应交流永磁伺服系统快速电流环带宽扩展方法[J].浙江理工大学学报(自然科学),2024,51(1):91-99.

[7] 张超若.交流伺服系统电流环带宽的扩展方法研究[D].哈尔滨:哈尔滨工业大学,2019.

[8] CHO Y K,KIM M D,KIM C Y.A low switching noise and high-efficiency buck converter using a continuous-time reconfigurable delta-sigma modulator[J].IEEE Transactions on Power Electronics,2018,33(12):10501-10511.

[9] SORENSEN J,O’SULLIVAN D,O’MEARA S.Part 1:Optimized sigma-delta modulated current measurement for motor control[Z].Analog Dialogue,2019.

[10] 王宏佳,杨明,牛里,等.永磁交流伺服系统电流环带宽扩展研究[J].中国电机工程学报,2010,30(12):56-62.

收稿日期: 20240816

A Study on Bandwidth Extension Technology of Servo System

Current Loop Based on Σ-ΔADC

DING Xinzhong, CHU Chengbing

(Shanghai STEP Electric Corporation, Shanghai 201801, China)

Abstract: This paper investigates a bandwidth extension technique for servo system current loops based on Σ-Δ ADC,aiming to enhance current sampling accuracy and current loop bandwidth.A center-aligned average current synchronous sampling method is proposed to reduce noise and delay during the sampling process.By optimizing the PWM update timing and adopting the synchronization strategy of the SINC3 filter,the precise alignment of current sampling moments with the PWM period is achieved,thereby reducing harmonic interference in the current loop.Additionally,a PI separation control strategy is proposed,configuring different filters for the proportional controller and the integral controller to balance the system’s dynamic response and steady-state accuracy.Experimental results show that the proposed method reduces the harmonic amplitude of the phase current by 80%,decreases torque feedback fluctuation by 64%,shortens the delay time at the current zero-crossing point from 1.5ms to 0.5ms,significantly improves the sinusoidal tracking of the current,and effectively enhances the dynamic performance and steady-state accuracy of the servo system current loop.Key words:

Σ-Δ ADC;extension of current loop bandwidth;synchronous current sampling;PI separation control;servo system