基于SIP 技术的固态硬盘电路设计

杨楚玮,张梅娟,沈 庆

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

0 引言

随着固态硬盘(Solid State Disk,SSD)小型化、高性能、高稳定性的要求越来越高,在确保安全稳定的前提下,提高集成度有利于存储系统体积的缩小和功耗的降低。然而,传统SSD 设计采用分离式设计方式,在PCB板级上多个芯片进行组合,各类元器件使得PCB 板卡面积庞大,且存在较严重的功耗和散热问题[1-3]。

SiP 技术可将SSD 控制单元、NAND 颗粒、电源管理等器件集成在一颗芯片上,达到降低存储系统体积的目的[4-6]。芯片间走线长度的减少能够降低高速读写信号的传输延迟和寄生效应[7],提高存储系统的传输性能及稳定性[8]。在产品应用方面,由于各类芯片管脚数和占用面积的降低,大幅降低了硬件设计的难度和风险。

针对传统SSD 分离式设计方式需要改善的问题,本文通过SiP 封装技术将SSD 控制单元、NAND 颗粒、SPI Flash 颗粒、电源管理等关键元器件集成在同一颗芯片内部的方式,实现和优化了存储系统。通过系统验证保证了设计的可靠性和正确性[9]。同时,通过SiP 存储系统和分离式存储系统的对比实现,获取了SiP 存储系统的相对小型化和性能优势。

1 系统总体设计

1.1 电路功能概述

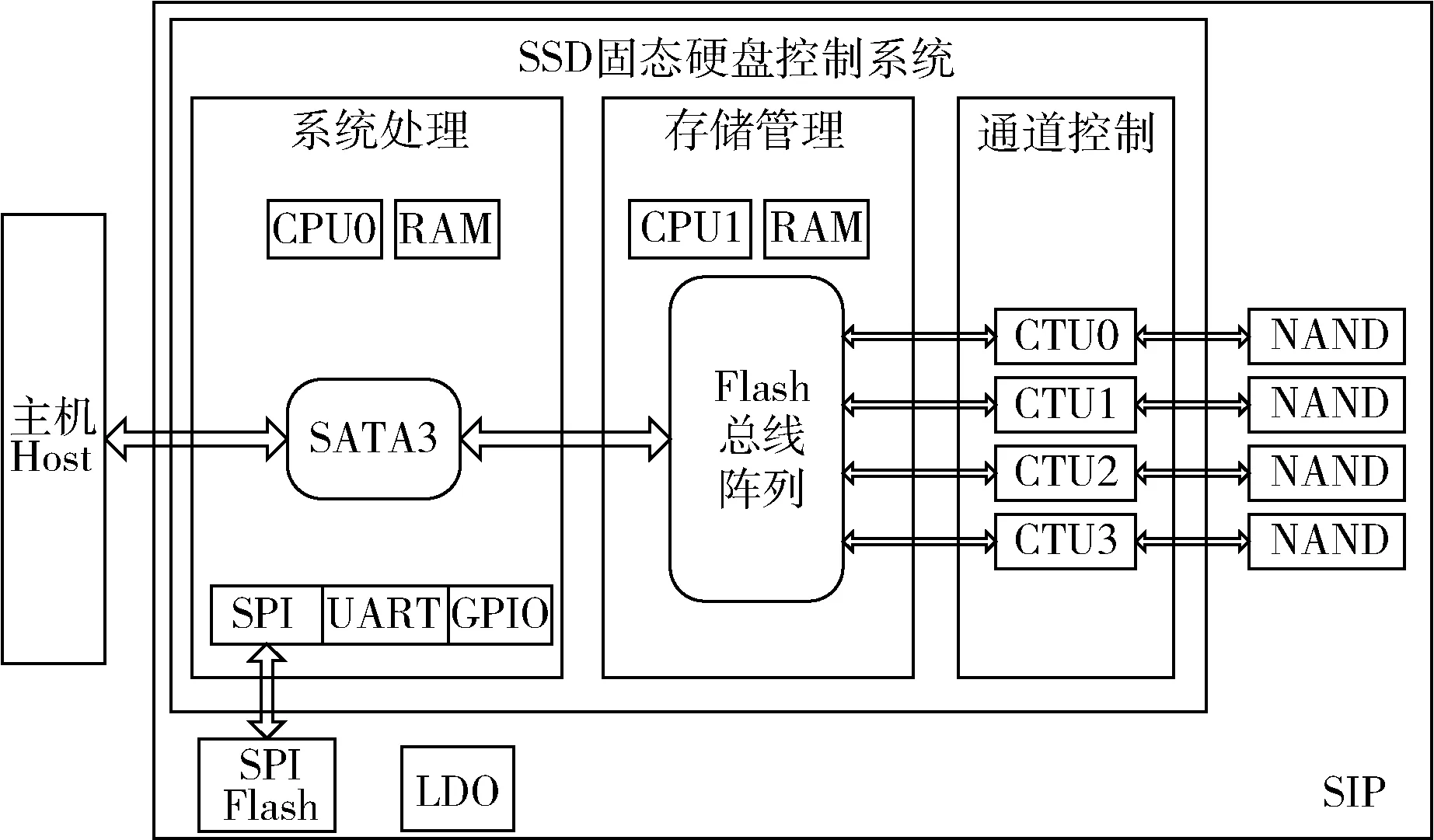

SiP 封装的固态硬盘电路功能框图如图1 所示。该SSD 控制系统的核心由系统控制单元SCU(System Control Unit)、系统存储单元SSU(System Storage Unit)、通道传输单元CTU(Channel Control Unit)三部分组成,其中SCU 负责系统启动和外设交互,SSU 负责固件算法运行和逻辑存储管理,CTU 负责执行SSU 对NAND 颗粒的物理操作。

图1 电路功能框图

其他主要外设接口包括:SATA 接口集成在SCU 内部,与外部主机Host 的SATA 接口进行交互;NAND 颗粒通过CTU 与SSD 控制模块相连,用于数据存储;外部SPI Flash 颗粒通过SPI 接口与SCU 相连,用于固件的存储。

1.2 系统控制单元

系统控制单元采用Cortex-M3 处理器作为主控,内部包括32 KB 的ROM 空间用于存储启动程序,1 MB的SRAM 空间用于运行SCU 固件处理程序及数据缓存。另外包含JTAG、SATA、SPI、UART、GPIO 等外设。

SCU 作为系统主控的基石,主要有固件分派、系统初始化、通信交互等功能。其中,固件分派是指系统上电后,SCU 的ROM Code 运行,通过SPI 接口加载SPI Flash 中的固件程序,并将固件程序进行分包派发到SCU、SSU、CTU 的SRAM 中;系统初始化指SCU 需要对SATA 接口以及其他外设进行初始化,并根据SSU、CTU 初始化完成情况决定整个系统初始化完成情况;通信交互指SCU 通过SATA 接口与主机进行各类帧信息结构FIS(Frame Information Structure)和数据的交互,并通过命令传输通道及DMA 数据传输通道与SSU 进行命令和数据传输。SCU 的工作流程如图2所示。

图2 SCU 工作流程图

1.3 系统存储单元

系统存储单元采用Cortex-M3 处理器作为主控,内部SRAM 由两部分组成,64 KB 的Code SRAM 空间用于运行SSU 固件处理程序;2 MB 的Data SRAM 空间划分成32 个16 KB 的FIFO 及6 个256 KB 的BUFFER,其中FIFO 用于缓存SCU 或者CTU 的命令及数据包,BUFFER 则用于NAND 映射表和坏块表的缓存。除此之外,SSU 内部还有5 个硬件加速引擎模块,用于庞大的映射表查找以及缓存复制,加速SSD 控制模块对命令的响应。SSU 内部硬件模块如图3 所示。

图3 SSU 内部硬件模块图

SSU 作为管理存储的核心部件,和存储传输层FTL(Flash Translation Layer)算法一起[10],对SSD 的存储性能、数据可靠性、使用寿命等方面具有决定性意义。SSU 的主要功能包括:处理与SCU 交互的命令和数据;处理与CTU 交互的NAND 操作命令;管理映射表、坏块表,实现FTL 算法,完成逻辑地址到物理地址的映射[11]。SSU 功能及与各控制单元的交互如图4所示。

图4 SSU 功能框图

1.4 通道传输单元

通道传输单元采用8-bit 的单片机PIC16 系列作为主控,内部包括:AES、SM4 硬件加密模块,对存取数据进行硬件加解密操作;扰码解码器,对存取数据进行硬件扰码解码操作;ECC 数据校验模块,对坏块或异常造成的少量数据异常进行纠错,纠错能力达到72 bit/KB。

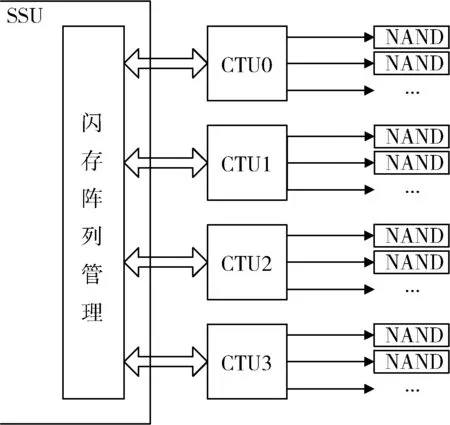

本SiP 电路共集成4 个CTU 模块,每个CTU 模块包含8 个CS 片选信号,最多可接32 个NAND 裸片,这种阵列式管理方式,为SSD 的高速度和大容量存储提供了可能。多CTU 模块同时对NAND 进行访问,通过提高数据访问的并行程度,达到加速访问的目的。通过多片选,CTU 采用流水线方式对裸片进行管理,不同时刻对不同裸片进行访问,提高了总线的利用效率,对SSD 的容量扩展和读写速率均大有裨益。CTU 阵列式管理如图5 所示。

图5 CTU 阵列式管理示意图

2 SiP 电路实现

2.1 电路设计

固态硬盘电路通过SiP 封装将SSD 控制模块芯片、NAND 颗粒、电源控制芯片LDO、SPI Flash 颗粒、贴片电阻、贴片电容等器件集成在同一电路腔体中,其腔内器件的位置如图6 所示。

图6 SiP 系统封装示意图

NAND 颗粒作为SSD 主存储空间,存储单元架构采用单层单元SLC(Single-Level Cell)模式,相比其他多层单元存储具备更长的使用寿命,存储容量为单片8 GB,共使用了4 只裸片,在SiP 腔内采用了两两堆叠的结构存放,有效降低了芯片面积[12]。SPI Flash颗粒存储容量为单片256 KB,其作用在于为控制单元的固件和配置信息提供存储空间,其位置紧邻SCU,通过SCU 的SPI 接口进行访问。电源控制芯片LDO 单元的输入电压范围为1.1 V~5.5 V,输出电压范围为0.8 V~3.6 V,其作用为将3.3 V 转换为1.8 V给系统供电。

2.2 封装结构设计

SSD 固态硬盘控制单元采用65 nm 工艺,SiP 电路面积为24.49 mm×14.24 mm。封装形式BGA145,装片采用导电胶粘接工艺,键合采用铜丝球焊工艺,塑封料模封,标记采用激光打印工艺。本电路的基板布局结构如图7 所示。

图7 基板布局图

2.3 信号完整性设计与仿真

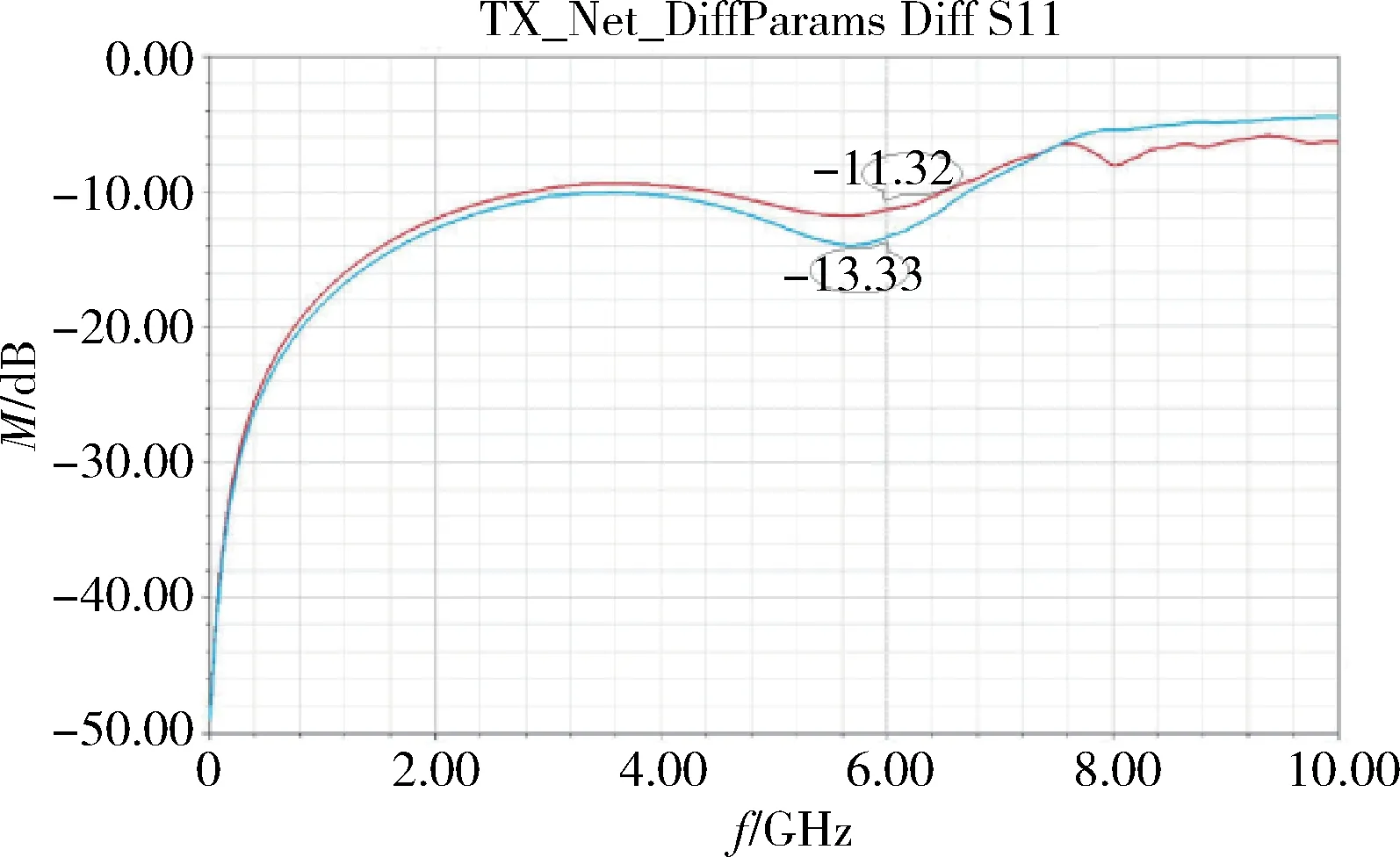

本设计中SATA 接口采用SATA3.0 协议,工作频率高达6 GHz,差分信号在传输线上传播时,很容易因为阻抗的变化发生信号反射现象。为了消除信号反射,要在两条信号线末端跨接端接匹配电阻,此处在电路RX 设计时内部带匹配电阻,并外部留有电阻校准接口。此外,在设计中需要将驱动器间错位和两线的不对称做到最小化,最大程度降低共模干扰导致的差分信号失真。图8 为SATA TX 信号的插入损耗仿真图,在6 GHz 工作频率处插入损耗较小,信号衰减较小。图9 为SATA TX 差分信号回波损耗仿真图,在6 GHz 工作频率处差分信号的回波损耗均保持在较大水平,回波较小。仿真结果显示TX 信号在工作频率处传输性能较好。

图8 插入损耗仿真波形图

图9 回波损耗仿真波形图

3 系统验证

3.1 软硬件环境

系统验证的硬件环境包括:电路测试板、最小系统板、带SATA 口主机、1.2 V 电流测试模块、3.3 V 电流测试模块及USB 转SATA 子卡。详细功能如表1 所示。硬件环境搭建框图如图10 所示。

表1 硬件资源

图10 硬件环境框图

系统验证的软件环境包括:控制单元固件烧写软件MPTool,如图11 所示;ATA 基础命令测试软件Bus Hound;SSD 性能测试软件TxBENCH。

图11 固件烧写软件图

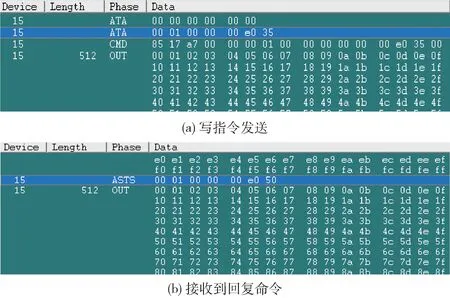

3.2 ATA 命令测试

写入命令测试:使用Bus Hound 软件,选择要检测的SSD;打开Bus Commander 窗口,选择ATA 指令;选择Load,打开待测试文档(test.db)导入数据;选择发送WRITE DMA EXT 35 指令,数据长度为512。通过Capture 窗口可确认WRITE DMA EXT 35 写指令命令发送成功,如图12(a)所示,并接收到ASTS 回复命令,显示传输OK,如图12(b)所示。

图12 数据写入命令交互截图

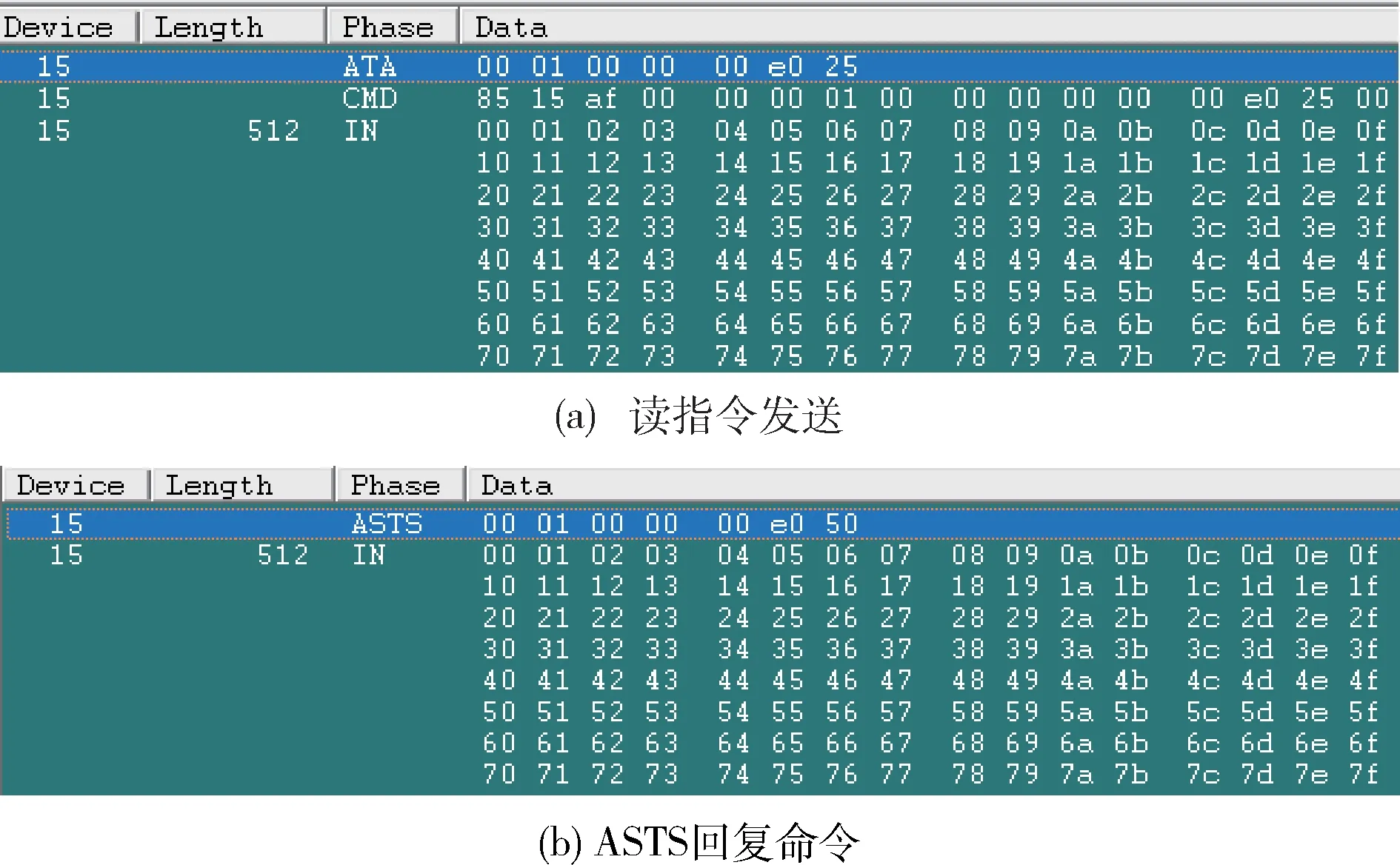

读取命令测试:打开Bus Commander 窗口,选择ATA 指令;选择发送READ DMA EXT 25 指令,数据长度为512。通过Capture 窗口可确认READ DMA EXT 25读指令命令发送成功,如图13(a)所示,并接收到ASTS回复命令,显示传输OK,如图13(b)所示。

图13 数据读取命令交互截图

根据图12 和图13 交互命令显示写入数据和读取数据保持一致,ATA 命令对SSD 读写功能正常。

3.3 性能测试

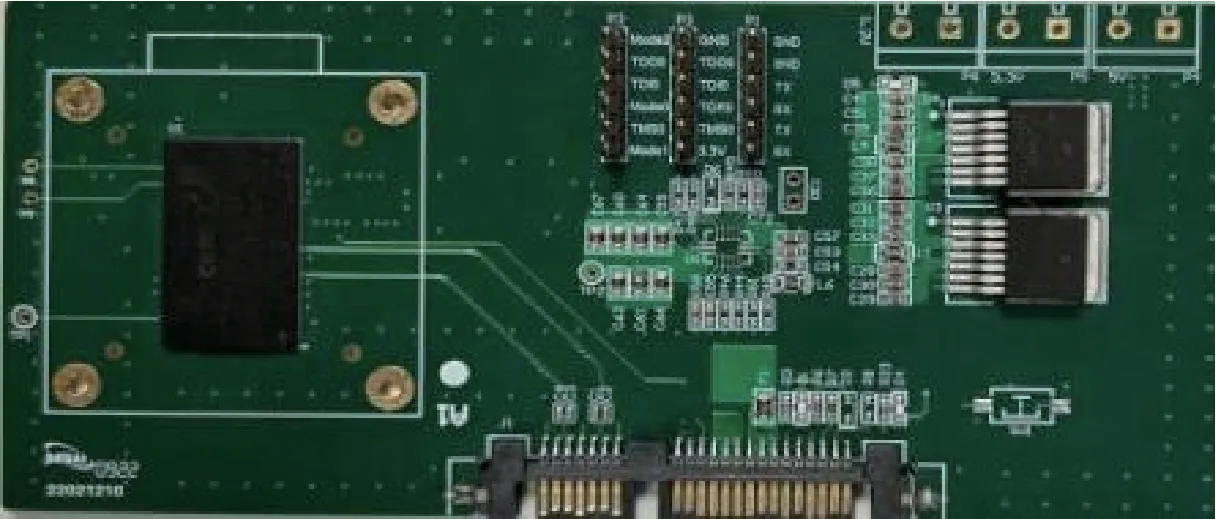

性能测试首先对使用SiP 封装电路的测试板进行测试,如图14 所示,然后对使用相同元器件独立封装的电路测试板进行测试,如图15 所示,最后对两组测试结果进行对比分析。

图14 SiP 封装测试板

图15 非SiP 封装测试板

性能测试使用TxBENCH 软件,进行连续读写和随机读写两种类型的测试[13],总数据块大小为256 MB。此外,随机读写的数据块分为最大数据128 KB 和实际使用频率最高的4 KB 两种情况;队列深度参数分为QD1 和QD32 两种情况,该参数用于反映SSD 在多线程并发环境下的性能。具体测试项如表2 所示。

表2 性能测试项

性能测试结果如图16 所示,图16(a)为SiP 封装电路结果,图16(b)为非SiP 封装电路的性能测试结果。结果分析可知SiP 封装电路比非SiP 封装电路在4 个测试项上均有不同幅度的提升。连续读写性能有一定的提升,但是提升幅度较小。随机读写的性能提升较大,尤其是数据块大小为4 KB 时的写数据性能提升一倍多,究其原因,写操作相对而言速度较慢,且随机小数据块写需要高频次主机和设备交互,这些特点凸显了SiP封装大幅缩短SSD 控制模块到NAND 颗粒距离的优势,写操作速率和稳定性均大幅提升[14-15]。

图16 性能测试结果

4 结论

随着SiP 集成技术的日趋成熟和存储系统小型化、高性能的需求,设计一款基于SiP 封装的存储系统电路能够实现存储系统各类电路高度集成以及芯片间走线的大幅减少,达到小型化、高性能需求。

本文基于SiP 技术和全国产化器件实现了一种固态硬盘存储电路的设计。与传统分离式电路的SSD 产品相比,将SiP 技术应用在国产SSD 上给存储系统带来了高性能、低功耗、小型化、高稳定性、高安全性等诸多优势。通过验证,证实了SiP 技术应用于存储系统的可行性,并对SSD 的随机读写性能带来了大幅提高,为后续SiP 封装存储系统的实现提供了设计思路和验证方法[16]。