应答器读写装置数据流解码单元的方案设计

梁嘉艺,范俊成

(浙江纺织服装职业技术学院机电与轨道交通学院,浙江宁波)

应答器是一种用于地面向列车传输信息的点式设备,分为有源和无源2 种[1]。随着高铁建设的快速发展,应答器在列控系统中被广泛使用。结合应答器设备现场维护的需求,应答器报文读写工具是现场维护必不可少的设备。本文提供一种利用基于FPGA 的解码串口数据信号的电路单元及检测串口数据流的方案设计,应用该设计解码串口数据,能够更快速、更精确,且使用简单,方便携带,弥补了目前应答器读写装置无法判定LEU 工况的功能缺失。

1 现有应答器读写装置方案分析

1.1 现有应答器读写装置方案

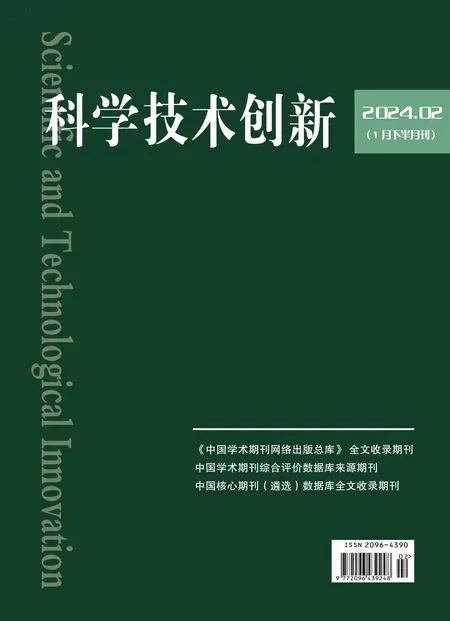

目前在用的应答器读写装置主要由电源单元、信号处理单元、核心处理单元、数字处理单元,显示单元等组成,如图1 所示。该装置可以对无源应答器和有源应答器进行报文的读写及分析,读取的报文即时显示在液晶屏幕上,具有读取记录查看功能,功耗低,具备待机休眠功能[2]。

图1 应答器读写装置组成框图

1.2 现有方案存在的问题

在TCC 与LEU 之间的命令传递中,传输距离短、传输数据量少、传输频率快,且呈现周期性,因此实际应用中最常采用异步串行通信协议,根据不同传输距离及可靠性需求,选择RS232、RS422 以及RS485 等串行通信[3]。目前应答器读写装置可以对现场的无源应答器及有源应答器进行报文的读写操作,但无法对TCC 与LEU 间的串口通信数据进行监测,即无法对串口数据进行解码[4]。

由于每条铁路线路使用的TCC 所属生产厂家不尽相同,TCC 与LEU 的串口会出现多种形式(RS485、RS232 等),并且大多情况下无法获得通信的波特率,因此在对该串口进行数据解码时通常使用示波器反复采集正负电平变化图像,通过肉眼观察数据波形变化,然后猜测波特率,进而解码数据内容。这种方法不仅效率低下、不能保证解码的准确性,且示波器不易携带、截图分析等操作繁琐。

2 应答器读写装置数据流解码单元设计方案

为解决现有方案存在的问题,提出了一种利用基于FPGA 的解码串口数据信号的电路单元及检测串口数据流的设计方案。应用该设计解码串口数据,能够更快速、更精确,且使用简单,方便携带。解码单元独立于应答器读写装置存在,与读写装置之间通过USB 总线通信,通过USB 总线可以给解码单元进行供电同时解码单元解码出的数据可以通过USB 总线上传给应答器读写装置,并和应答器读写装置读到的有源应答器的报文进行比对以此判断出LEU 工况。应答器读写装置与其它外部设备的关联如图2 所示。

图2 应答器读写装置与外部设备关联

2.1 主解码芯片的选择

单片机、DSP 等嵌入式器件虽然计算能力强,但是指令周期过长,通常都在4 个时钟周期以上,无法满足本发明的检测精度。因此选用每1 个时钟周期能够做出反应的FPGA 作为核心运算芯片。

FPGA 由于具有并行处理能力,且执行效率高,对时钟周期反应敏锐的特点,一直被工业产品广泛采用。利用FPGA 能够精确检测算出数据流的波特率,以此确保解码的准确性。本解码单元中FPGA 芯片采用EP1C3T144C8,该FPGA 是A1tera 公司2003 年9月份推出的,基于1.5v,O.13μm 工艺,Cyclone 是一个性价比很高的FPGA 系列。其中EPlC3T144 是Cyclone 系列中的一员,共有2910 逻辑单元,59904RAM bits,1 个PLLs,最多有104 个用户I/O,可以说这款FPGA 的资源非常丰富,足够满足大型设计的需要[5]。

2.2 解码单元的硬件方案设计

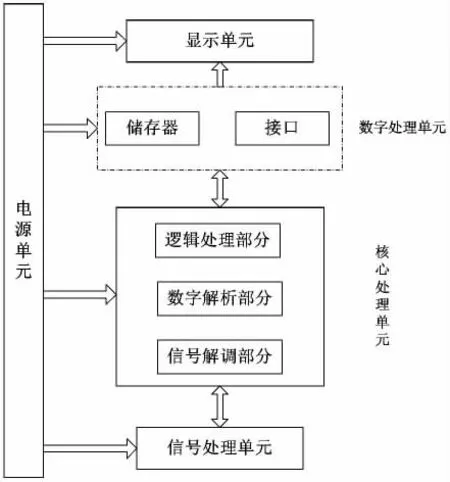

设计三部分电路:数据采集区域、数据输出区域、解码区域。为搭建上述电路,本设计选用主要器件如下:数据采集、与输出接口均采用标准的DB9 接口。解码区域中,选用6 个共阳极七段数码管,用以显示波特率;解码区域中,采用基于FPGA 主控制电路。图3示意了本方案三大区域布局。

图3 硬件设计区域划分示意

数据采集区域,三个端口,均配有按键,用于使能检测波特率;数据输出区域,使用USB 串行通信接口。数据输出区域,配有一个按键,用于使能发送,将接收到的数据不断发送给应答器读写装置;解码区域完成波特率检测、数据接收并存储、波特率显示、以及发送控制等功能。

2.2.1 解码区域的电路设计

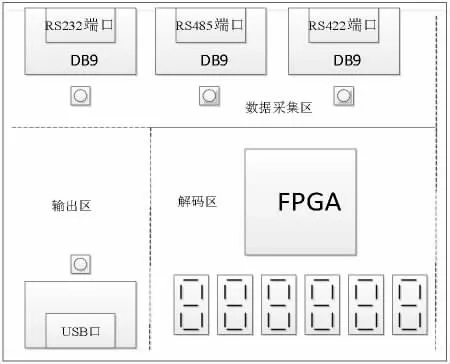

解码区域是以FPGA 芯片(EP1C3T144C8)作为主控制单元解码核心部分,外围包括了JTAG 电路、电源电路、复位电路和外围的数码管电路。图4 为解码区域的电路原理框图。

图4 解码区域的电路原理框图

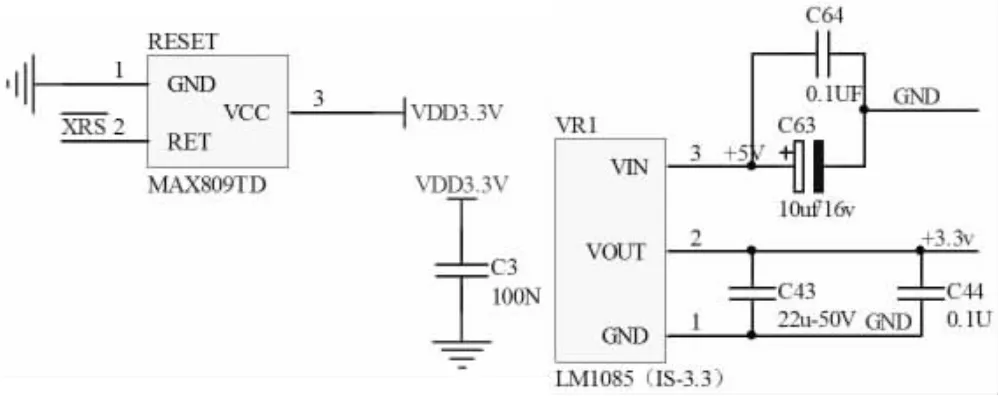

电源电路采用LM1085 系列芯片为FPGA 提供稳定的电源,通过与应答器读写装置通信的USB 通信口获得DC5V,并将DC5V 转换成DC3.3V 和DC1.5V 给FPGA 供电。复位电路采用了电源监测芯片MAX809TD,用于监测电源电路中的DC3.3V 的工况,一旦DC3.3V 的供电小于该芯片的阈值(2.8V 左右),该芯片就会输出低电平使FPGA 复位。图5 为电源电路(输出DC3.3V)和复位电路的电路原理。JTAG 模式接口电路与数码管电路为通用常规电路,在此不进行赘述。

图5 电源电路和复位电路原理

2.2.2 输出区域的电路设计

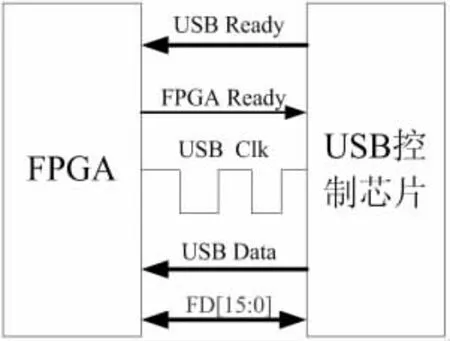

图6 为FPGA 与USB 控制芯片的连接,USB 控制芯片选用Cypress 公司的CY7C68013。USB_Ready 为USB 芯片状态标志,低电平有效;FPGA_Ready 为FPGA 芯片状态标志,低电平有效;USB_Clk 为USB 向FPGA 传送指令的指令时钟,USB_Data 为USB 传送给FPGA 的控制指令;FD[15:0]为USB 与FPGA 交互的数据。

图6 FPGA 与USB 控制芯片的连接

2.2.3 采集区域的电路设计

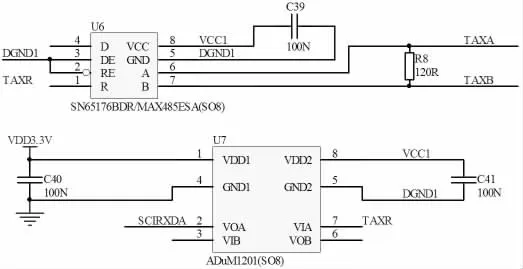

采集区域均为异步串行通信,三个串行口总线形式分别为RS232、RS485 及RS422,由于本解码单元知识接收TCC 发送给LEU 的串行数据,因此电路设计时只进行了接收电路的设计,图7 为RS485 总线的接收电路。接收采用了ADuM1201(SO8)芯片进行隔离设计以防止外部干扰对总线的影响。通信电平转换芯片采用了MAX485ESA(SO8),将差分信号转换为单端信号输入FPGA。其它两种总线电路与RS485 总线的设计思想相同,在此不再进行赘述。

图7 RS485 总线的接收电路

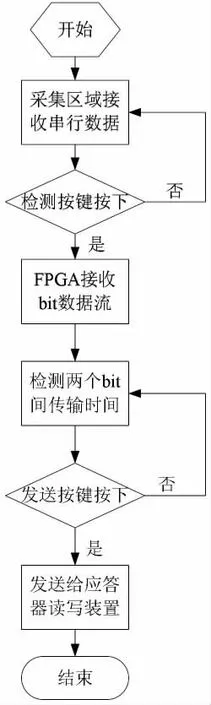

2.3 解码单元解码的具体实施方式

将被采集数据连接到采集区域的某一端口,以RS485 端口为例,电路板上电后,数据流通过采集区域的RS485 端口进入解码单元。按下RS485 端口对应的按键,采集区域将RS485 差分信号解码为串行数据,发送至解码区域的FPGA。FPGA 从接收到第一个位数据开始计时,得到串行数据中每个位之间发送的间隙时间。FPGA 自动重复上述计时过程,可以得到许多组位间传输时间,选择其中间隙最小的时间作为基础参数,加以计算确定该数据流的波特率。将计算得到的波特率存储,同时发送给数码管显示。当看到数码管显示出数据时,可以按下发送按键,被测数据流此时能够发送给应答器读写装置,在应答器读写装置端能够方便地看到具体数据内容,至此实现串口数据流解码。再次按下此按键,停止发送数据。如需重新检测波特率,可以在停止发送数据后,再次按下采集区域的对应端口按键,重新检测。其它被检测端口的工作过程,与上述内容相同,不再复述。图8 所示为解码单元的解码方式具体实施的工作流程。

图8 解码单元的工作流程

由于数据流发送均在us 级别,因此检测位时间过程在1 ms 以内可以完成,上述所有操作,理论上不足1 s 即可完成,效率远高于使用示波器肉眼解码。解码单元晶振使用25 Mhz,因此对于高达115 200 bps 计算,误差在0.4%以内,随着波特率降低,传输检测的误差将更小,能够满足研发和测试的需求[6]。对应端口的检测按键按下一次后,FPGA 自行迭代检测多次后再确定波特率,因此检测结果更接近真实波特率值。

结束语

本文指出了现阶段应答器读写装置存在的无法获取TCC 与LEU 通信数据的不足,设计了基于FPGA的应答器读写装置解码单元以此解决目前应答器读写装置存在的问题。本文给出了解码单元的硬件设计以及解码方式的具体实施流程,设计过程具体详细。目前系统处于试验阶段并在现场进行实际运用的检验。通过现场反馈,其性能稳定可靠,准备进一步的测试并推广运用。