基于FPGA的LVDS+RS422远距离高速通信设计与实现

赵冬青,王越涛,李东星,武慧军

(1.中北大学仪器与电子学院,山西太原 030051;2.中北大学电子测试技术与重点实验室,山西太原 030051;3.北京航天长征飞行器研究所,北京 100071)

随着时代的不断进步及科技的高速发展,远距离高速率数据传输技术逐渐趋于成熟,同时要求传输的数据量越来越大,传输速率越来越快。由于对环境因素掌握不全面,恶劣环境下将不利于数据测试[1]。基于此,设计了远距离高速数据传输测试设备。长线电缆将设备引至安全地点测试,保障了测试人员与设备的安全。

由于远距离并行传输数据成本高,布线工艺复杂,且每一位同时传输导致误码率的不可控,种种因素限制着远距离并行传输的发展。文中采用的串行传输,在误码率、传输速率等方面都有着并行传输无可比拟的优势。串行传输的接口标准有RS232、RS422和LVDS(Low Voltage Differential Signaling)等。故在方案设计中,综合各总线接口的优缺点,同时兼顾考虑到传输距离、速率及可靠性等因素,选用RS422 通信协议进行上位机、待测设备指令与状态的交互,LVDS 进行远距离数据传输[2]。以FPGA 为控制核心,实现了数据远距离高速传输存储,同时添加8B/10B 校验码,降低了误码率。

1 系统总体方案设计

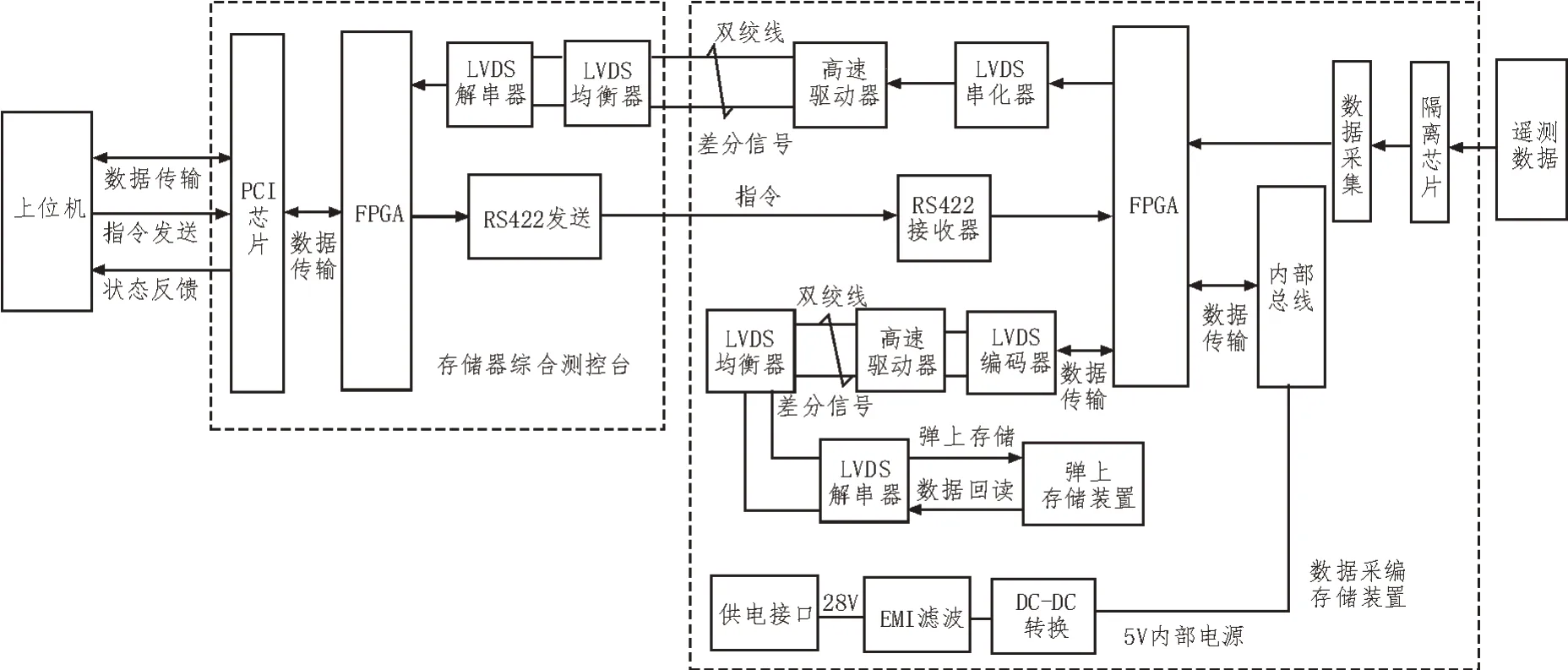

数据传输系统由上位机、存储器综合测控台和数据采编存储装置组成[3]。如图1 所示,数据采编存储装置用于采集遥测数据并进行编码存储,存储器综合测控台负责回读采编到的数据,上位机软件发送回读指令并将回读数据进行分析[4]。由于采编装置与遥测数据的两个电路之间存在接地环路,为阻断共模、浪涌信号的传播,硬件上增加了隔离芯片,通过电气隔离,提高了数据采编存储装置的安全性和可靠性。

图1 系统总体设计

为实现地面测控台高速回读数据采编存储装置记录的遥测数据,采用LVDS 作为收发接口。地面测控台向外发送RS422 回读指令,数据采编存储装置在接收到回读指令后,由FPGA 控制数据经串化器并转串后进行传输。因为数据经长线传输后会有不同程度的衰减,为了提高LVDS 信号的传输速率与传输距离[5],在数据发送接口增添高速驱动器,同时在数据接收端增加均衡器以进行信号补偿,电平信号识别的准确率得到提高。LVDS 信号传输采用双绞屏蔽线QX2539 作为传输介质,由于其每30 m 衰减11 dB,而均衡器CLC014 最大可以恢复40 dB 的电缆衰减,故传输距离可达90 m。

2 硬件电路设计

2.1 LVDS发送端电路设计

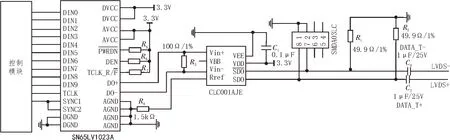

LVDS 是一种差分信号的传输方式,可一对一或一对多进行信号传输[6]。当信号经过两条平行的差分线后,由于接收端仅关注两电平的差值,又因为该传输标准采用电流模式驱动输出,不会受到信号切换或阻尼振荡的影响,故具有良好的抗电磁干扰(EMI)特性。同时有低电压(250~450 mV)传输的特点,故振幅较小,功耗较低,电平转换快。发送端电路如图2 所示。

图2 发送端电路设计

存储器综合测试台的LVDS 接口主要用于实时监测数据和存储器数据的下传。LVDS 发送端以SN65LV1023A 为主要芯片,由芯片资料可知,其数据传输速率区间为100~660 Mbit/s。FPGA 输出的并行数据经该芯片后全部转化为串行输出,在电路板内嵌时钟的协调下有效地降低了时钟与数据不同步造成的传输误码错误,提高了传输可靠性。DIN0-DIN9 是十路并行数据信号接口,TCLK 为时钟信号口,经串化器输出一对差分串行信号D0+和D0-,在高速驱动器CLC001AJE 的驱动下稳定传输。

在发送端增加的静电保护芯片SMDA03LC-LF有效地降低了芯片被浪涌电压击穿的风险。R5、R6、R7分别为1 kΩ的电阻,上拉至3.3V 限流。发送芯片与驱动器之间接入的R3电阻,将对两条差分信号线进行阻抗匹配;同时尽量靠近驱动器引脚进行布线可有效降低干扰。LVDS 输出的电压值由1.5 kΩ的R4进行调节,R1、R2取49.9 Ω精度1%的电阻为发送电路做阻抗匹配[7]。

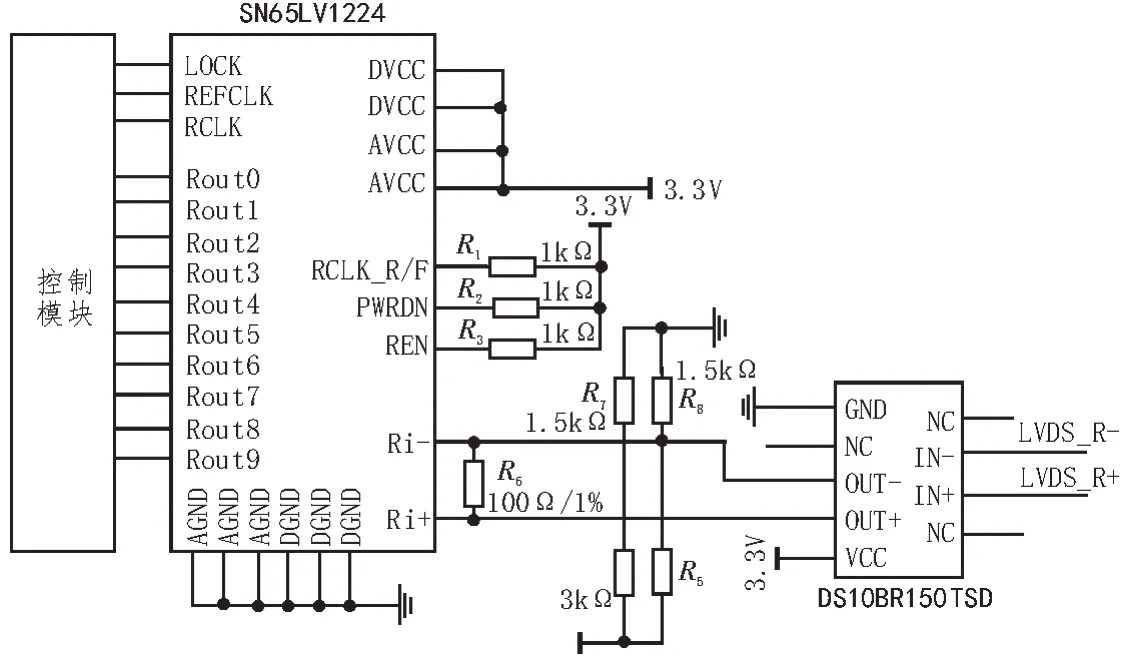

2.2 接收端电路设计

当信号进入接收端,经缓冲芯片缓冲后,SN65LV1224解串器将一对串行差分数据解码为数据和时钟信号并由FPGA 进行处理。R1、R2、R3为1 kΩ电阻,通 过3.3 V上拉电压进行限流。接收端电路如图3所示。

图3 接收端电路

为加强电路板和电缆的抗干扰能力,电路设计时采用双隔离式LVDS 缓冲器芯片DS10BR150TSD,其自带8 kV PK 增强型隔离电压,具备静电释放(15 kV 以内)和带电插接保护的功能;由于其可将信号传输路径细分为很短的区段,故可在整个信号路径上控制阻抗以遮蔽阻抗误配,降低信号衰减,使信号完整性得以保证;并且也因为不需使用高成本的高频连接器,降低了开发成本,提升了系统的运作效能。由于芯片具有低辐射、低功耗和高电磁抗扰度等特性,在设计中提高了可靠性并节省了布板空间[8]。

经远距离传输后,接收端接收到的信号电平会部分衰减,少数信号会由于幅度衰减严重而导致解串器无法判断其处于高电平或低电平,从而出现误码。如图4 所示,由于电平衰减幅度与电缆长度和信号频率成正比,因此当接收到信号后,要对信号进行美化,修正其幅频和相频等关键参数。采用的LVDS 缓冲器可将信号恢复,修正后的波形如图5 所示。经示波器抓取判断,高低电平摆幅基本一致,高低电位区别显著,解串器解串正确率大幅提升。

图4 LVDS经长电缆后传输波形

图5 LVDS修正后的波形

2.3 RS422指令交互的可靠性设计

RS422 是一种支持多点通信,传输方式为差分传输的协议,因具有较强的抗干扰能力而被广泛运用于多个领域[9]。两设备在进行通信时,通常采用隔离电路可避免互相干扰和异常信号导致的接口损坏。传统RS422 电路进行隔离设计时通常为协议芯片、电源隔离芯片和光耦相连接的方式,电路较为复杂,开发成本高。而ADM2682E 芯片内部集成了隔离式DC/DC 转换器,同时可配置为全双工或半双工模式,极大简化了电路结构,降低了成本。RS422 收发接口电路如图6 所示。

为提高收发的稳定性和安全性[10],需对芯片进行配置。电路配置时,为降低噪声干扰,需在ADM2682E芯片电源引脚和地引脚之间并联一大一小两只旁路电容。为应对电路突发短路状况时引起的故障,一方面,由芯片手册可知,芯片的输入端具备故障保护功能,电路短路时接收器将输出高电平;另一方面,在电路设计时,分别在两芯片输入端接1 kΩ的上、下拉电阻,可确保差分信号电压始终高于芯片门限电压,保证了芯片始终工作在稳态。在两芯片正负输出端各接5.1 Ω电阻,防止了芯片发生短路。由于信号会发生反射,故选用阻值与传输电缆阻抗接近的120 Ω电阻,并将其跨接在各终端的正负引脚,可靠性得到提升。

3 软件可靠性设计

为保证通信稳定,硬件电路中加入可靠性设计的同时,对软件进行设计优化。在指令传输过程中加入校验字和三判二机制,提高指令可靠性;在数据传输过程中加入8B/10B 编码,降低误码率。

3.1 指令收发可靠性设计

存储器综合测控台向数据采编存储装置发送命令,采编存储装置向存储器综合测控台反馈状态,传输码率可达327.68 kbit/s。为防止因传输过程中的偶发性因素导致的指令错误,通常指令传输时有两种可靠性设计:一种采用三判二机制,测控台连续发送三次相同指令,当数据存储器检测到两次正确命令后,才会执行该命令;而另一种是在指令后添加校验字,其校验字由指令内容按位异或的方式求得[11]。指令传输在设计时,采用了三判二机制和校验字相结合的方法,保证了指令传输的可靠性。测控台下发一条指令时,将附带校验字的该指令连续发送三次,每次间隔1 ms,当数据存储器准确接收到其中两条指令后,将按照指令要求进行下一步操作[12]。指令内容如表1 所示。

3.2 数据传输可靠性设计(8B/10B)

当高速串行传输数据时,会有链路超时的情况出现[13]。由于连续高电平对高通滤波器的电容器充电时,可能会发生误码,从而将信号输入错误地降低为低电平。为了避免该类型的位错误,同时为避免电容寄生效应与电压位阶的存在对数据传输的干扰,在线路数据传输时,在牺牲少量带宽的情况下,加入了8B/10B 编码[14]。与4B/5B 编码的直流不平衡最大可达10%相比,8B/10B 编码更易达到DC 平衡,故采用8B/10B 编码,使得发送的“0”、“1”数量保持基本一致,提高了数据传输稳定性,降低了误码率。8B/10B 编码模块化的思路如下:

1)判断代码类型是数据代码还是特殊命令代码;

2)如果是特殊命令代码,则根据极性偏差的正负进行取值;

3)如果是数据字符,则将8 bit 拆分为高三位和低五位,并分别按其十进制数值记为x与y,故得到D.X.Y,再对照8B/10B 编码表进行编码[15]。由于8B/10B 编码表是从10 位共1 024 种排列组合中挑选256种0、1 个数差值较小的组合,故保证了DC 平衡。

4)编码时,5B/6B 编码在前,3B/4B 编码在后[16],在并串转换后将进行串行传输,其中,由5B/6B 的高位先进行发送。

4 试验验证与分析

通过上位机反复读取大量数据,并测试误码率,其数据结构如图7 所示。其中“C1 AA”为包头,其后的“B9 C3”至“B9 C9”为帧计数,每包共1 019 个字节有效数据,在测试时以“DD”进行代替。最后一位为校验位,用于校验接收数据的正确性。

为了验证设计的可靠性,将存储器综合测控台、数据采编存储设备、上位机组成闭环测试系统。采编设备通过一根长90 m 电缆向存储器综合测控台发送LVDS 数据,上位机对不同速率接收到的数据进行可靠性验证。通过多次测试,数据传输结果如表2 所示。

表2 测试结果

分析表2 中的数据可知,在不加8B/10B 编码的情况下,LVDS 数据可以无误码在传输速度为240 Mbit/s,传输距离为90 m 的情况下发送。随着传输速率的增加,数据开始频繁失锁。在加有8B/10B编码后,传输速度有所下降,但传输稳定性得到提升,在320 Mbit/s 的速度下,90 m 电缆可保持零误码传输。

5 结论

文中通过RS422 与LVDS 相结合,进行了通信链路的设计。在满足设计需求的前提下,针对LVDS 高速数据传输可靠性低的问题,硬件上提出预加重设计,增加缓冲器和均衡器;采用隔离芯片,在增加可靠性的同时,效率更高,功耗更小,降低了开发成本。软件上,对LVDS 数据传输采用8B/10B 编码,有效降低误码率。对RS422 指令传输采用三判二机制和校验字双结合,增强了检错能力。经验证,数据在320 Mbit/s 的速率下可靠传输,传输距离可达90 m。