集成电路成品测试的常见问题分析

倪宋斌,马美铭

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

1 引言

在集成电路的开发与生产中,检验测试环节是必不可少的,现阶段确保量产芯片质量和性能的主要方法就是测试。芯片在生产中的任意环节(例如流片、封装等)都会产生一定比例的缺陷,为了确保每颗电路在交付给客户前都能符合要求,集成电路测试行业应运而生,通过测试发现并剔除有缺陷的电路,从而保证电路的质量和可靠性。一般通过测试电路的直流参数(电流、电压等)以及各模块的功能来判断电路的整体性能是否符合标准。通过测试结果可以直观地获得电路的结构、功能以及电气特性的相关指标反馈。集成电路的芯片特征尺寸不断缩小,其集成度与复杂度也却来越高,使得集成电路测试的重要性不断上升。根据电路的生产过程,集成电路测试环节会覆盖每一道工序[1],例如晶圆测试、成品测试和可靠性测试等,并在每一步提高测试参数的全面性。成品测试是筛选质量良好芯片的最后一步,它对芯片测试规范中提到的电性能进行了最全面的检测。本文分析了不同类型的测试板、测试插座对芯片测试参数的影响,提出了在功能测试中进行时序调整的方法,降低了量产芯片的测试异常发生率,提高了芯片产能。

2 测试设备

2.1 自动测试系统

成品测试需要使用测试系统、测试板卡以及测试插座。采用泰瑞达公司的数字集成电路测试系统J750EX 机台进行测试。该系统具有丰富的数字通道资源,其时钟频率最高可达到200 MHz,并且拥有良好的驱动和接受能力。系统可根据需求分别拥有256 个、512 个或者1 024 个通道,每块机台电路板上集成了64 个通道。每个通道都可以独立地控制其引脚的驱动时序和电平,每个通道的向量存储深度最高为16 MB,每个通道都配备了独立的参数测量单元和高压驱动通道[2],支持32 个工位并行测试。该测试系统采用微软公司的Windows NT 平台,并利用Excel 软件和VisualBasic 语言开发了与之配套的测试软件包[3]。

2.2 测试板及DUT 板

测试板与DUT 板是测试硬件的主体部分。测试板是为了引出机台内部资源通道板的通道而设计的测试母板,其通用性高且不易损坏。子母板形式的DUT 测试板外观如图1(a)所示,针对不同的芯片,在测试母板基础上设计单独适配的DUT 子板,以确保测试结果的准确性和可靠性。用于多芯片并行测试的测试板中通常存在射频信号和模拟差分信号,这些信号在板级之间的互扰影响很大[4]。如果对测试频率的要求较高,或者外围器件较复杂,通常会在测试母板的基础上直接设计并集成以形成一个专用的测试板,专用测试板外观如图1(b)所示。专用测试板对测试的稳定性和准确性有较大提高,具体表现为工作电流变小、电压测试结果更接近真实值以及由于线长变短带来的传输延时降低。

图1 不同类型的测试板外观

3 成品测试流程

集成电路成品测试流程如图2 所示,基本可以分为开短路测试(接触测试)、电路功能测试以及电参数测试。

图2 集成电路成品测试流程

3.1 开短路测试

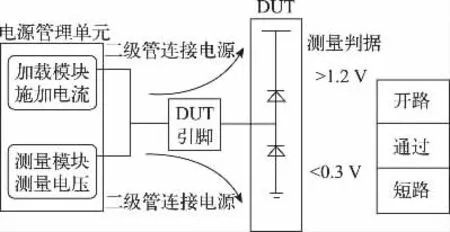

在芯片设计阶段,会在引脚处添加二极管。开短路测试则是利用开尔文测试原理,在电路的被测管脚处施加电流,之后测试该管脚的电压,并根据测出的电压值判断电路的管脚是否存在短路或者开路现象。开短路测试方法如图3 所示。

图3 开短路测试方法

使用测试机连接电路引脚,之后对电路引脚注入或者拉取100 μA 以上的电流,检测其引脚的电压值,以判断引脚是否存在开路或短路现象。一般情况下,若测得的电压绝对值大于1.2 V,则认为该引脚开路;若测得的电压绝对值小于0.3 V,则认为该引脚短路。

3.2 测试插座的影响

测试插座是一种用于对电路的电性能及电气连接进行测试,以检查生产制造缺陷及电路不良的必备试验装置。在成品测试中普遍使用的测试插座为老化测试插座和弹簧针测试插座,如图4 所示。

图4 老化测试插座及弹簧针测试插座

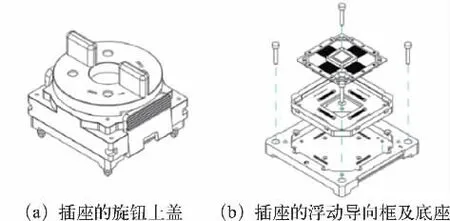

在生产中大量使用的为弹簧针测试插座,其结构如图5 所示,主要由插座主体、弹簧信号针、浮动导向框及旋钮上盖组成。

图5 弹簧针测试插座结构

弹簧针测试插座的耐电流能力比老化测试插座更强,其可以承受的电流为1~2 A[5]。弹簧针测试插座的弹针连接器在被压缩时其接触点不移动,而弹片连接器在被压缩时则会发生移动,稳定的接触点可以确保连接的稳定性,从而让产品获得稳定的电气性能[6]。相较于采用老化测试插座进行测试,采用弹簧针测试插座进行测试的最大区别是需要在低温环境下进行。老化测试插座由于受到其材质的影响,在低温环境下会产生水汽,影响插座和电路的接触,过多的水汽会造成电路管脚短路,损伤电路性能。另外,老化测试插座缺少气孔,在进行热流罩测试时,电路的实际温度达不到测试要求的温度。例如,测试要求达到125 ℃,使用无气孔的老化测试插座进行测试,电路的实测温度仅为95~105 ℃,远未达到测试要求。

老化测试插座的底座材料中还应添加耐磨损添加剂,以提高插座的耐摩擦及耐磨损性能。但是耐磨损添加剂通常为金属化合物,在使用插座过程中,金属化合物受到温度、压力及磨损的影响,容易形成凸起的颗粒物,造成电路外观损伤。为避免此类损伤,弹簧针测试插座的底座与浮动导向框腔体接触的部分应尽量选用耐磨损、杂质少且不会因吸潮变形的材料[7]。

3.3 DUT 板及测试板的影响

DUT 板和测试板是集成电路测试中非常重要的两个测试部件,其设计和制作质量会直接影响到整个测试过程,尤其对开短路测试有重要影响。DUT 板和测试板的设计或制作不规范,会导致线路不通畅或测试结果不准确,从而出现误判和漏判的情况。以2.2 节中提到的子母板形式的DUT 测试板为例,由于测试母板的使用时间过长,导致测试母板与测试机之间出现连接不通的现象,这会引起开短路测试的误判。如果子板出现线路不通或设计不规范的情况,也会影响开短路测试结果,进而降低测试效率。在母板上设计并集成以形成一个专用的测试板,会大大减少接触测试发生异常的情况,对异常问题的定位和解决效率也有显著的提升。综上所述,在测试过程中需要注意DUT 板和测试板是否可以正常工作,以确保测试结果的准确性。

4 功能测试中的时序偏移

芯片测试的主要目的是验证功能。功能测试是数字集成电路测试的核心,通过模拟芯片的实际工作状态,输入一系列有序或随机组合的测试图形,以电路规定的时序驱动被测器件,检测输出信号是否与预期图形数据相符,以此判别电路功能是否正常[8]。在数字集成电路测试系统的配套测试软件中,常见的测试方法是利用测试向量来判断芯片功能是否满足最初的设计要求。测试向量一般是由I/O 引脚的逻辑值(通常为0 或1)组成,为芯片的I/O 引脚提供输入信息。从输出引脚采样点得到输出逻辑值,再用得到的输出逻辑值与测试向量的原始逻辑值进行比较。若在采样点得到的输出逻辑值与预期的输出逻辑值一致,则判定电路正常;若结果与预期的输出逻辑值不一致,则判定电路存在功能失效。使用软件中的时间参数设置功能来定义输出引脚的采样过程,为了避免在信号状态翻转处出现误采,通常将采样点设置在一个周期的95%处,以确保信号有足够的稳定时间,从而避免误判。在理想状态与非理想状态下输出引脚采样点的情况如图6 所示。从图6 可以看出,理想状态下输出引脚的逻辑值为H,非理想状态下输出引脚的逻辑值为L,T 为一个采样周期。在实际测试过程中,由于芯片个体差异,部分输出引脚对输入引脚的变化响应过快,这种情况可能导致在原先设置的采样点采集到的输出逻辑值为下一个周期的输出逻辑值。为了避免这种情况,可以将采样点设置在一个周期的90%处,以确保可以在采样点采集到准确的当前周期的输出逻辑值。

图6 在理想状态与非理想状态下输出引脚采样点的情况

5 结论

本文分析了测试插座、测试板以及温度差异等因素对集成电路成品开短路测试准确性的影响,并提出了避免在测试中出现假性失效现象的优化方案。同时讨论了测试程序设置不合理和温度差异对功能测试的影响以及相应的解决方法。通过规避集成电路成品测试中的问题,可以直接提高测试效率,从而提高经济效益。本文的研究结果还可以为之后量产电路测试方案的制定提供有益的指导。