基于DDS的低相噪捷变频频率源的设计与实现

杨光华,管 飞,尹红波,黄家升

(中国船舶集团有限公司第七二三研究所,江苏 扬州 225101)

0 引 言

频率源是微波系统中的重要功能单元,它是一种利用一个或多个高稳定度和高准确度的标准信号,采用各种技术产生大量离散频率信号的设备,作用是给微波扫频信号提供一定分辨率的频率参考信号,并对微波信号输出频率进行逐点锁定,以得到高准确度和稳定度的扫频输出信号。高性能频率源[1]是通信、雷达、精密测量仪器等电子系统的核心组成部分,是决定电子系统性能的关键设备。随着现代无线通信事业的发展,移动通信、雷达、制导武器和电子对抗等系统对频率源提出了越来越高的要求,宽带、低相位噪声、低杂散、细步进、快速频率变换的频率源成为其发展的主要趋势。

DDS输出基带信号杂散较大,带外杂散经带通滤波器后可直接滤除;带内杂散,传统设计方案中因为体积问题只依靠DDS本身性能抑制,而其自身对带内抑制较差(一般约60 dBc),导致最终组件输出杂散不理想。本文在DDS后接小型化开关滤波器组来分段滤除DDS输出的带内杂散,实现杂散抑制指标提升约10 dBc的同时也实现了小型化。

1 基本原理

1.1 频率源设计指标

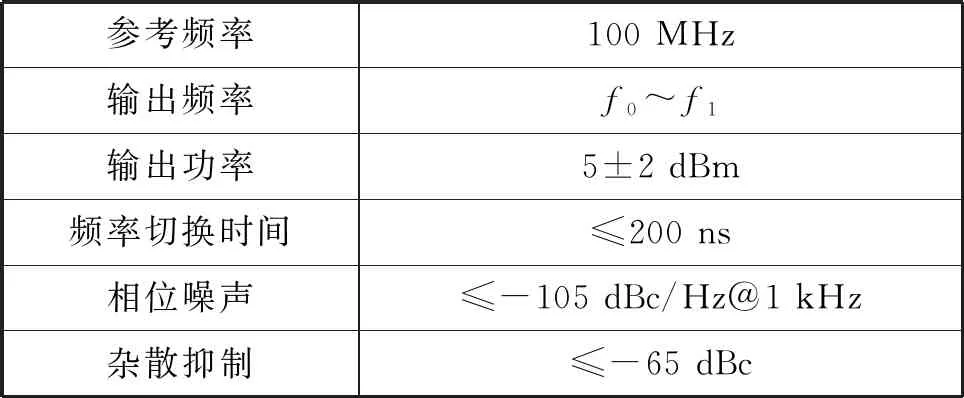

本文频率源的设计指标如表1所示。

表1 性能指标

1.2 原理分析

目前频率合成的基本方式按照工作原理可以分为3种[2]:直接频率合成法、间接频率合成法和直接数字合成法(DDS)。

直接频率合成法是最早的频率合成方法,由一个高稳定度的参考源,通过“加、减、乘、除”四则运算产生多个所需的频率:加减法通过混频器实现,乘法通过倍频器实现,除法通过分频器实现。该方法频率切换时间快,但是体积大、功耗大、重量大、硬件多、可靠性较差。目前只有少数场合仍在使用。

间接频率合成法又称为锁相环合成法(PLL),通过改变反馈支路中分频器的分频比值,可以实现由一个单一参考频率获得大量频率信号输出的方法。其具有低杂散、低相噪、输出带宽较宽的优点;但其频率转换速度慢,频率分辨率低。

DDS是继直接频率合成和锁相环合成法之后,随着数字集成电路和微电子技术的发展而迅速发展起来并广泛应用的第3代频率合成技术[3]。它是从相位的角度出发,利用先进的数字处理技术把一系列数字信号通过数/模(D/A)转换器转换为模拟信号的方法。它具有以下优点:频率分辨力高,切换速度快,可以合成任意形状的周期信号,数字调制能力强,体积小,集成度高,控制方便,易与计算机相连。其缺点是输出信号频率较低、带宽窄、杂散较大。

基于此,提出DDS+上变频的低杂散捷变频方案。DDS主要由相位累加器、数模转换器、滤波器等组成。根据DDS的相位累加原理[4],在一个系统时钟周期内,不同的相位累加值可以得到不同的频率信号输出。假设系统时钟频率为fc,输出频率为fo,则:

(1)

式中:K为频率控制字;N为相位累加器的字长。

由式(1)可知,在时钟频率确定的情况下,相位累加器的位数越高,则DDS的输出分辨力越高;改变频率控制字,即可得到所需的频率;由于受奈奎斯特采样定理的限制,DDS输出频率只能达到参考时钟的40%。本文选用振芯科技的GM4912C芯片,其参考时钟最高可达5 GHz,直接模拟输出可达2 GHz。实测发现其输出频率越高,杂散越大,最终选择DDS输出频率为f2~f3。

DDS直接输出的基频频率较低,采用混频的方式进行频率搬移得到较高输出频率。多个本振频点由梳状谱发生器通过倍频产生,倍频[5]过程中会恶化相位噪声。设倍频器输入信号和输出信号的相位噪声分别为L(fo)和L(Nfo),根据倍频器相位噪声的理论分析可得,其倍频后信号相位噪声恶化理论值为:

(2)

式中:N为输出频率与输入频率的比值。

由式(2)可知,输出信号的相位噪声按照20lgN程度恶化。本文中的本振频点由梳妆谱发生器产生,经式(2)计算满足最终相噪指标要求。

DDS输出的幅度可由下式计算:

(3)

式中:Am表示输出幅度;A表示幅度字;Amax表示输出波形最大幅度值,通过改变A值来控制输出波形的幅度;N表示D/A寄存器的位数。

本文选用的GM4912CN为14,其最大输出为0 dBm左右,综合考虑频率源的增益等,设置DDS最大输出,减少后续增益压力。

1.3 频率源整体设计方案

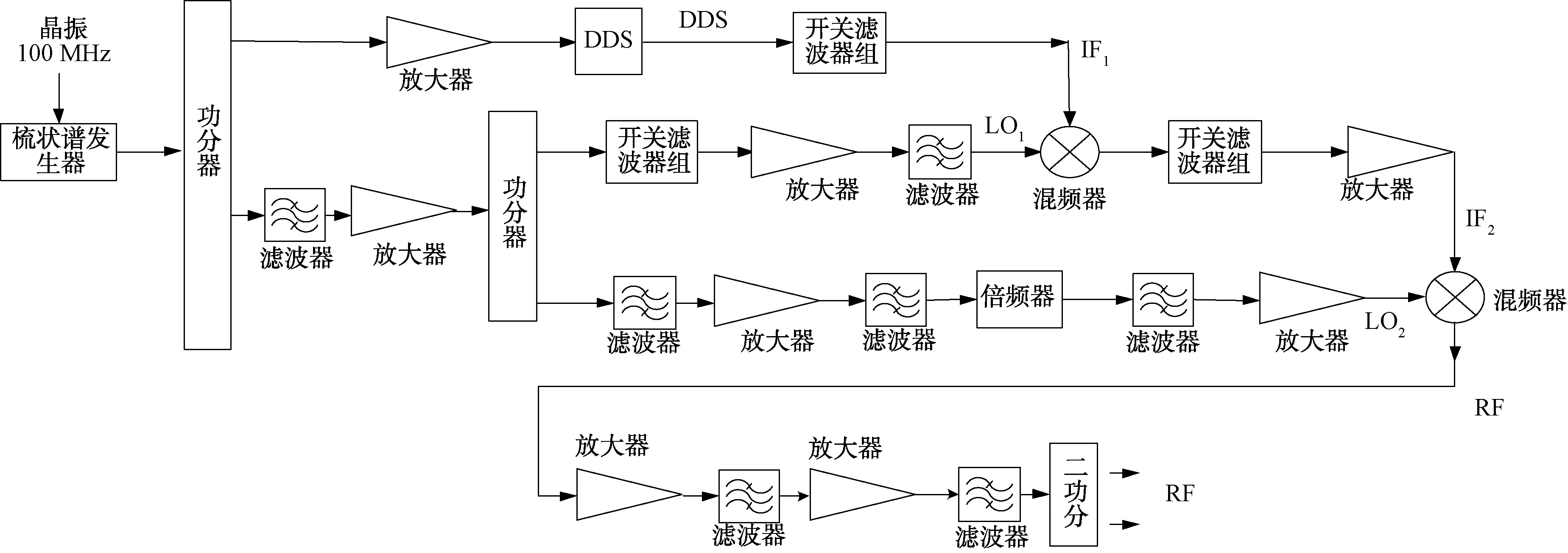

本文采用DDS与直接频率合成(上变频)相结合的方式,把DDS输出的具有一定带宽的低频信号与梳状谱发生器产生的多个点频混频,上搬到X波段,然后再滤波放大输出。具体方案框图见图1。

图1 系统原理框图

通过梳状谱发生器对100 MHz输入信号进行倍频,产生多个高次谐波,然后功分2路。一路经放大滤波后作为DDS部分参考信号,产生低频的基带捷变信号。DDS对参考信号的相位噪声要求较高,本文采用恒温晶振经梳状谱发生器产生的参考信号可以满足其相噪要求。DDS在不同的参考信号下产生的杂散不同,本文为得到高性能指标,考虑本方案所能提供的参考信号,经计算结合多次试验最终选定该参考信号,使DDS输出的杂散满足指标要求。

另一路经滤波放大后再功分为2路,第1路经开关滤波器组,滤出多个点频信号作为一次变频的本振信号LO1,和DDS输出基带信号(IF1)上变频产生IF2,IF2再经开关滤波器组滤除杂散后放大输出给第2级混频器。这2个开关滤波器组除要求高抑制外还要求快速切换,故其上滤波电容不可使用大电容以免影响开关时间;第2路信号经过4倍频产生高频的本振信号LO2,和IF2再变频产生射频(RF)信号,该部分需要注意基波、2次、3次及高次谐波问题,这些不需要的谐波极有可能在后续电路中交调产生落在带内的杂散信号,故这部分电路一定要滤除基波、2次、3次及高次谐波。

二混后的第1级放大器选取需要注意。经计算,二混后落在带内的杂散都为高阶杂散,混频器本身对其抑制就很高,此时考虑改善输出信号底噪的问题,要选用高P-1、低增益的放大器。因为混频后未滤波而先进入放大器,对放大器的线性指标要求较高,否则会产生交调。最后经过放大、滤波、功分,实现2路输出。

1.3.1 低相位噪声的实现

相位噪声是频率源的关键指标,目前实现低相噪要注意两点:(1)首先保证参考源相噪要低;(2)保证后续放大、倍频等链路中,相噪不再恶化或者恶化量小(倍频理论恶化除外)。对于第1点,选择相噪较好的恒温晶振即可,本文主要实现第2点。

后续电路对相位噪声的恶化主要体现在电源噪声引入的相噪恶化。直流电源由交流电源经稳压整流形成,不可避免地含有交流成份,称之为电源纹波。电源纹波会影响晶振及梳状谱的相噪,该噪声属于近端干扰,将直接附加在输出信号的噪声基底上。

这里采用电源噪声处理技术来实现较高的相噪输出。首先通过仿真计算,在电源入口处采用LC低通滤波来滤除低频噪声,使用分段滤波处理技术来滤除宽带范围内的高频噪声。其次,DDS部分既有数字电路还有模拟电路,需要模拟地和数字地,故数字电路和模拟电路分区布局并且在印制电路板(PCB)板上留出大面积接地面。最后对梳状谱及DDS供电采用具有较好电源抑制比(PSRR)的低压差线性稳压器(LDO)供电。

另外,为得到较低的相噪,低频附近的放大器,即梳状谱后的放大器采用低相位噪声放大器。

本文采用电源噪声处理技术及低相位噪声放大器后,最终测得DDS输出IF1信号相噪优于-125 dBc/Hz@1 kHz。通过原理框图可看出,最终输出信号的相噪决定于本振信号的相噪。根据公式(2)计算并考虑到链路中相噪恶化,最终信号相噪理论值为-115 dBc/Hz@1 kHz。

1.3.2 低杂散的实现

该频率源杂散主要来源于DDS电路、梳状谱产生的多种本振信号及高次谐波、混频产生的杂散。

DDS直接输出的基带信号杂散较大,包含多次谐波及带内杂散。带外杂散使用低通或带通滤波器可滤除;带内杂散,传统方案中只能通过计算结合试验选定不同的参考信号依靠DDS本身抑制来实现,如本文DDS输出的f2~f3带内杂散,经计算选定参考后只能靠GM4912C自身的抑制。此时DDS芯片自身对带内杂散抑制只有60 dBc左右,抑制较差。若采用普通的介质滤波器做开关滤波器组来分段抑制带内杂散,抑制可以达到设计要求但体积非常大,不符合小型化要求。本文从小型化的角度出发,选用低温共烧陶瓷(LTCC)形式的滤波器形成开关滤波器组来滤除基带信号的带内杂散。

经实际测试发现,GM4912C在输出频段f2~f3时,除谐波分量外,最大杂散约60 dBc,其它杂散在70 dBc以下。经分析,该最大杂散点可通过分段滤除。故本文把DDS输出分为2段,在其后接2路开关滤波器组,滤波器选用LTCC结构的带通形式,在满足小型化的同时抑制了DDS带内杂散。最终实测其输出杂散在68 dBc及以上。

梳状谱产生的本振杂散抑制主要取决于滤波器的带外抑制程度,本设计中选用的LC和腔体点频滤波器对于带外相邻100 MHz频点和低频段的抑制度达到80 dBc,高频端还选用微波单片集成电路(MMIC)低通滤波器和陶瓷带通滤波器进行滤除,理论杂散抑制能达到80 dBc。

2次变频的杂散计算:低阶杂散,比如(2,1)(2,0)(3,0)等远离通带;发现落在带内的杂散都为高阶杂散,比如(5,0)(4,0),混频器本身对其抑制就很高,满足设计要求,无需再做考虑。而镜频和本振信号,其频率远高于中频信号,可以通过混频后的中频滤波器进行滤除,中频滤波器的带外抑制度在80 dBc以上。

综合计算,频率源的杂散取决于DDS部分的杂散,最后输出应在68 dBc以上。

1.3.3 捷变频的实现

跳频时间组成主要有:DDS跳频时间、开关滤波器组切换时间、通信时间等。DDS跳频时间典型值70 ns,开关滤波器组切换时间在100 ns以内,这2种流程处于并行,总时间100 ns;通信时间及驱动的时间也在100 ns以内,总跳频时间可以控制在200 ns以内,满足要求。

2 测试结果

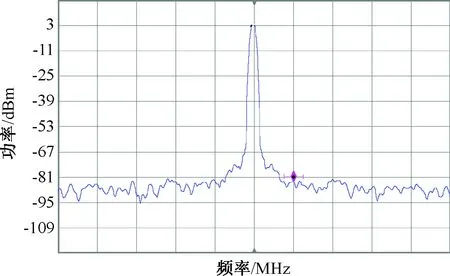

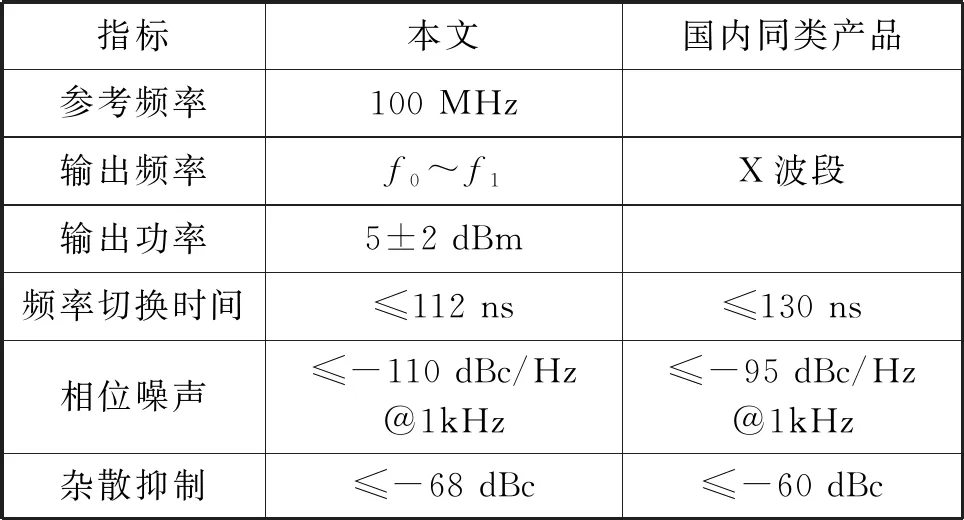

通过以上的理论与指标分析,对实物进行最终测试,在输出频带内,输出功率为5.8±1.1 dBm,满足设计要求,其它指标测试结果如图2~图4所示。与国内同类型产品指标对比如表2。

图2 相位噪声测试结果

表2 性能对比

图2为频率源最高输出频率时的信号相位噪声测试结果,可以看出在偏离主频1 kHz处相噪有-110 dBc/Hz@1kHz,与理论值接近,相差的5 dBc推测主要是由于电源纹波引入的相噪恶化。

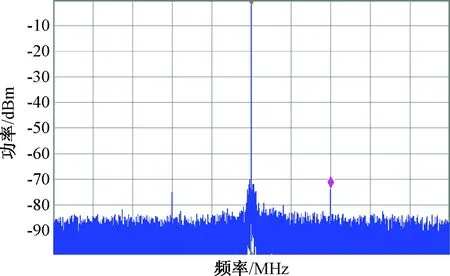

图3是模块杂散测试结果,为带宽内杂散最大值。由图3可以看出,杂散最大值为68.9 dBc。

图3 杂散测试结果

图4是模块频率切换时间测试结果,由图4可看出切换时间是112 ns。

3 结束语

本文介绍了一种低相噪捷变频频率源的设计,并进行了实物测试。测试结果表明,基于直接数字频率合成技术与混频频率合成技术相结合的方案,能够实现低相噪、高杂散抑制、快速频率切换等指标。在f0~f1内,相噪可以达到-110 dBc/Hz@1 kHz,杂散达到65 dBc以上,频率切换时间达到150 ns以下。该方案具有集成度高、小型化、控制方便等特点,为雷达、电子对抗等系统的频率综合器设计提供了一种低成本、高性能的选择。