高速跳频接收机方案设计

摘 要:随着干扰技术的快速发展,以及通信系统对抗截获和抗干扰能力需求不断提高,高速跳频接收机的需求不断增多。高速跳頻接收机对换频时间要求比较苛刻,这是高频跳频接收机设计面临的主要问题。文章从原理上对几种常用接收机架构进行了对比和分析,指出了制约接收机换频时间性能提升的主要原因,提出了基于射频直接采样架构的高速跳频接收机解决方案,对方案的基本架构和设计思路进行了阐述,并对方案的关键器件性能、达到的换频时间、方案设计要点和关键指标测试情况进行了说明,可为同类通信产品的设计提供参考。

关键词:跳频通信;高速跳频;换频时间;射频直接采样;频率合成;采样率

中图分类号:TN914.41 文献标识码:A 文章编号:2096-4706(2023)19-0046-05

Design of High Speed Frequency Hopping Receiver Scheme

NIU Shaowu

(Guangzhou Haige Communications Group Co., Ltd., Guangzhou 510663, China)

Abstract: With the rapid development of interference technology and the increasing demand of communication system for anti-interception and anti-interference capability, the demand of high-speed frequency hopping receiver is increasing. High-speed frequency hopping receivers require more rigorous frequency conversion time, which is the main problem in the design of high-frequency frequency hopping receivers. This paper makes a comparison and analysis of several common receiver architectures in principle, points out the main reasons that restrict the improvement of frequency conversion time performance of the receiver, puts forward a solution for high-speed frequency hopping receiver based on RF direct sampling architecture. It describes the basic architecture and design ideas of the scheme, and explains the performance of key components of the scheme, the achieved frequency conversion time, the design essentials of the scheme and the testing situation of key indicators. It can provide reference for the design of similar type of communication products.

Keywords: frequency hopping communication; high-speed frequency hopping; frequency conversion time; direct RF sampling; frequency synthesis; sampling rate

0 引 言

跳频通信是通信常见的抗干扰通信方式。与定频通信相比,跳频通信双方的工作频率会根据设备内伪随机码发生器数值计算出的频率进行有规律的跳变。只要对方不清楚跳频通信工作频率的跳变规律,通信的内容很难被截获。跳频通信还具有抗干扰能力,即使大部分工作频率被干扰了,跳频通信还可以在未被干扰的工作频率上进行信息传输。跳频通信因其良好的抗截获和抗干扰能力,在战术通信中被广泛应用。

随着跳频通信方式的发展,跟踪干扰应运而生。跟踪干扰是通过对跳频信号进行侦察、检测,并在相应频点施加干扰信号来干扰跳频通信。为了提高抗干扰能力,跳频通信需要更高的跳频速度来应对快速的跟踪干扰。每秒几千跳的中高速跳频接收机相对比较容易实现,但对于跳频速率超过每秒一万次或更高跳速的高速跳频接收机,由于射频电子元器件的固有特性,实现相对比较困难。

本文分析了常用接收机架构的特点和高速跳频接收机的难点,提出了基于国产射频直接采样收发芯片的高速跳频接收机的实现方案,并对实现方案要点进行了阐述,同时还给出了实现方案的测试情况,可为高速跳频通信技术的发展提供技术支撑。

1 接收机换频时间分析

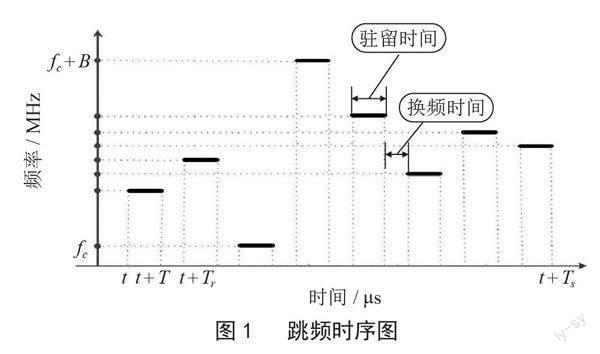

跳频通信时每个频点跳频通信时间包括驻留时间和换频时间两部分。一个跳频周期内换频时间越短,驻留时间越长,说明接收机用来传输有用信息的时间越长,信息传递效率越高。驻留时间和换频时间的跳频时序如图1所示。每秒一万跳的高速跳频接收机每个频点的驻留时间和换频时间的总时间为1/10 000 s,即100 μs。按照跳频通信通常要求,换频时间占一跳通信时间的十分之一左右,即每秒一万跳的高速跳频接收机换频时间要小于10 μs,通信驻留时间为90 μs。

2 接收机架构论证

2.1 接收机架构分析

超高速跳频接收机换频时间设计是难点。接收机架构有很多种,接收机结构一些固有特点已经决定了有些接收机结构很难满足超高速跳频的换频时间要求。

根据变频方式和中频频率的不同,接收机可分为超外差接收机、零中频接收机、镜像抑制接收机和射频直接采样接收机。以下分别对几种接收机结构做简单的介绍和分析。

2.1.1 超外差架构

超外差结构信号通路上一般包括选频滤波器、低噪放LNA(Low Noise Amplifier)、混频器、中频放大器和中频滤波器等电路。超外差结构是比较经典的接收机结构,应用范围广,架构成熟,性能高。超外差架构分为射频和中频两部分,甚至还可以有多个中频,方便进行增益分配,实现良好的系统动态范围。选频滤波器的合理设计,可有效滤除中频和像频干扰;中频频率的合理选择,可以实现优良的系统杂散性能;系统的带宽主要取决于中频滤波器带宽,带宽越窄,越可以发挥模数转换器(Analog to Digital Converter, ADC)的性能。超外差架构接收机原理图框图如图2所示。

超外差结构接收机电路相对复杂,主要体现在射频前端比较复杂,需要选频滤波器、放大器、混频器、本振、自动增益控制电路等组成,对于高速跳频的接收机来说,超外差结构的最主要缺点在于它的本振换频速度不够快,很难满足换频时间10 μs的高速跳频需求。

本振常用的频率合成有直接模拟频率合成DAS(Direct Analog Frequency Synthesis)、直接数字频率合成DDS(Direct Digital Frequency Synthesis)和锁相式频率合成技术PLL(Phase-Locked Loop)等。这几种频率合成技术中DAS和PLL技术,由于器件固有特性,很难达到换频时间10 μs以下的技术要求。有的方案会采用乒乓环的方案实现减小换频时间,但乒乓环电路存在电路复杂,以及负载牵引等一系列问题。DDS采用是数字处理技术,它的优点是变频速度快,相位噪声低,频率精度高;缺点是带宽较窄,输出的杂散分量较高,可用的带宽被限制在参考时钟频率的40%以下,很难在宽带内实现高速跳频。

2.1.2 零中频架构

零中频架构接收机信号通路上主要有选频滤波器、低噪放LNA、混频器、本振信号、低通滤波器和模数转换器等电路。零中频架构接收机的本振信号与射频信号频率相同,故中频频率为零赫兹。零中频结构接收机原理框图如图3所示。

零中频架构接收机是一种结构简单,成本和体积相对较低的接收机架构。近年来随着高集成射频收发芯片的快速发展,零中频接收机被广泛使用。零中频接收机固有的直流偏移问题、二阶失真问题和闪烁噪声问题均可以通过一定方式进行解决。但对于高速跳频接收机来说,目前市面上通用的收发芯片内部的本振信号换频时间在15 μs左右,很难满足换频时间10 μs以内的要求。

2.1.3 镜像抑制架构

镜像抑制架构接收机是为了解决超外差架构接收机存在的镜像频率干扰问题。镜像抑制架构接收机的原理是通过增加混频的复杂度从而超外差架构接收机的镜像干扰,从而减少超外差结构接收机对镜像滤波器的依赖。镜像抑制架构接收机原理图框图如图4所示。

鏡像抑制架构接收机可以很好地抑制像频干扰,具有很高的接收机像频抑制能力。但镜像抑制架构接收机和超外差架构接收机存在同样的问题,频率合成器换频时间很难达到10 μs以内。

2.1.4 射频直接采样架构

射频直接采样架构接收机原理框图如图5所示。它主要包括选频滤波器、高速ADC和数字下变频模块等。按照奈奎斯特采样定理,射频直接采样架构接收机要求ADC的采样频率要足够高,采样频率必须是被采样信号带宽的两倍以上,才能无损地还原基带信号,否则会发生信号混叠失真。ADC前边带通滤波器的带宽必须根据ADC的采样时钟频率决定。ADC采样后的数据通过数字下变频的方式实现基带信号的还原。数字下变频部分使用数控振荡器NCO(Numerically Controlled Oscillator)的作用是产生正交的数字本振信号。数字本振信号和ADC采样的数字有用信号进行混频。混频换频后的信号经过数字低通滤波器后,滤除基带以外的混频产物,经数字低通滤波器滤波后产生正交I路和Q路两路信号,并被送到解调器进行相应解调处理。

射频直接采样架构接收机结构是最符合软件无线电结构的接收机,它结构最为简洁,软件化程度更高、更灵活,最接近理想的软件无线电设备。射频直接采样架构接收机把射频电路部分的器件数量减少到最少。有用射频接收信号经天线进入接收通路后,仅需要经过简单的滤波和放大后就被送给ADC进行采样,根本无须进行模拟混频,不存在混频时产生的杂散和干扰信号。数字下变频器DDC(Digital Down Conversion)处理的信号为数字信号。在数字域实现下变频,技术比较成熟,比较容易实现。数字域下变频算法多种多样,成本低,速度快。射频直接采样缺点是结构对ADC转换器的性能要求高,对后续信号处理芯片的处理速度要求也较高。

2.2 接收机架构选择

通过针对上述接收机进行对比分析,超外差架构、零中频结构、镜像抑制架构的接收机由于换频时间受限,很难满足换频时间小于10 μs的高速跳频接收机的要求。各种接收机结构的优缺点如表1所示。

近年来随着高性能ADC和高性能处理器越来越成熟,射频直接采样架构接收机越来越多被广泛应用。射频直接采样接收机模拟部分无须混频电路,数字下变频器中的数控振荡器NCO为数字信号,数字域下变频内部实现简单,速度快,换频时间为纳秒级别,是高速跳频接收机比较理想的架构选择。

3 高速跳频接收机方案设计

射频直接采样架构高速跳频接收机方案原理框图如图6所示。该方案核心ADC器件选用杭州城芯科技的高集成芯片CX8142。

高速跳频接收机天线接收下来的射频信号,经过960~1 224 MHz带通滤波器滤除带外无用信号,经IQ解调器后,通过固定本振,将960~1 224 MHz变换为频率为DC~264 MHz两路IQ信号,IQ信号经滤波和可调增益放大器放大后送给ADC器件CX8142进行信号处理,通过CX8142实现高速跳频设计。

3.1 核心器件性能分析

CX8142是一款集成两路高速高精度模数转换器ADC、两路数模转换器DAC、低噪声频率综合器以及基于JESD204B子类1标准SerDes接口的中频、射频信号处理芯片,芯片功能框图如图7所示。单通道功耗小于0.5 W,相对于三颗分立器件搭建的硬件,其具备的高集成度、低功耗特性大大降低了系统的面积和功耗开销。CX8142中ADC为14-bit,最高采样率可达750 MS/s,在500 MS/s采样条件下,80 MHz

输入条件下SFDR设计达到-80 dBc,在200 MHz输入条件下SFDR为-75 dBc;DAC的采样率为14-bit的,最高采样率为3 GSPS,输出功率最高可达6 dBm,在80 MHz输入条件下SFDR为-80 dBc,在200 MHz输入条件下SFDR为75 dBc。ADC和DAC支持片内提供频率源和外供频率源两种模式,其中内置频率综合器时钟抖动为120 fs。高速串口最大速率为15 Gbit/s并具备均衡、摆幅调节等功能。

3.2 换频时间分析

CX8142芯片内集成的DDS对0~2π作16位量化,采用直接旋转cordic,高效实现不同相位点的三角函数值求解;该技术首先通过折叠技术将0~2π折叠限定在0~π/4范围内,接着采用查找表进行角度细化,然后根据数学量化分析得到细化后的较小角度量化补码,直接按每位二进制值进行2-i角度免缩放因子单向旋转。每次旋转方向比较确定,使迭代次数有效减少,过程处理时间大大缩短;从而降低电路面积,降低杂散。采用48 bits的相位控制字在每个时钟周期内和相位累加器内的相位进行累加,累加的结果高16 bits作为一个寻址地址,从对应的0~2π的量化結果中正弦余弦值,从而提高NCO的精度;采用小数补偿技术进一步提高了相位控制字的精度;信号混频时,采用三个乘法器实现了复数乘法,和传统的复数乘法相比节省了25%的硬件开销。

采用并行数据处理技术,配合DAC模块能够输出两倍系统钟采样率的信号(2 fs),同时提高混频器的混频频率;NCO模块可以在一个系统钟周期内实现连续两次的相位累加,从而输出连续的两个相位的正弦和余弦信号值和输入信号进行混频,提高输出信号的混频频率;采用延时更新技术,每次更改频率需要写六个地址寄存器,从reg0~reg5依次写入,只有最后一个寄存器(reg5)被写入数据时,频率控制字才会更新;从而实现了存在6个地址中的48 bits频率控制字进行瞬态切换,从而实现NCO的相位连续,换频时间快。NCO换频时间小于0.5 μs,跳频速率可达15万跳以上。

3.3 AD降采样设计

接收机工作频段为960~1 224 MHz,为了方便对信号进行处理,在AD采样之前需要先采用固定频率对信号频谱搬移至下DC~264 MHz。CX8142芯片最高采样率750 MS/s,为了优化性能,如果使用500 MS/s采样频率采样DC~264 MHz带宽的信号,采样率偏低,对基带FPGA基带处理速度要求很高。因此本方案在信道变频部分采用IQ正交解调器的方案,先将射频信号下变频为两路IQ信号,再进行ADC采样,这样采样带宽可降低一半,FPGA处理速度要求也对应降低,方案实现难度降低,可靠性也会得到保证。

3.4 关键指标测试情况

在射频直接高速跳频接收机方案中,接收机性能主要取决于CX8142芯片性能。CX8142的关键指标测试情况如下。

3.4.1 无杂散动态范围指标测试情况

在采样率为500 MHz,ADC满幅电压Vpp为1.8 V,输入典型工作频率为150.7 MHz,输入功率分别为-1 dBFS、-2 dBFS、-3 dBFS、-4 dBFS时,CX8142的无杂散动态范围(SFDR)如表2所示。

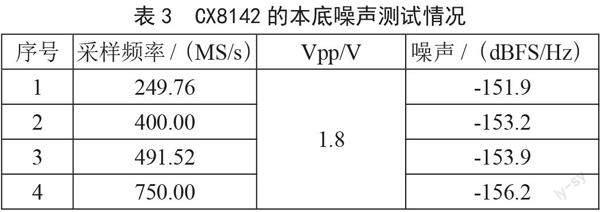

3.4.2 ADC的本底噪声测试情况

在ADC满幅电压Vpp为1.8 V,不同采样频率时,CX8142的本底噪声测试情况如表3所示。

除了良好的无杂散动态范围和本底噪声外,CX8142芯片内部数字混频器NCO可实现信号的上下变频,支持五种跳频模式,五种模式包括相位连续跳频、相位不连续跳频、相位连续快速同步跳频、相位不连续快速跳频和相位相干跳频。本方案采用相位连续跳频方式,频率控制字只有在最后一个相位控制字更新之后才会更新相位控制字,且相位控制字切换之后,NCO输出的相位连续,换频时间为0.5 μs以内,跳频速率可达15万跳,满足换频时间10 μs的高速跳频要求。

4 结 论

针对高速跳频接收机换频时间要求苛刻这一难题,本文分析了常用接收机架构的特点和高速跳频接收机的实现难点,提出了基于CX8142的射频直接采样高速跳频接收机的解决方案。文章不仅对方案采用的关键器件性能和方案设计要点进行了详细阐述,还对高速跳频接收机的关键指标测试情况进行了说明,可为同类通信产品的设计提供参考。

参考文献:

[1] 唐磊.超短波抗干扰通信系统射频前端设计 [D].西安:西安电子科技大学,2017.

[2] 崔晓冬.超宽带接收机的设计与实现 [D].成都:电子科技大学,2021.

[3] 王润生.高线性宽带射频系统设计 [D].南京:东南大学,2015.

[4] 郭昭杨.一种可重构的宽带射频前端设计 [J].通信技术,2018,51(1):245-251.

[5] 庞子鸿.基于射频收发机的通信系统的研究与设计 [J].电子测试,2019(11):98-99+55.

[6] 陈斌,黎绍峰,牛绍伍.宽频段大功率射频前端的设计问题 [J].电子科技,2017,30(9):156-158.

[7] 朱洪亮.短波软件无线电接收机硬件平台设计关键技术研究 [D].郑州:解放军信息工程大学,2006.

[8] 刘雨.多通道数字信道化接收机技术研究与实现 [D].哈尔滨:哈尔滨工程大学,2017.

[9] 刘国超.基于PLL低相噪快捷变频率源的研究与设计 [D].成都:电子科技大学,2021.

[10] 王涛.快速切换频率综合器的设计与实现 [D].成都:电子科技大学,2015.

[11] 王战永.基于DDS+PLL一种快速跳频频率合成电路的设计与实现 [J].移动通信,2014,38(24):57-61+66.

[12] 厉家骏.快跳频率合成器的设计与实现 [D].杭州:杭州电子科技大学,2016.

[13] 叶津宇.超宽带小型化捷变频频率合成器的研究 [D].南京:南京理工大学,2020.

[14] 李宁,范亚浩,贾建鹏,等.轻型高效可重构射频前端的研究 [C]//第三届航天电子战略研究论坛论文集(遥测遥控专刊).北京:中国航天科技集团公司第九研究院科学技术委员会,2017:89-92.

[15] 余江.无线通信中射频收发系统的研究与设计 [J].无线互联科技,2022,19(2):6-7.

作者简介:牛绍伍(1977—),男,汉族,安徽宿州人,高级工程师,本科,研究方向:无线通信系统。

收稿日期:2023-04-13