基于FPGA的激光测距硬件设计研究*

刘永华

(江西师范高等专科学校,江西 鹰潭 335000)

激光测距系统的任务是利用数据采集模块对硬件系统接收到的参考信号和回波信号进行数据采样,之后将采样数据送入信息处理单元解算目标距离值[1]。由于激光具有方向性强、单色性好、发散角度小等优点,对比其他测距技术和设备,激光测距仪具有测速效率高、测距远、精度强等特点,现已被广泛应用于航空、农业土地测量、矿山、港口等领域[2]。本文在对脉冲式激光测距进行深入研究的理论基础上,对激光测距系统进行了相关的硬件电路设计,为后续的相关研究提供了借鉴。

1 脉冲式激光测距原理

激光发射器会向被测对象发射特定频率的激光脉冲,同时,计时器启动,脉冲经空气介质进行传输,到达待测对象后,物体对激光的反射作用会使激光反射回激光接收器,计时器停止[3]。根据计时器所记录的时间差,利用公式计算距离大小,即:

式中,D为测量的距离大小,ΔT为激光发射与反射到达激光接收器的时间间隔,C为光速。特别注意:是以发射和返回脉冲波的上升沿作为时间基准ΔT,可计算出被测对象的距离[4]。

2 控制系统设计

激光测距系统的系统结构设计如图1所示,整个系统可分为四个部分。第一部分是激光发射单元,主要驱动二极管发射激光脉冲;第二部分是激光接收单元,高速AD采样,对接收的信号进行放大、整形、滤波,形成可供FPGA处理的数字信号,从而完成回波信号的探测;第三部分是存储器,主要用于存放程序和数据;第四部分是信息处理单元,主要是围绕FPGA芯片,完成数据的相关处理,将计算结果传递给上位机进行显示[5]。

3 基于FPGA的激光测距硬件平台搭建

3.1 FPGA设计

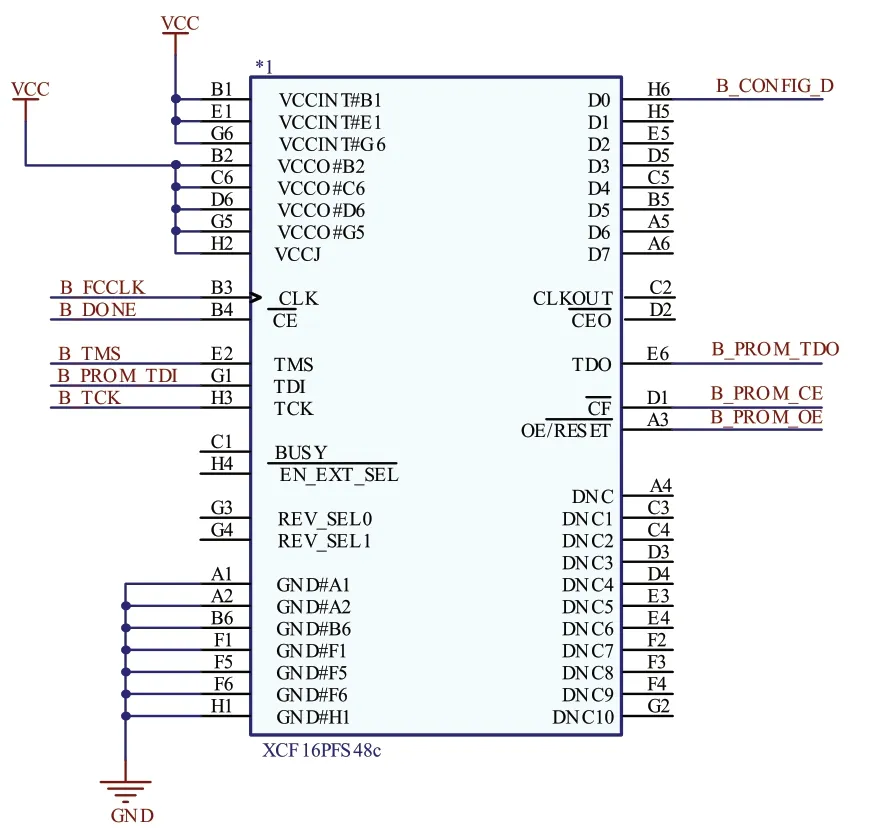

根据相关性能的要求,FPGA芯片主要选择XINLINX公司生产的Ⅴirtex-4XC4ⅤLX40-10FF668I,具有ASMBL架构、高逻辑密度、500 MHz的时钟频率,配置电路如图2所示。

图2 FPGA配置电路

3.2 激光发射单元设计

在空气介质传播过程中,由于漫反射的作用导致脉冲功率下降严重。为了满足远距离传输要求,需要提高发射功率。因此,在本次设计中选用303 MHz高重复频率掺Er光纤飞秒激光器[6]。

设计脉冲驱动电路时,采用EL7104芯片将电路的输出信号通过互连线与激光管相连,在互连线的两端分别接入0.1 μF的阻抗,保证激光管和互连线的匹配。其中,芯片2号的管脚输入电压信号[7],自动调整偏置电流,能够保证激光器发射光功率的稳定。驱动电路图如图3所示。

图3 驱动电路

3.3 激光接收单元设计

激光接收单元主要包括三大部分:一是光电探测器部分,主要选择光电二极管,保证能将回波信号转化为电信号,并根据光电探测器匹配激光器;二是匹配放大器部分,放大整形探测器输出的电信号经过放大、整形、滤波后能增强信号性能,便于后续处理;三是AD数据模块,能完成模数转换,在存储器中陆续存储已调制的离散数据。

本系统中,激光接收单元各部分的电路模块关系如图4所示[8]。其中,回波光信号通过光电探测器能够将光信号转换成电信号,由于部分电信号比较微弱,需要经过匹配放大器,完成信号的放大、整流、过滤,为AD高速采样做好准备。

图4 激光接收单元各部分电路模块关系

3.3.1 探测器部分

由于雪崩二激光具有响应速度快、倍增因子适中、噪声小、成本低等优点,所以光电探测器选用的是AD500-9型雪崩光电二极管以及C30724光电探测[9]。

3.3.2 匹配放大器部分

主放大电路主要是利用两个超高速电流反馈放大器AD8009进行级联[10],增益倍数由原先的10扩大为100,主放大电路如图5所示。由于反馈电路采用的是电流负反馈,反馈电阻和带宽存在反比关系,再考虑到AD8009所需的工作环境(例如175 mA以上的负载电流,440 MHz的信号带宽),综合判断反馈电阻为1 kΩ。

图5 主放大电路原理图

3.3.3 AD数据采样模块

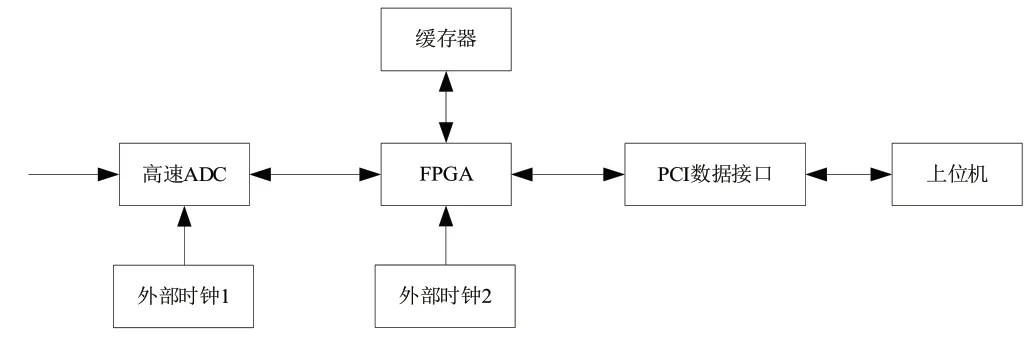

该系统模块主要通过高速ADC进行采样,并将模拟信号转换成数字信号,再由FPGA控制完成数据的采集和运算处理,通过PCI数据接口将数据结果传递给上位机进行显示。高速数据采集模块系统结构如图6所示。

图6 AD高速数据采集模块系统结构

其中,高速ADC模块采用的是ADC08D1000芯片,其采样速率能够达到1 GHz。外部时钟模块,由于外部时钟的精准性对ADC的精准采样影响较大,实际电路中也会产生时钟的抖动,时钟抖动的时间间隔需低于15 ps,因此,采用IDT公司的专用时钟芯片ICS8430-61,其具有高精度、低抖动的特点。FPGA控制模块对ADC08D1000进行配置时,首先会将配置命令控制字写进缓存器中,同时通过三线口对ADC的内部两条通道进行配置,完成对数据的运算处理。

3.4 FPGA与ADC接口设计

FPGA与ADC的接口设计电路图如图7所示。FPGA与ADC08D1000的输出端相连,将ADC08D1000得到的数据通过FPGA缓存到DDR3缓存器中,以便后续单元将数据取走。

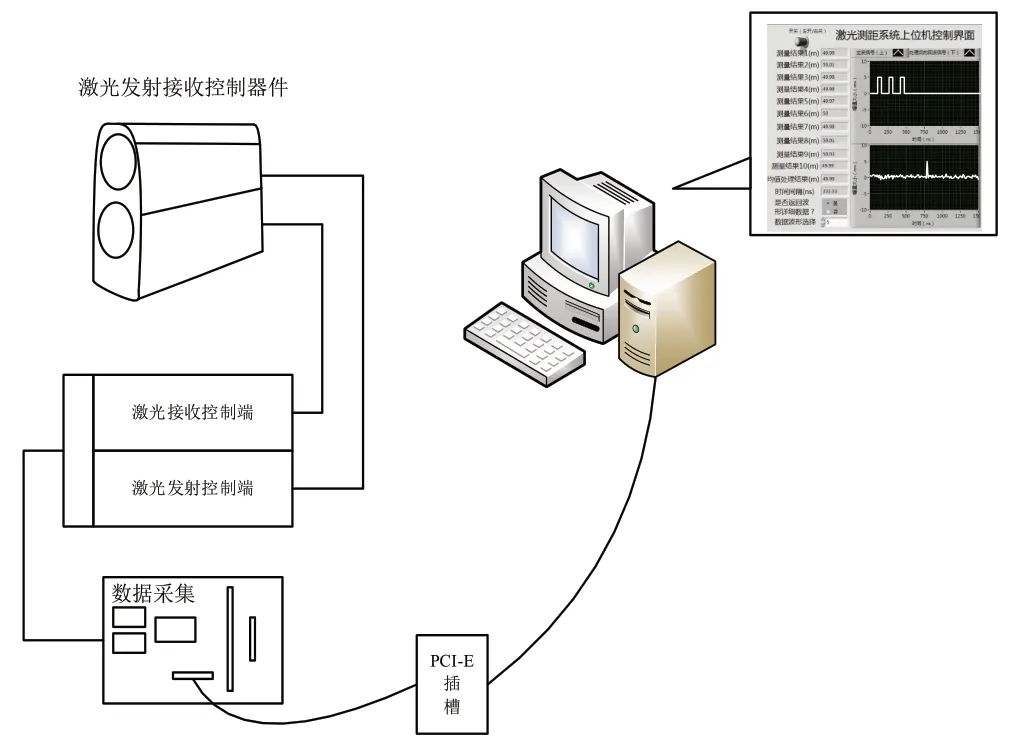

4 测试系统组成

测试系统如图8所示,主要由激光发射接收控制器件、数据采集模块、上位机组成。本次测试主要针对2 854.35 m的待测距离,其测量结果如图9所示。

图8 测试系统组成

图9 测量结果

5 结果与结论

经过十次测距,结果显示的最大和最小误差分别为17 cm和3 cm,误差均在±20 cm以内,符合预期。经过小波变换的奇异值检测算法求出其平均值,测距结果为2 854.38 m,和实际值相差3 cm。图9中的LabⅤIEW界面上显示的是第9次回波信号的幅值大小和时间值,测试结果为2 854.31 m。

通过对多脉冲式激光测距仪进行硬件设计,实现了测距仪的自动化测量和远距离测量,满足了测距技术在不同领域的要求,具有良好的研究和应用价值。