面向CMUT的多通道数据采集系统

邢晨茹 韩建宁 蔺红彦 郝国栋

摘 要:随着医学超声成像系统的不断发展,电容式微机械超声换能器(CMUT)的应用日益增多。为了满足电容式微机械超声换能器在超声采集过程中的实时性、高精度、多通道数据采集需求,基于Altera公司的EP4CE10F17C8型号芯片,结合16位8通道的同步采样芯片AD7606进行CMUT超声换能器信号的采集与传输,实现CMUT超声换能器的信号处理、采集、传输与显示一体化。

关键词:CMUT;EP4CE10F1717N;AD7606;多通道数据采集

中图分类号:TN919.5 文献标识码:A 文章编号:2096-4706(2023)14-0048-06

Multi-channel Data Acquisition System for CMUT

XING Chenru, HAN Jianning, LIN hongyan, HAO Guodong

(School of Information and Communication Engineering, North University of China, Taiyuan 030051, China)

Abstract: With the continuous development of medical ultrasound imaging systems, the application of capacitive micro mechanical ultrasound transducers (CMUT) is increasing. In order to meet the real-time, high-precision, and multi-channel data acquisition requirements of capacitive micro mechanical ultrasonic transducers in the ultrasonic acquisition process, based on Altera's EP4CE10F17C8 chip, combined with a 16 bit 8-channel synchronous sampling chip AD7606, the CMUT ultrasonic transducer signal is collected and transmitted, achieving the integration of signal processing, acquisition, transmission, and display of the CMUT ultrasonic transducer.

Keywords: CMUT; EP4CE10F1717N; AD7606; multi-channel data acquisition

0 引 言

CMUT超聲换能器比压电超声波换能器具有更宽的带宽和更高的灵敏度,并且其结构和加工工艺相对简单,易于实现阵列化,可以在医学成像应用中替代压电超声换能器[1,2]。我国关于CMUT技术的研究起步较晚,发展缓慢,基于CMUT超声换能器的超声成像系统需要逐步突破。针对CMUT超声换能器信号的检测以及系统的微型化需求,设计实时性强、精度高、功耗低的数据采集系统。

本文利用16位8通道的同步采样芯片AD7606,基于Altera公司的EP4CE10F17C8型FPGA控制整体系统逻辑,设计一套高适配性的采集系统,该系统可实现8路模拟输入信号的同步采样。因FPGA具有灵活、高速的特性而将其用作处理器,控制模数转换芯片[3],处理后的采样数据通过USB控制器从FIFO接口同步传输到PC机,可实时接收各通道采集的数据,以供超声成像系统对接收的数据进行成像分析。

1 硬件设计

1.1 总体框架

首先要确定面向CMUT超声换能器的多通道数据采集电路的整体设计方案。为了有效检测和接收CMUT超声换能器的信号,需要构建一个全新的多通道数据采集电路。该电路中包含一个低噪放大模块(用于降低系统的噪音),同时,FPGA可以根据不同的情况调节超声回波的增益,从而在下一级传输时获得更适合的信号幅度。同时接收的超声换能器信号为模拟信号[4],通过模数转换电路转换为数字信号,进而实现超声成像系统的数字化。模数转换电路的采样率由超声探头的频率决定。再将数据由数据的发送端传至数据的接收端,为CMUT超声成像系统提供数据支撑。

CMUT信号采集系统的硬件主板由FPGA核心板和扩展板构成,子板为ADC数据采集板。主板主要负责控制采集状态,接收ADC发送的模数转换数据,将采集到的数据信号在FPGA的控制下存入FIFO缓存器进行锁存,并通过USB接口发送给上位机;扩展板采用USB 2.0芯片,与PC机进行数据通信;AD7606芯片作为同步多路数据采集板的核心,负责将采集到的超声模拟信号进行模数转换,并将数字信号传输到FPGA。因此,整个系统是将通过检测电路的待采集信号传送至AD模块进行采样,经FPGA处理后数据通过USB接口发送给PC端,最后进行数据显示[5]。

系统硬件整体框图如图1所示。

1.2 采集模块设计

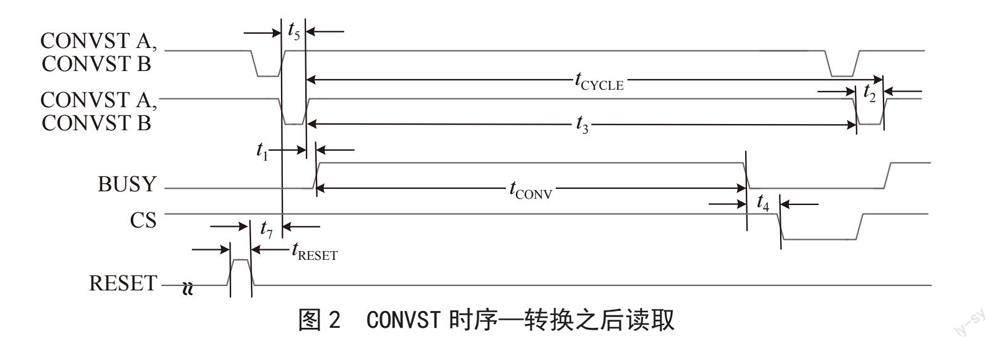

超声模拟信号采集电路是超声成像系统设计的基础,AD7606是ADI公司生产的高性能ADC,其采用iCMOS处理技术,可以实现8通道16位逐次逼近采样,每个通道高达200 kp/s。与传统的逐次逼近ADC不同,AD7606芯片具有内部集成的信号调理电路,还具有低噪声和高输入阻抗[6,7]。此外,该芯片使用单个+5 V电源供电。当8信道信号被同步采样时,CONVSTA和CONVSTB将被链接。在转换过程中,BUSY信号变为“1”,当它下降时,8通道信号被完全转换,数据被锁存到输出数据寄存器中[8]。在本设计中,芯片以串行接口模式工作,在CS信号拉低后,SCLK给出16×4 = 64个时钟,分别读取DOUTA输出和采集到的通道1~4上的数据以及DOUTB输出和采集到的通道5~8上的数据。在读取通道1时,FRSTDATA信号拉高。时序关系如图2所示。

1.3 输入输出接口

输入输出接口模块主要是负责FPGA控制系统与上位机的数据交互。硬件接口电路对整个数据采集系统的数据传输速率和运行速度发挥关键作用,所以,本设计采用Cypress公司的EZ-USBFX2芯片,通过USB 2.0接口将PC端发送的命令发送到FPGA,实现对数据采集系统的控制;同时也可以将AD7606采集到的数据发送至PC端。该芯片是一款嵌入式USB 2.0的微处理器,其内部包含智能串行接口引擎,能够自动终止发送和接收USB 2.0协议以及其他基本的USB功能[9]。芯片内部结构如图3所示。

其中,USB 2.0提供一个与计算机进行数据传输的接口。USB 2.0控制器有四个可寻址的FIFO缓冲区,每个缓冲区都连接到单个端点,通过设置地址信号的方式选择活动端点。FPGA与FX2芯片以FIFO方式通信,实现数据的高速传输。在该模式下CPU不再参与传输数据的过程,USB芯片在本过程中也只作为一个数据传输通道[10]。

2 软件设计

2.1 AD数据采集

当CMUT超声换能器的信号转换为电压信号后,需要由通过AD7606设计的信号采集电路进行采集与处理。AD测试程序以Verilog语言编写,QuartusⅡ编译器将编译无误的.sof文件通过JTAG下载到FPGA中。FRSTDATA是输出指令信号,当芯片选择信号CS处于高电平时,FRSTDATA将具有高阻抗,CS的下降沿将激活FRSTDATA信号。一旦可以读取第一信号,FRSTDATA信号将跳变为高电平。当RD信号处于下降沿时,读取第一信道信号的转换数据,FRSTDATA信号下降到低电平,具體的时序图如图4所示。FRSTDATA信号仅指示读取第一个信道信号。当CS信号保持在低电平时,RD脉冲信号可以读取转换后的8通道数据。最后,将采集到的数据写入FPGA的FIFO缓存器中[11]。

本设计采用状态机实现整个控制,共定义九个状态进行转换,通过输入caiji_flag标志信号开始每次的数据采集,当数据采集结束后,输出caiji_over结束信号。状态机转换流程如图5所示。

图5 AD数据采集状态图

2.2 数据存储

根据如图5所示的状态机转换过程,可以绘制出FPGA硬件程序的设计框图,如图6所示。在设计数据传输电路模块时,FPGA负责生成数据地址,并根据地址进行数据的读取和传输,而FIFO缓存器则应用于数据的存储。当需要向FIFO写入采集电路中的数据时,需将数据发送给FPGA芯片进行处理,同时在地址信号和控制信号的共同作用下将数据写入FIFO[12]。如果需要对FIFO中的数据进行读操作,FPGA控制将FIFO中对应地址的数据进行读取,并发送给FPGA芯片,FPGA芯片再将读取到的数据进行处理,便于USB 2.0实现对采样数据的实时获取,从而实现连续不断地采集数据信号,本设计中的数据存储及传输方式在减小资源占用的同时,还提高了系统的运行效率。

图6 FPGA程序设计框图

具体的执行过程是,AD7606芯片在FPGA的ADC接口控制电路的控制下,把超声模拟信号转换成数字信号,并将经由AD采集模块转换的数据存入FIFO[13],程序实现的RTL视图如图7所示。

2.3 数据传输

在完成超声成像系统中数据的存储后,需要对采集到的数据进行读取,以便后期方便快捷地处理数据,因此,在超声成像系统中,将超声信号数据传输至电脑端模块也是至关重要的。

FX2芯片在SlaveFIFO模式下工作时,FPGA控制模块按照SlaveFIFO模式下的时序与上位机进行高速数据通信。如图8所示为从设备FIFO接口与外部FPGA连接的系统框图。此时芯片内部4 KB的FIFO存储器将作为端点缓存,结合USB 2.0协议可配置4个端点,分别为EP2、EP4、EP6、EP8,通过改变USB固件的设置来修改其大小及缓冲倍数[14]。FPGA控制模块输出SlaveFIFO模式的传输时序,实现对端点的数据读、写操作,其中FX2芯片只作为FPGA与上位机数据交互的通道。

在传输过程中,FPGA的USB接口控制逻辑会询问FX2是否处于空闲状态,如果FX2处于空闲状态,FPGA的USB接口控制逻辑将通过FPGA内部FIFO缓存将指定通道的选择性数据发送到FX2内部FIFO。当FIFO的内部容量超过指定范围时,FX2会打包并将所有信息传输至PC端[15]。同时,固件程序将FX2芯片配置为SlaveFIFO模式,在向服务器发送数据的过程中,所有操作均不受FX2内部的CPU干预,因此数据传输速率得到保证。

传输模块的固件设计旨在完成对外部设备的初始化,处理驱动程序发送的各种命令,以及接收数据[16]。而驱动程序用于识别USB设备,在连接过程中可在主机PC侧与设备侧之间建立稳定的通信。

3 系统运行效果

在FPGA开发过程中,仿真验证调试时序是必不可少的步骤,利用QUARTUS软件,结合Modelsim仿真进行所开发采集系统的仿真实验。图9和图10分别表示AD7606时序逻辑结果与八通道数据输出结果。图中可以看出各个时序的周期变化以及通道1~8分别读取到的输入数据结果,时序图与代码设定一致。

编写tb仿真代码,测试数据是否存储到FPGA的FIFO中,图11显示了程序的模拟波形。由仿真波形图可以看出,wr_data和rd_data交替出现并一直循环下去,wr_flag数据有效标志信号与wr_data一一对应,rd_data在读请求信号时rd_req为高时输出。同时还可以看到empty和full在不同的位置均有拉高的脉冲。

采集卡时序逻辑设计涵盖USB接口控制模块和采集卡控制模块。先对USB接口控制模块的程序进行测试,此时的硬件状态为不加载采集板卡,仅控制板卡工作。在FPGA程序内部以累加器的形式替代采集数据的输入,采用cypress公司的ControlCenter软件,先选择端点EP2,发送启动采集指令使得采集卡开始工作,再从端点EP6内部读取累加器的数据,由图12可知,该USB 2.0接口控制模块的程序设计有效可行。

本测试选用外部信号发生器作为采集卡的模拟输入,信号发生器的CHA通道向采集卡的1、3、5、7四个通道输出频率为10 kHz的标准正弦波,峰值为8 V;CHB通道向采集卡的2、4、6、8四个通道输出频率为5 kHz的标准正弦波,峰值为4 V。图13显示了Labview软件中分别显示的8通道同步采集的界面波形图。

图12 USB接口控制模块的FPGA程序测试

为保证测试结果的准确性而进行了多次试验,最终实验结果是:8通道同步采集时,通道的最大采样精度为0.075%,能满足采样精度预期指标0.1%;同时也验证了用户应用软件的波形显示功能正常。

4 结 论

随着医学超声成像技术的快速发展,CMUT超声换能器凭借其宽频带、高灵敏度、高机电转换效率、微型化等优点业已成为压电超声换能器的有效替代。通过ADC将超声模拟输入信号转换为数字信号,随后数据将按顺序存储在FPGA的随机存取存储器(FIFO)中,再通过USB 2.0接口进行数据传输,实现与PC端的实时通信。在FPGA内部,利用VHDL语言设计了FIFO和状态机时序控制器,实现了与USB控制器的高速数据传输。此外,FPGA还用于转换和存储数据,可以较好地控制多通道同步采集系统。通过搭建测试平台,验证了多通道数据采集电路的电路性能,实验结果表明,面向CMUT的多通道高速实时数据采集系统可以实现既定功能。

参考文献:

[1] 孟亚楠.面向CMUT的多通道数据采集电路设计与分析 [D].太原:中北大学,2022.

[2] 张泽芳,任勇峰,何常德.基于CMUT的超声波信号检测及放大电路设计 [J].仪表技术与传感器,2020,445(2):37-40.

[3] 赵欢,李东伟,朱倩,等.FPGA仿真验证工具及前沿技术综述 [J].电子测试,2020,442(13):100-103.

[4] 赖泉青,卢露,许才彬,等.一种新型自发自收式双频超声换能器 [J].电子器件,2022,45(6):1517-1522.

[5] 白晓,尹俊,郑洋德,等.基于FPGA和LabVIEW的多通道数据采集系统设计 [J].核电子学与探测技术,2018,38(30):319-325.

[6] SHE X,XIONG J. Multi-channel electrical power data acquisition system based on AD7606 and NIOSII [C]//2011 International Conference on Electrical and Control Engineering.Yichang:IEEE,2011:1625-1627.

[7] WANG B J,MIAOL,DONG H Y,et al. Designofdynamicsynchronousmulti-channeldataacquisitionsystemforlungsoundbasedonFPGA [C]//2012 IEEE International Conference on Information and Automation. Shenyang:IEEE,2012:768-771.

[8] 田慧,管雪元,姜博文.基于Zynq的数据采集系统的研究与设计 [J].电子测量技术,2019,42(2):135-141.

[9] 郭艳.USB2.0接口多通道数据采集系统的设计 [D].西安:西安理工大学,2018.

[10] 朱莹.基于FPGA与USB2.0的数据采集系统的设计 [J].科技资讯,2015,13(22):17-19.

[11] 肖李欢,黄元峰,代文泽,等.基于AD7606的高精度数据采集系统的实现 [J].电脑知识与技术,2017,13(20):210-211+214.

[12] MROCZEK K. USB FIFO interface for FPGA based DAQ applications [C] //2015 IEEE 8th International Conference on Intelligent Data Acquisition and Advanced Computing Systems: Technology and Applications (IDAACS).Warsaw:IEEE,2015:666-671.

[13] 李朋勃,张洪平.基于FPGA和USB2.0的高速数据采集系统 [J].单片机与嵌入式系统应用,2009,35(10):109-112.

[14] 蒋思宇,王斌,余龙海,等.基于FPGA+AD7606的多通道数据采样系统设计与实现 [J].电子设计工程,2022,30(22):103-107.

[15] 庄洪毅.一种基于FX2与FPGA联用实现USB2.0通信协议的方法 [J].电子測量技术,2017,40(4):78-81.

[16] 陈柯勋,王振田,王飞.基于FPGA和USB2.0的数据采集系统 [J].工业技术创新,2017,4(5):12-15.

作者简介:邢晨茹(1999.12—),女,汉族,山西运城人,硕士研究生在读,研究方向:多通道采集。