基于共享存储技术的乱序TCP 分段重排电路设计

鲁铭洋,乔庐峰,张 栋

(陆军工程大学,江苏 南京 210001)

0 引 言

共享存储技术广泛应用于以太网交换机、路由器等网络设备中。共享存储管理电路本身是一个队列管理器,具有存储资源利用率高、结构简单、低时延等特性,能够将所有输入数据存储到公共存储区,通过高效调度管理,实现高速、高效运行[1]。

传输控制协议(Transmission Control Protocol,TCP)运行在网络层IP 协议上,TCP 分段数据在IP网络传输时,存在因网络拥塞和信道误码导致的分段数据丢失以及多路由转发引起的分段数据乱序问题[2]。TCP 协议提供可靠的面向连接的端到端服务,协议规定每个字节占用一个序列号,数据的发送和接收都要按序进行[3]。如果TCP 协议对不连续报文不加处理,采取简单丢弃策略,则将导致超时,重传数据分段,进而增加网络负载,导致网络拥塞,降低传输效率,因此协议需要高效处理乱序数据分段[4]。现有传统的TCP 分段乱序重排采用软件实现,接收端收到TCP 分段后,在乱序链节点中依次向后查找,直至将乱序分段插入正确节点,该方式灵活性差,消耗时钟周期长且占用中央处理器(Central Processing Unit,CPU)的资源,降低了处理器性能[5]。

本文提出了一种基于共享存储技术的乱序TCP分段重排硬件电路设计方案,不仅能够克服内容寻址存储器(Content Addressable Memory,CAM) 或三态内容可寻址存储器(Ternary Content Addressable Memory,TCAM)高功耗以及可扩展性差的缺点,而且收发缓存总量确定的条件下,通过共享存储动态为每一条连接分配存储空间,能够控制网络流量总量,缓解网络拥塞,提高缓存利用率,也能够充分发挥硬件电路并行处理高速的优点,有效提升处理器性能[6]。

1 TCP 协议硬件处理电路的结构设计

TCP 协议处理电路主要由TCP 发送和接收模块构成,如图1 所示。TCP 发送模块包含TCP 发送控制(tx_tcp_ctl)、发送指针队列(tx_ptr_qm_hash)、发送窗口(tx_win)和定时器管理电路(ttl_gen);TCP 接收电路包含TCP 接收控制电路(rx_tcp_ctl)和接收指针队列电路(rx_ptr_qm_hash)。发送缓存管理电路(TX_BM)控制TCP 分段的发送策略。发送控制电路每发送一个TCP 分段,超时定时器电路启动一个定时器来控制报文段重传,计算往返时延,预估超时值大小,同时发送窗口电路根据确认信息管理发送窗口,实现流量控制[7]。接收控制电路根据接收的TCP 分段,产生分段起始序号、长度和控制状态信息并发送至接收指针队列电路。接收指针队列电路根据数据分段控制状态信息,将按序分段信息发至接收缓存管理电路(RX_BM),由接收控制电路交付数据;将乱序分段控制信息存储于哈希链表存储器中进行分段重排,接收缓存管理模块缓存乱序分段数据。

图1 TCP 协议处理电路内部结构

2 乱序TCP 分段重排电路设计

2.1 设计思路

TCP 拥塞控制是通过滑动窗口进行调节,收发端各维护一个滑动窗口,窗口大小随网络拥塞程度变化。窗口内数据分段可以接收和发送,窗口外的数据分段不可以接收和发送[8,9]。接收窗口内按序到达的数据可以直接交付给应用层,非按序到达的分段必须先进行缓存,待缺省的分段到达后重新排序再交付给应用层。乱序TCP 分段重排功能是根据接收队列电路提取的TCP 分段起始序号、数据长度、流号判断分段是否乱序。若是乱序分段,将分段起始序号、数据长度、流号作为关键字,进行哈希计算,以哈希值为地址查找哈希链表头RAM,根据查找结果执行添加、删除和匹配操作。

2.2 哈希查找电路设计

哈希散列算法广泛应用于以太网交换机的转发表查找和路由器的路由表查找中,利用较小的存储空间实现高速查找功能。

哈希链表查找电路的基本结构如图2 所示。本设计中,hash_ll 电路内部包括一块哈希链表头(hash_ll_head)存储器、一块hash_ll 存储器以及hash_ll 状态机;外部电路包括哈希值运算电路和外部匹配结果查找电路。hash_ll 电路主要完成TCP 分段信息表项添加、删除和查找功能。表项添加主要完成乱序TCP分段信息的添加,外部哈希查找管理电路提取待匹配的关键字。采取循环冗余校验(Cyclic Redundancy Check,CRC)计算方式,取校验值低16 位作为哈希值,查找链表中是否存在该乱序分段,若不存在,则将表项加入链表,确定表项在hash_ll存储器中的位置,执行表项插入操作;若存在,则直接丢弃该表项信息。表项删除主要完成删除乱序链表中重新排序后按序交付分段数据表项,归还链表指针和释放接收缓存空间。表项查找主要完成接收端数据分段的查重及乱序分段排序,根据查找匹配结果读取相应查找结果的存储器数据,能有效避免数据的重复接收,进一步提高缓存利用率[10]。

图2 哈希链表查找电路结构

2.3 接收指针队列电路设计

本文接收指针队列电路的设计重点在于乱序TCP分段在共享缓存中的高效管理。共享存储技术以其结构简单、存储资源利用率高、低时延的特性而广泛应用,文章引入共享存储管理,旨在解决软件、CAM和TCAM 查找排序的缺点。接收指针队列电路产生TCP 分段数据在共享缓存空间中的控制信息,以此高效调度乱序TCP 数据分段的接收、排序,同时接收指针队列电路还产生发送控制电路所需的信息,完成TCP 分段数据的收发。下面主要介绍接收指针队列电路的工作机制。

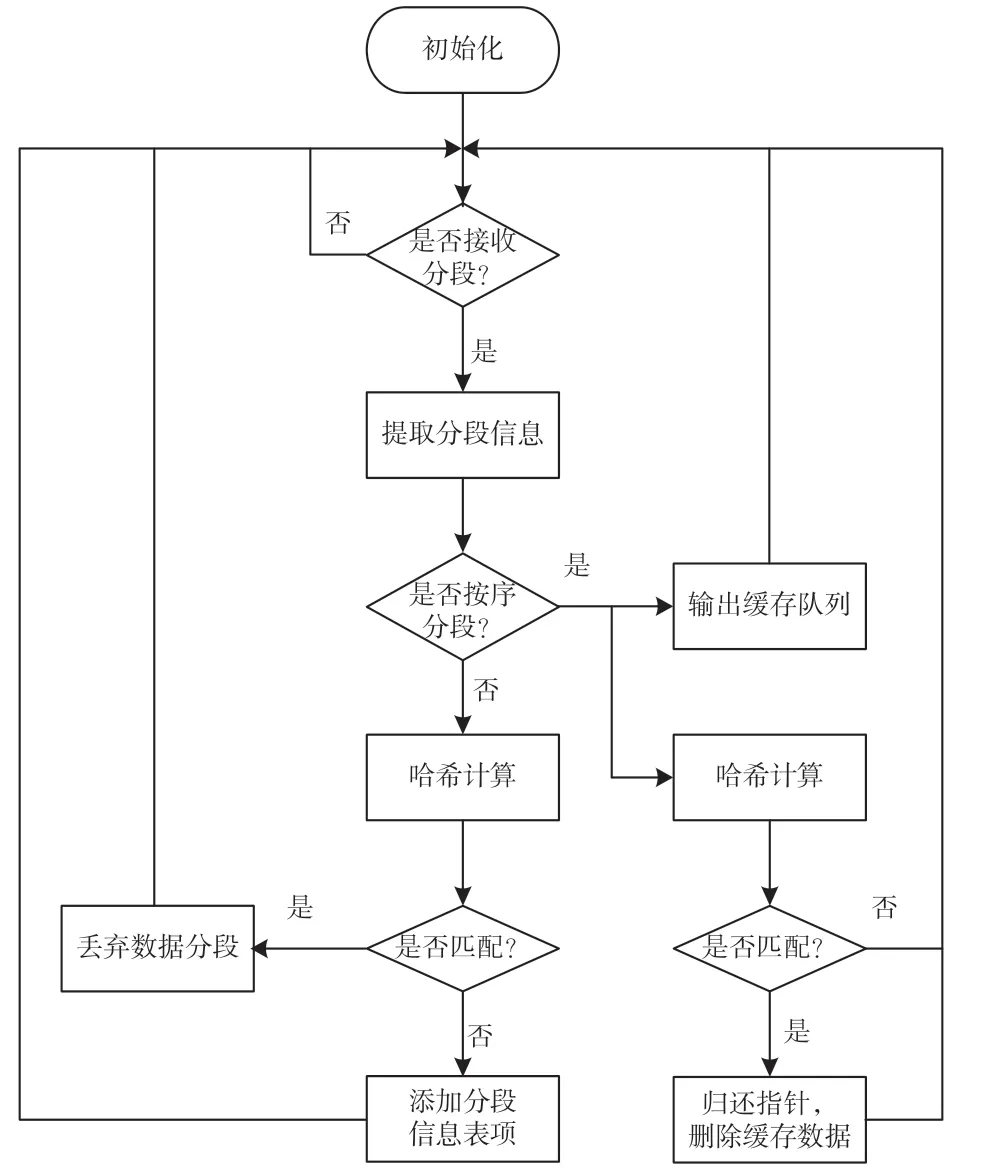

接收指针队列电路完成分段排序的功能在一块哈希链表SRAM 中实现,该SRAM 用于存储接收分段的信息,数据结构包括分段长度、流号、序号和前后表项地址。电路的工作流程如图3 所示,在正常接收数据分段前,状态机会先进行电路的初始化和CPU初始化操作,电路初始化操作完成哈希链表电路、自由指针电路的初始化以及接收端初始序号与接收缓存区大小的分配。完成初始化操作后,状态机会不停检测接收控制电路是否收到TCP 分段数据,如果收到分段数据,则先根据接收控制电路提取出分段数据的头部信息,如数据分段起始序号、长度和流号,根据控制状态信息分别完成相应操作。

图3 接收指针队列电路工作流程

如果是分段接收,状态机会比较接收数据分段的序号与接收窗口中期望接收分段的序号大小,如果小于,则说明该分段数据已经接收并交付应用程序,直接丢弃处理;如果等于,则说明该分段是按序到达的分段;如果大于接收窗口左边界小于接收窗口右边界,则说明是非按序到达的分段;如果大于接收窗口右边界,则说明分段数据超出接收窗口上界,直接丢弃。

如果是TCP分段非按序到达,根据分段头部信息,计算hash 值进行哈希查找,判断hash_ll 存储器中是否存在当前乱序分段信息。如果有乱序分段,则说明是重传分段,对接收到的乱序分段进行丢弃处理,向发送控制电路提供拟接收确认字符(Acknowledgement,ACK)值,接收窗口大小不变;如果无乱序分段,将分段信息存储在hash_ll存储器中,记录相应位置信息,并将分段数据存储在接收缓存中,同时向发送控制电路发送期望接收的ACK 值,调整接收窗口大小。

如果是按序到达,则向输出队列中缓存当前接收分段的指针信息。判断hash_ll 存储器中是否有乱序分段信息。如果没有乱序分段,则向发送控制电路提供当前接收数据分段的ACK 值,接收窗口值不变;如果有乱序分段,根据当前接收分段数据信息进行hash 计算,判断乱序分段中是否存在当前接收分段数据的后续分段数据信息,如果存在,则根据后续分段数据信息读出缓存数据交付应用程序,同时归还自由指针,依此类推,完成缓存数据读取和自由指针归还,直至链表内无法查找到后续分段信息,同时每完成一次数据交付对接收窗口大小进行调整,向发送控制电路提供拟接收ACK 值;如果不存在后续分段信息,则向发送控制电路提供拟接收ACK 值,接收窗口大小保持不变。

3 仿真结果与分析

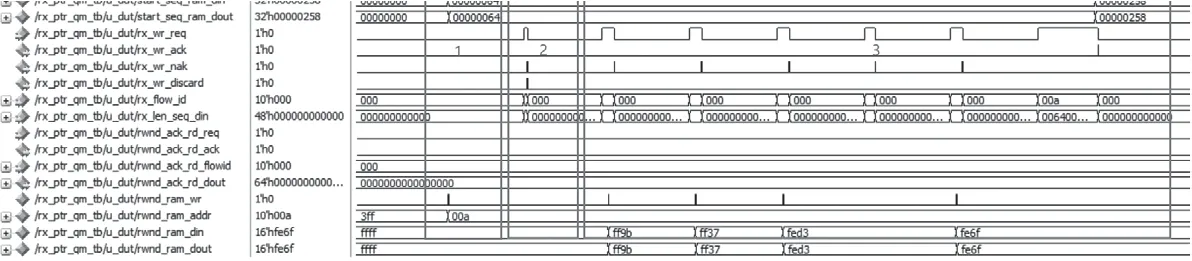

本文以Xilinx ZYNQ-7020 开发板为硬件平台搭建接收指针队列电路,其数据分段乱序重排的仿真波形如图4、图5 所示。图4 中1 处CPU 初始化,发送序号为100,字节流号为10,所以此接收电路期望收到的第一个数据分段的序号值是100,接收窗口值设置为最大64 kB;2 处到达一个初始序号值为50,流号为10,长度值为100 的分段,起始序号小于窗口起始值分段,此分段被丢弃,同时向发送控制电路提供序号为100 的ACK 值;3 处到达一组乱序分段,序号分别为为200、300、400、500,长度值均为100,经过hash 查找后给出查找失败se_nak 信号,将乱序分段执行表项添加,此时接收窗口值减小,分别向发送控制电路发送ACK 值为100 的信息;最后接收到序号为100、长度为100 的分段后,返回查找成功se_ack 信号,向发送控制电路发送ACK 为600 的信息,同时调整接收窗口大小。图5 中4 处给出自由指针变化,接收乱序分段时读取自由指针,存放分段控制信息,最后接收到序号值为100,长度值为100的分段后,执行清除请求,清除对应哈希链表,归还自由指针,释放缓存,调整接收窗口值;5 处为接收窗口以及ACK 值变化情况,接收乱序分段时,接收窗口减小,待接收到按序分段后,归还自由指针,调整接收窗口值和ACK 值;6 处为hash 查找过程,当接收乱序分段时执行查找和添加工作,按序分段到达后,执行查找和清除功能。

图4 数据分段乱序到达仿真波形

图5 数据分段hash 查找及自由指针变化仿真波形

4 综合结果分析

电路在Xilinx ZYNQ 7000 系列的现场可编程门阵列(Field Programmable Gate Array,FPGA )上进行了实现和综合,得出的综合结果如表1 所示。电路消耗了1 116 个查找表、1 309 个触发器以及43 块BRAM,接收数据采用片外DDR3 进行存储,片内关键资源消耗量较低,对比CAM 或TCAM 器件具有很大优势。电路综合后频率可达127 MHz,查找排序1次乱序TCP 分段最长不超过35 个时钟周期。该电路在采用127 MHz、位宽为32 位的DDR3 存储器时,其读写峰值带宽大于32.5 Gb/s,读写处理200 字节的TCP 分段需要7 个时钟周期,接收指针队列电路数据处理速度可达4.8 Gb/s,能够满足高速网络需求。

表1 综合结果报告

5 结 论

本文给出一种基于共享存储技术的乱序TCP 分段重排电路设计方案,详细说明了乱序重排电路的工作原理,仿真分析及综合结果表明,采用基于共享存储技术的乱序TCP 分段重排电路能够有效降低硬件资源消耗,提高处理效率,乱序重排处理速度达到吉比特,可以满足高速网络设计需求,尤其在数据中心服务器应用方面,TCP 分段乱序重排电路具有重要的实践意义。