基于FPGA 短波发射机音频AGC 算法的设计与实现*

柯乐乐,方 圆,王 毅,吕迎春

(1.同方电子科技有限公司,江西 九江 332002;2.军委装备发展部军事代表局驻镇江地区军事代表室,江苏 镇江 212000)

0 引言

在短波电台通信中,基带信号传输距离、音频源的不稳定性等因素都会使进入发射机前端的音频信号幅度变化比较大[1]。为了使得激励单元能够接收到幅值稳定的音频信号,需要对射频输出之前的音频信号进行自动增益控制(Automatic Generation Control,AGC)算法处理。为了减小运算量,一般会在采样率较低的阶段进行AGC 处理。AGC 处理除了使输出的音频幅值相对稳定,还有一定的噪音处理功能。音频AGC 必须实时跟踪输入音频信号的幅值变化,一方面要减小不期望因素的干扰,另一方面要较准确地反映音频信号的幅度变化,同时还要平衡AGC 处理带来的信号抖动和信号延时。运用数字化处理技术,在现场可编程门阵列(Field Programmable Gate Array,FPGA)器件上实现数字音频AGC 算法,可以使得AGC 控制更加精确,运行更加稳定[2]。

1 AGC 原理和分类

AGC 作为自动控制领域的研究对象,在实际工程中被广泛应用,比如语音系统中对声音大小的调节,电机控制中对功率的调节等[2]。在通信领域中,AGC 是无线接收系统重要的组成部分,它会根据输入信号的幅值大小动态调整接收系统的增益,从而提高接收系统的性能[3-6]。根据不同的实现方式,AGC 可分为模拟AGC 和数字AGC。

模拟AGC 电路结构主要包括检波器、滤波器、比较器、增益控制和可变增益放大器。经过检波和滤波后可以得到输出信号的幅值,然后与参考电平进行比较得到电平误差,增益控制电路根据电平误差产生信号控制可变增益放大器的增益值,从而完成对输入信号的调节。

数字AGC 分为数控AGC 和全数字 AGC。数控AGC 包括模数转换器(Analog to Digital Converter,ADC)、数模转换器(Digital to Analog Converter,DAC)、可变增益放大器、数字信号处理单元。数控AGC 输出的信号经过ADC 采样后将模拟信号转换为数字信号;数字信号处理单元根据输出信号计算出信号幅值,并与设定的参考信号幅值进行比较从而得到误差值,再通过增益控制算法计算得到对应的增益值,最后通过DAC 将增益值转换为模拟信号控制可变增益放大器。全数字AGC 包括ADC、数字乘法器和数字信号处理,ADC 对输入信号采样,然后与增益值相乘后得到输出信号,并将输出信号反馈到数字信号处理单元,从而得到下一次的增益值。

模拟AGC 电路器件极易受外界因素影响,对干扰信号比较敏感,导致其稳定性和可靠性都比数字AGC 差。数字AGC 对信号的调整更加精确,实现方式灵活,电路集成度和成本都比模拟AGC 低。因此,数字AGC 更符合软件无线电的发展要求,会逐渐取代模拟AGC。

2 数字AGC 指标参数

AGC的指标参数是衡量AGC性能的重要依据,数字AGC 的指标参数主要包括动态范围、稳定时间和环路稳定性[6-7]。

AGC 电路的动态范围是表示对输入信号控制能力的参数。因为AGC 的作用是将变化很大的输入信号调节到输出稳定在固定范围内,所以当输入信号的幅值变化越大且输出信号的变化范围越小时,AGC 的动态范围就越好。

稳定时间是指输入信号幅值发生阶跃变化时,输出信号从阶跃时刻到稳定时所需要的时间。稳定时间的选取非常关键,不但要考虑信道的特性,还要考虑接收信号的某些参数,比如调制速率、信号功率变化速率等。实际工程应用中,数字AGC 的稳定时间一般要可控,这不仅和控制算法有关,还和信号的采样周期有关。

理论上,数字AGC 将输入信号幅值调节到固定范围内后,数字增益值将不会发生变化。但在实际工程使用中,由于噪声信号干扰或者对输入信号幅值的估计存在误差,数字增益值可能会在某个值附近不停变化,导致AGC 输出信号幅度在一定范围内抖动。如果抖动的次数很频繁或者信号抖动的幅值比较大,会影响AGC 后级处理。

3 短波发射机中数字AGC 设计

短波发射机中,模数转换(Analog to Digital,AD)芯片采集到的线路音频和麦克风音频以及外部设备输入进来的数字音频允许的幅值范围是-20~10 dB,需要经过AGC 设计后使输入的信号稳定在0 dB。由于AGC 的期望值是一个定值,实验中发现,输出信号会不断调整,造成输出信号幅度不稳定[8],因此,在AGC 期望值的基础上,设计了一个音频信号输出稳定的动态范围,即在AGC 期望值的基础上允许上下浮动0.1 dB,输出音频信号幅值在此动态范围内,则认为信号是稳定的,不需要再进行调整。

根据输入音频信号幅值的要求,增益调整范围固定在-10~20 dB,为了防止幅值计算错误或信号干扰影响幅值计算,当计算出来的增益大于一定值时,以一定值为单位逐次调整,直至信号稳定在允许的幅值范围内,根据发射机对AGC 调整速度的要求,来确定需要进行逐次调整的最小增益值a和单位b。

AGC 算法主要在FPGA 中实现,FPGA 采用复旦微电子公司的FMQL 系列的FMQL45-FFG900,采用FPGA+ARM 体系,不仅拥有丰富的逻辑控制器,而且拥有高性能处理器,其处理器为四核A7处理器,工作频率可达1.0 GHz,逻辑资源丰富,逻辑单元为350 000,查找表为218 600,触发器为437 200,乘 法 器 为18×25,MACC 为900,4QUAD 高速GTX 收发器,支持PCIE GEN2×8、2 个AD 转换器,可以测量片上电压、温度感应。模拟AD 采用中国电子科技集团公司第24 研究所的SAD7656 音频AD 芯片,SAD7656 芯片具有6 个独立采样通道,最大采样速率为250 kHz,信噪比(Signal-to-Noise Ratio,SNR)为86 dB@50 kHz,数据接口为16 bit 并行接口或串行外部设备接口(Serial Peripheral Interface,SPI)。

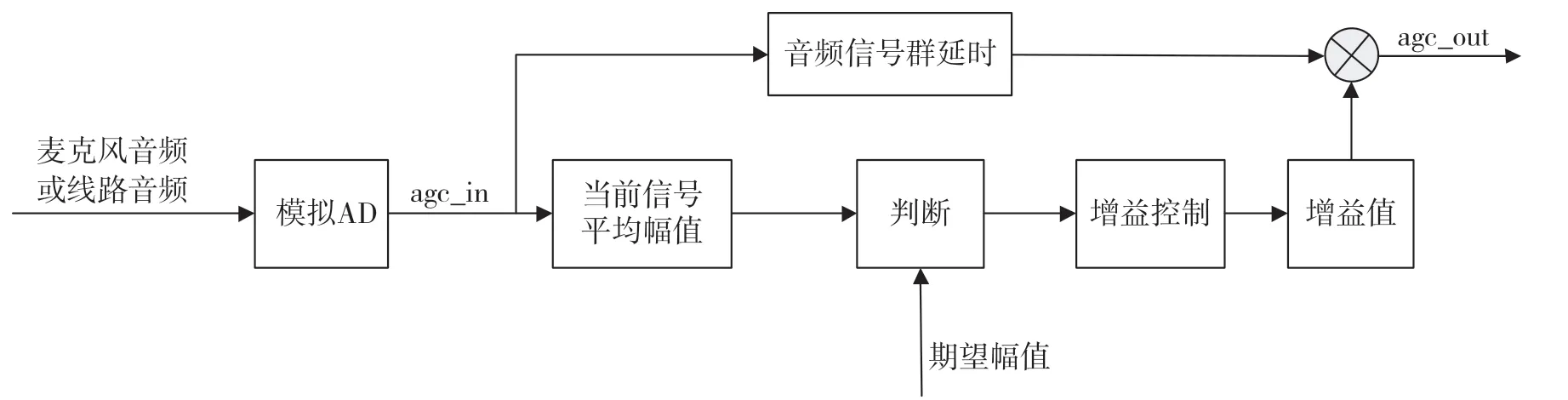

本方案所采用的数字AGC 的设计原理如图1所示,主要包括模拟AD 采样、当前信号平均幅值计算、平均幅值和期望幅值比较、增益控制、增益值乘当前信号得到输出信号。

图1 数字AGC 设计原理

FPGA 中信号为并行、流水、定点处理模式。在图1 中,计算信号平均幅值需要采集一段时间内的信号,并且判断和计算都需要耗费一定的时间,导致计算出的增益值不能与计算该值的数据同步,造成输出信号功率频繁抖动[9]。增益值通过迭代计算得到,AGC 控制范围越大,迭代收敛时间越长,音频数据与增益值相差越大,输出信号功率抖动越明显。

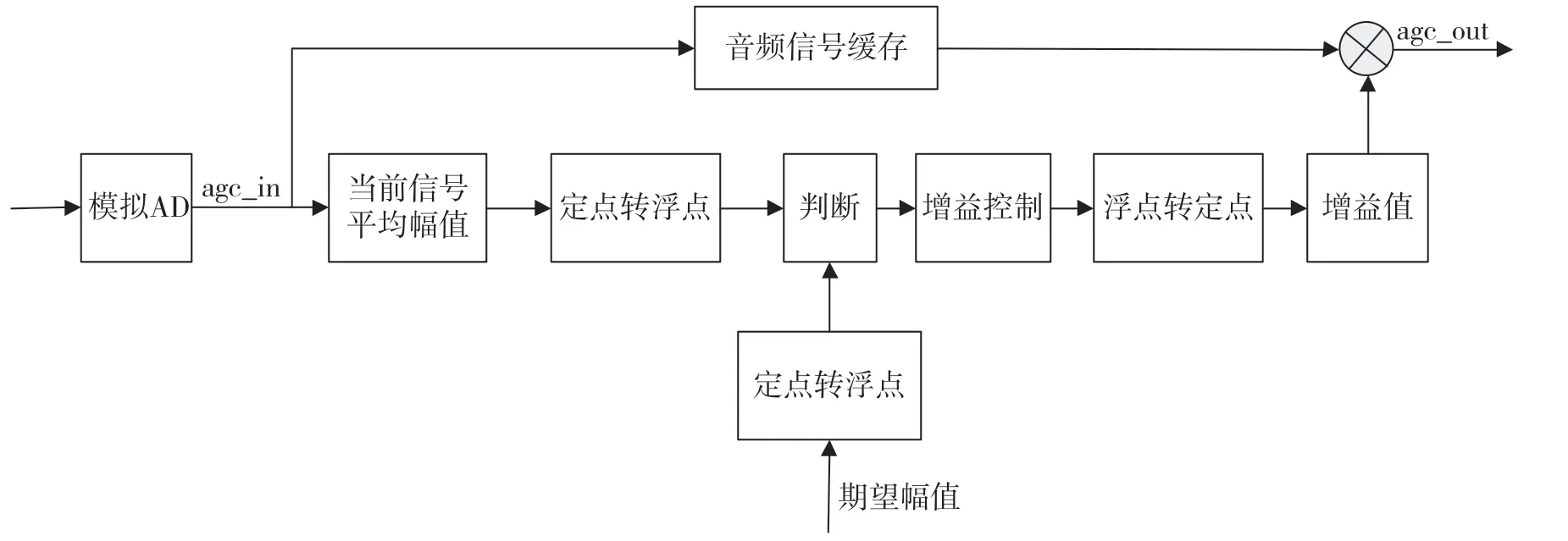

为消除数据不同步产生的抖动,本文采用的信号同步处理方法是将输入的数字音频信号存入RAM中进行群延时处理,信号缓存长度等于增益值更新的时间长度,这样就可以得到稳定的信号输出[10],原理见图2 所示。

图2 加入同步处理的数字AGC设计原理

定点计算中数据相乘可能会导致信号位数溢出,而且计算精度不高,所以将图2 中的判断模块和增益控制模块采用浮点运算,另外为了加快运算时间,浮点运算的时钟采用FPGA 的系统时钟,浮点AGC 设计流程如图3 所示。

图3 浮点同步数字AGC 设计原理

4 AGC 算法仿真和实现

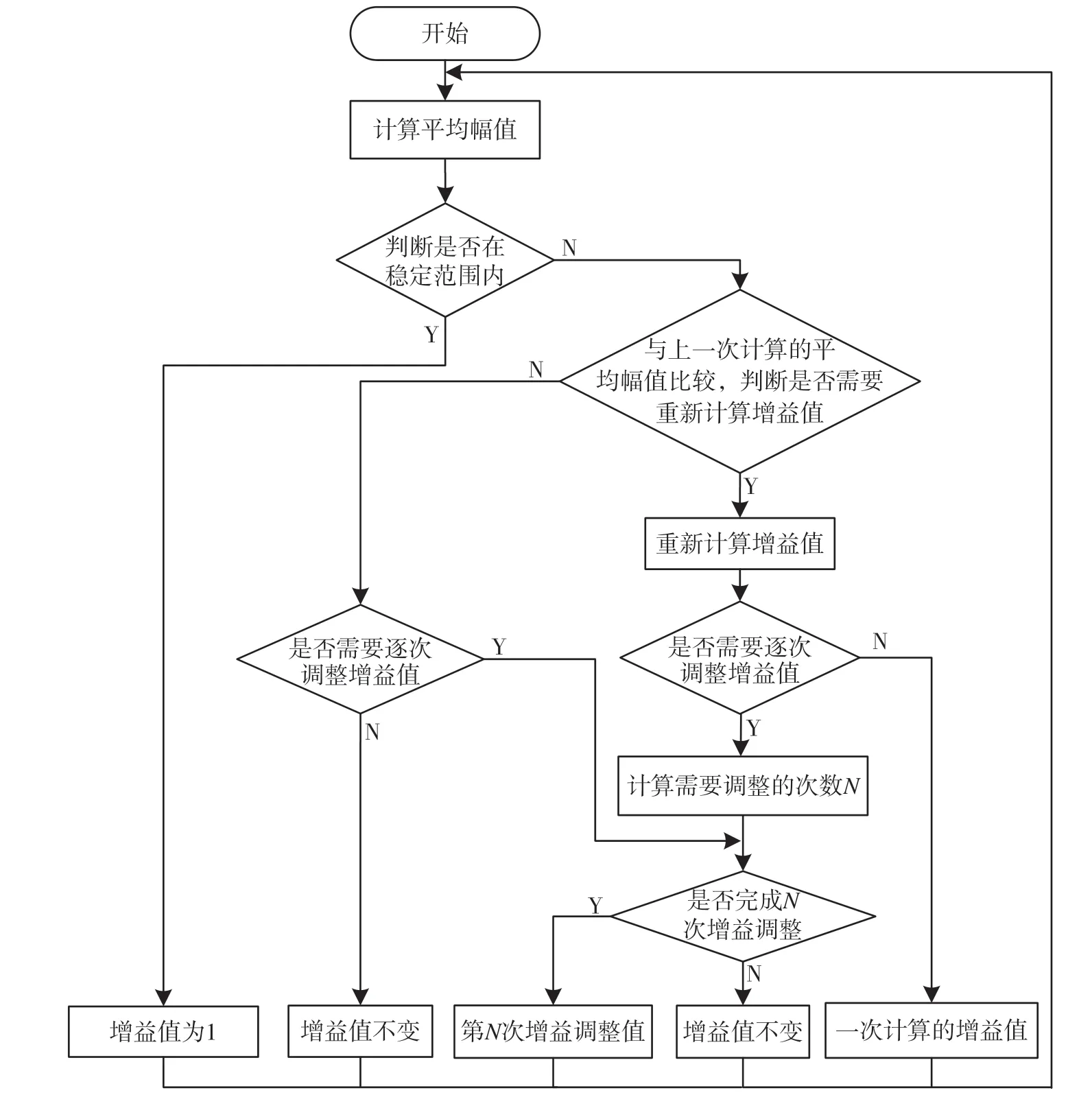

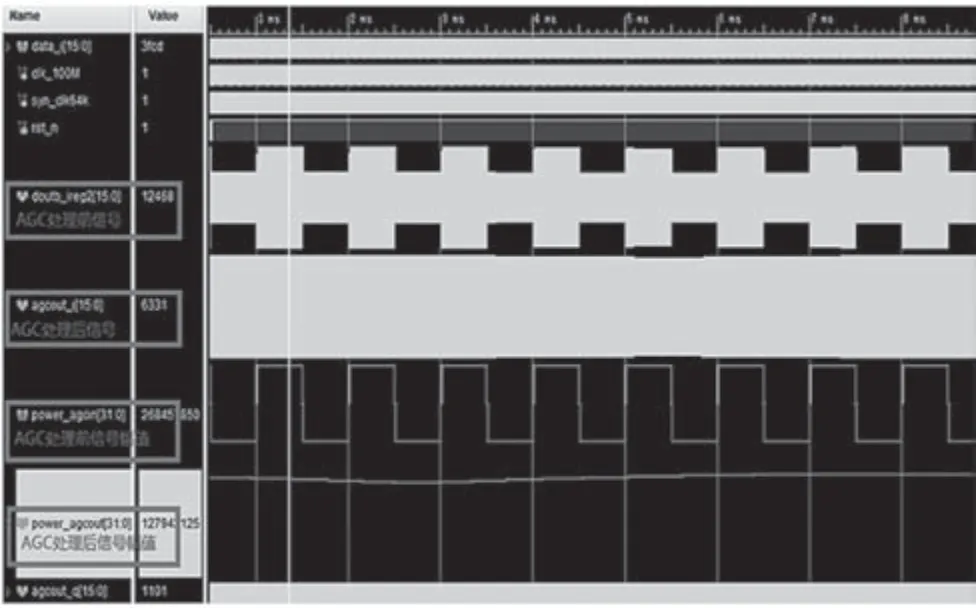

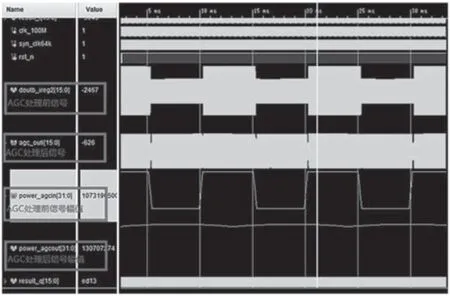

本文设计的AGC 算法流程如图4 所示。当计算得到的输入信号的平均幅值在稳定范围内时,则输出增益值为1,作用于群延时后的信号。当计算得到的输入信号的平均幅值大于期望的幅值稳定范围时,输出计算的当前增益值,作用于群延时后的信号。当计算得到的输入信号的平均幅值小于期望的幅值稳定范围时,与上一次计算的增益值比较,如果变化超过0.1 dB,则计算增益值并判断是否需要逐次调整增益值,如果不需要,则输出当前计算的增益值,作用于群延时后的信号;如果需要,则逐次调整增益值,计算需要逐次调整的次数N,判断是否完成N次调整,如果已完成,则增益值不变,否则要计算出第n(n 图4 短波发射机中数字浮点同步AGC 算法流程 仿真模拟音频输入单音和双音,信号幅值范围为-20~10 dB,首先仿真幅值多次改变的单音输入信号如图5 所示,可以观察到输入的音频信号的幅值隔一段时间会改变,仿真进入发射机前端的音频信号幅度忽大忽小。经过AGC 算法后,将输入音频信号的平均幅值调整到0±0.1 dB,在图5 中,可以观察到经过AGC 处理后信号的平均幅值一直稳定在规定的范围内,满足设计要求。 图5 单音信号经过AGC 算法处理仿真 当输入音频信号是幅值多次改变的双音信号时,经过本文设计的AGC 算法后,也可以将输入音频信号的平均幅值调整到0±0.1 dB,仿真如图6所示,图中的信号幅值是指一段时间内信号的平均幅值,当音频信号的平均幅值发生改变时,经过一段短暂时间的调整,AGC 处理后的信号平均幅值会稳定在要求的范围内,AGC 调整时间满足发射机功率稳定时间要求。 图6 双音信号经过AGC 算法处理仿真 将此AGC 算法应用到某型号的短波发射机平台上时,用综测仪接入音频信号,不断改变输入音频信号的幅值,经过AGC 算法处理后的信号的幅值会快速调整到一定的范围内,使发射机输出功率稳定在要求的范围内;接入麦克风,开启PTT,当喊话声音忽大忽小时,即输入信号幅值波动较大的情况下,能在短时间内调节输出信号幅值,使其快速收敛,为后级电路提供稳定的输入信号,且方案简单,易于实现[11]。另外,AGC 处理后输出信号幅值的参考值是可调的,算法灵活性和适应性强。 本文首先对AGC 算法的原理、分类、指标进行了介绍,其次重点分析了浮点同步数字AGC 算法的设计思路,最后通过FPGA 仿真和在某型号短波发射机平台上的应用验证了此算法的可行性。

5 结语