一种多种接口时序兼容性验证设计方法

杨帆 王哲

摘 要 针对接口从设备兼容性弱的问题,提出一种多种接口时序兼容性验证方法,实现了灵活、方便、可控的接口从设备时序拉偏验证功能。

关键词 时序拉偏测试 接口从设备 物联网 时序逻辑验证 兼容

中图分类号 TP206 文献标识码 B 文章编号 1000?3932(2023)03?0392?04

作者简介:杨帆(1992-),工程师,从事软件设计工作,yangfan@hed.com.cn。

引用本文:杨帆,王哲.一种多种接口时序兼容性验证设计方法[J].化工自动化及仪表,2023,50(3):392-395.

随着物联网的发展,接口种类越来越来多,应用环境越来越复杂,接口从设备需要应对各种各样的主设备,接口验证不仅局限于接口协议要求,对时序兼容性的需求也越来越高。市场上不同厂家的各类接口产品设计也存在着或多或少的不同之处,因此产品需要有较高的接口兼容性。

把接口兼容性问题拦截在验证阶段,可以降低投入市场后的兼容性风险。对于从设备接口样品验证而言,接口的兼容性测试是十分必要的,但目前尚无灵活、方便、可控的时序拉偏验证方法的报道。为此,笔者提出一种多种接口时序兼容性验证设计方法,利用上位机软件下发测试命令,通过FPGA芯片电路设计应用,灵活输出可控的接口测试时序,将时序测试结果返回上位机,从而满足从设备接口时序兼容性的要求,直观准确地测试出从设备的时序拉偏性能。

1 验证方法设计

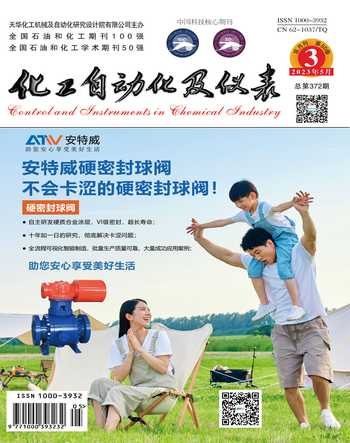

首先设计并开发FPGA芯片电路,包括5个模块:接口解析模块、存储模块、主控电路单元模块、时钟处理模块和协议处理模块,整体模块框图如图1所示。接口解析模块。选择并配置上位机与FPGA芯片电路的通信接口,上位机软件下发指令,接口解析模块对指令进行解析,根据解析结果,通过主控电路单元模块控制调用其他模块,完成指令功能。接口解析模块也具有将测试结果进行解析并通过与上位机连接的接口返回给上位机的功能。

存储模块。上位机下发存储指令,接口解析模块对指令进行解析,由主控电路单元模块将目标接口验证时序向量存储在存储模块中。上位机下发测试指令,由主控电路单元模块调取存储模块中已存储的目标接口验证时序向量,通过协议处理模块输出验证时序向量,并且将采集的从接口返回的测试结果,通过主控电路单元模块存储在存储模块中,待上位机发送测试结果读取指令时调用。

时钟处理模块。上位机下发时钟配置指令,接口解析模块对指令进行解析,通过主控电路单元模块选择高频时钟源,并经过时钟处理模块进行处理,以得到满足目标时钟时序需求的时钟时序。

主控电路单元模块。用于控制调用各模块工作。上位机下发存储指令,接口解析模块对指令进行解析,由主控电路单元将目标接口验证时序向量存储在存储模块中。上位机软件下发时钟配置指令,接口解析模块对指令进行解析,由主控电路单元模块调用选择高频时钟源,并调用时钟处理模块对时钟源进行信号处理,以得到满足目标时钟时序需求的时钟时序。上位机软件下发协议选择指令,接口解析模块对指令进行解析,由主控电路单元模块调用协议处理模块进行接口协议配置。上位机软件下发测试指令,接口解析模块对指令进行解析,由主控电路单元模块调用存储模块中已存储的接口验证时序向量,并调用协议处理模块,输出验证时序,同时协议处理模块采集测试结果,通过主控电路单元模块存储在存储模块中。上位机下发测试结果读取指令,接口解析模块对指令解析后,由主控电路单元模块调用存储模块中存储的测试结果,经接口解析模块进行解析,通过FPGA芯片电路与上位机连接的接口返回给上位机。

协议处理模块。在上位机发送协议选择指令时,接口解析模块对指令解析后,由主控电路单元模块调用协议处理模块,根据目标接口协议,对接口性能进行相应配置。在上位机发送测试指令时,经过接口解析模块解析命令后,由主控电路单元模块调用存储模块中的接口验证时序向量,经协议处理模块输出接口验证时序,并经协议处理模块采集从接口时序测试结果,通过主控电路单元模块存储在存储模块中。

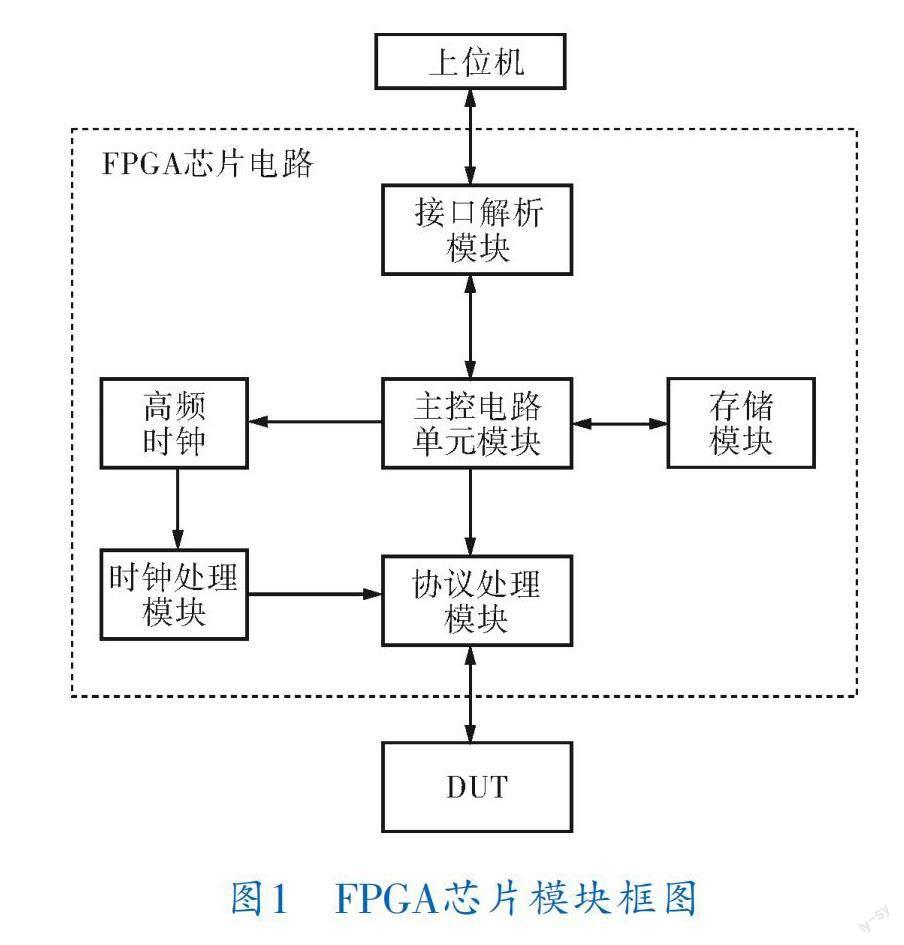

配置上位机与FPGA芯片电路的通信接口,使用上位机软件下发测试时序向量存储指令、时钟配置指令、接口协议选择指令、测试指令和测试结果读取指令。上位机接口通信结构框图如图2所示。

通过接口解析模块解析上位机指令。

通过主控电路单元模块协调控制FPGA电路各模块,验证时序向量存储的功能,选择高频时钟并对时钟信号进行处理的功能,选择接口协议并对目标接口时序进行协议特性配置的功能,时序测试功能,以及测试结果的读取功能。

通过灵活的指令配置,存储并调用不同的时序向量,从而满足对从设备接口时序拉偏验证的要求,直观准确地测试出从设备的时序兼容性能。

2 目标接口时序测试流程

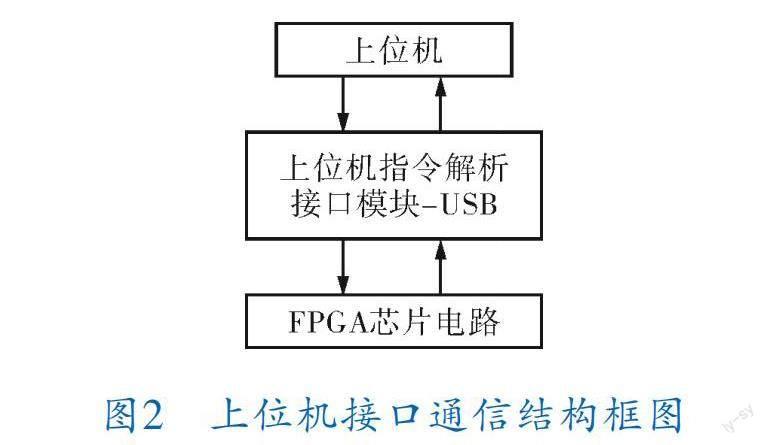

目标接口时序测试流程如图3所示。

上位机与FPGA芯片电路的通信接口。上位机软件下发指令,接口解析模块对指令进行解析,根據解析结果,通过主控电路单元模块控制调用其他模块,完成指令功能。接口解析模块也可以将测试结果进行解析,并通过与上位机连接的接口返回给上位机。

上位机下发不同的验证时序向量存储指令。由接口解析模块对指令进行解析后,通过主控电路单元模块将验证时序向量存放在存储模块中。

上位机下发时钟配置指令。FPGA接口解析模块对指令进行解析后,利用主控电路单元模块选择高频时钟源,并通过时钟处理模块对时钟信号进行处理,得到满足接口时序验证需求的时钟信号。

上位机下发接口协议选择指令。接口解析模块对指令进行解析后,利用主控电路单元模块调用协议处理模块,对目标接口时序进行协议配置。

上位机下发测试指令。接口解析模块对指令进行解析后,通过主控电路单元模块调用存储模塊中已经存储的不同的接口验证时序向量,通过协议处理模块,灵活输出验证时序,并采集测试结果,通过主控电路单元模块将其存储在存储模块中。

上位机下发测试结果读取指令。接口解析模块对指令进行解析后,由主控电路单元模块调用存储模块中存储的测试结果,经接口解析模块进行解析后,通过与上位机连接的接口返回给上位机。

重复以上操作,遍历需要的接口时序,就能满足接口时序拉偏兼容性验证。

3 方法例举

笔者举例说明本设计的具体实施方式。本设计方法使用的软、硬件实现方式,可在实际操作时指定。

第1步 设计并开发FPGA芯片电路,包括5个模块(图1)。

第2步 PC机通过USB接口向FPGA芯片电路发送I2C接口验证时序向量存储指令,接口解析模块对命令进行解析(图2)。之后,通过主控电路单元模块调用存储模块,将接收到的I2C接口验证时序向量存储在内部RAM中。

第3步 PC机通过USB接口向FPGA芯片电路发送I2C接口时钟配置指令,接口解析模块对命令进行解析后,主控电路单元模块选择时钟源,并调用时钟处理模块将高频时钟源进行信号处理(图4),即可得到满足接口时序验证需求的时钟时序。

第4步 PC机通过USB接口向FPGA芯片电路发送I2C接口协议选择指令,接口解析模块对命令进行解析。由主控电路单元模块调用协议处理模块,按照I2C协议要求配置接口设置。

第5步 PC机通过USB接口向FPGA芯片电路发送I2C接口测试指令,接口解析模块对命令进行解析。由主控电路单元模块调用存储模块,读取内部RAM中已存储的接口拉偏验证时序向量。通过协议处理模块,按照I2C协议要求输出接口验证时序。从设备接收验证时序后响应,通过协议处理模块采集响应结果,并通过主控电路单元模存储在内部RAM中。

第6步 PC机通过USB接口向FPGA芯片电路发送测试结果读取指令,接口解析模块对命令进行解析,主控电路单元模块调用存储模块,读取内部RAM中已存储的测试结果,接口解析模块对测试结果进行解析,并从USB接口向PC机返回测试结果。

第7步 重复以上操作,遍历需要验证的接口时序。

4 结束语

笔者提出的多种接口时序兼容性验证设计方法,通过指令操控,利用FPGA芯片电路灵活可编程的优点,可以灵活、可控地输出多种目标接口时序,并根据存储的接口时序向量对接口时序进行拉偏测试,满足了市场上从设备接口的时序兼容性验证需求。

(收稿日期:2022-08-16)