基于MCIMX6Q6AVT10AC的可配置神经网络硬件设计

朱春燕

摘要:当前硬件在不同环境下适应性较差,为此需要提高硬件的运行性能,文章提出基于MCIMX6Q6AVT10AC的可配置神经网络硬件设计研究。将STMicroelectronics的ARM微控制器STM32F429BI作为硬件的MCIMX6Q6AVT10AC微处理器,在硬件电源管理方面集成线性调节器,以实际引脚输入/输出电源状态为基础在硬件内部生成不同区域的电压水平。为满足MCIMX6Q6AVT10AC为核心硬件的可配置需求,本研究设置了具有交织模式的16位、32位和64位3种模态内存接口以及辅助驱动装置。测试结果表明,设计硬件运行期间的正峰值衰落和负峰值衰落程度分别为8.94%和8.89%,每个周期内相位峰值失真小于15 mV,能够满足相关规范要求。

关键词:MCIMX6Q6AVT10AC;可配置神经网络;线性调节器;交织模式;内存接口;辅助驱动装置

中图分类号:TP389.1 文献标志码:A

0 引言

为确保计算集中运行能够在海量算法负荷下实现稳定执行,构建稳定可靠的硬件环境十分必要[1]。现阶段,神经网络作为一种应用较为广泛的算法,针对其设计能够结合实际应用环境进行适应性配置调节的硬件成为计算机领域关注的重点[2]。从硬件的具体运行逻辑角度分析,其本身是以处理器为核心的系统性组织结构,这就决定了处理器在硬件中的控制性地位[3]。MCIMX6Q6AVT10AC作为一种具有较高性能的微处理器,其可以实现对多元任务的快速处理,协调各配件之间的关系,确保硬件在运行期间能够保持流畅,避免由于任务堆积导致的运行卡顿等问题。在实际应用时,受不同环境的应用需求以及基础构件设置的影响,需要硬件能够结合实际情况进行差异化调节。因此,硬件需要具备较强的可配置属性。本文提出基于MCIMX6Q6AVT10AC的可配置神经网络硬件设计,通过试验测试分析验证了设计硬件在计算机环境中的运行效果。借助本文的研究,希望可以为实际的神经网络相关计算系统提供可靠的硬件基础。

1 可配置神经网络硬件设计

1.1 MCIMX6Q6AVT10AC的选择

为确保硬件能够适应神经网络的层级运行逻辑执行需求,结合实际应用环境实现对相关构件的差异化配置,本文将STMicroelectronics的ARM微控制器STM32F429BI作为硬件的微处理器,采用STM32F429BI支持SMD和SMT两种形式进行安装,极大地降低了实际使用阶段的局限性。STM32F429BI的核心为ARM Cortex M4,可执行的程序存储器大小为2.0MB,数据RAM大小为260 KB,数据总线宽度为32 bit,对应的ADC分辨率可以达到12 bit,在最大180MHz的时钟频率,可以实现对运行逻辑的快速执行,大大降低了等待的时间。除此之外,STM32F429BI输入和输出端的总数量为168个,具体的类型包括CAN、I2C、SAI、SPI、UART/USART、USB。在1.7~3.6 V的电源电压下均可以实现稳定运行。考虑到硬件的运行环境存在较大差异,STM32F429BI适应性通过Tray封装的方式对其可以运行的工作温度阈值进行调节,对应的范围为-40~85℃。ADC通道数量为24Channel,同时还搭载了14个基础计时器和1个Watchdog Timer看门狗计时器。在重量上,STM32F429BI仅2.587G,不会对硬件造成额外的安装负担。

1.2 集成电源管理设计

本文将STM32F429BI处理器作为硬件的核心构件,为适应其运行电压范围。本文在硬件电源管理方面集成了線性调节器,在硬件内部生成不同区域的电压水平。通过这样的方式实现简化硬件电源管理结构的目的。其中,图1为本文设计的用于识别特定零件特征的电压传输线集总模型。

如图1所示,本文设计的硬件电源管理是以实际引脚输入/输出电源状态为基础进行的。当引脚(NVCC\\uxxx)的输入/输出电源关闭时,对A11 IO引脚进行外部驱动关闭。考虑到在实际的运行过程中,频繁的状态调节会导致信号峰值的大幅衰落,进而引起由于反向电流带来的硬件内部闭锁和功能不良问题,因此本文对每个引脚的输入/输出电源的信息进行细化设置。当硬件不使用SATA接口时,保持SATA\\uU VP和SATA\\u VPH电源处于接地状态,其余端口则保持断开的状态。同时,当SATA\\uVP电源处于开启状态时,则SATA\\uvph电源转换至关闭状态。通过这样的方式避免由此带来的过度功耗和信号衰落问题。考虑到在以神经网络为主体架构的系统运行过程中,各个接口的信息传输是阶段性的。因此,当PCIE接口处于待机状态时,本文设计硬件的PCIE\\uVP、PCIE\\uvph和PCIE\\uvPTX电源应处于接地状态,其余端口保持断开状态。不仅如此,为了降低由于信号自身衰落属性带来的传输影响,本文设置PCIE-VP电源与PCIE-VPH电源之间的关系为对立状态。即当PCIE-VP电源处于开启状态时,则PCIE-VPH电源默认恢复断开状态;当PCIE-VP电源处于关闭状态时,则PCIE-VPH电源默认启动开启状态。

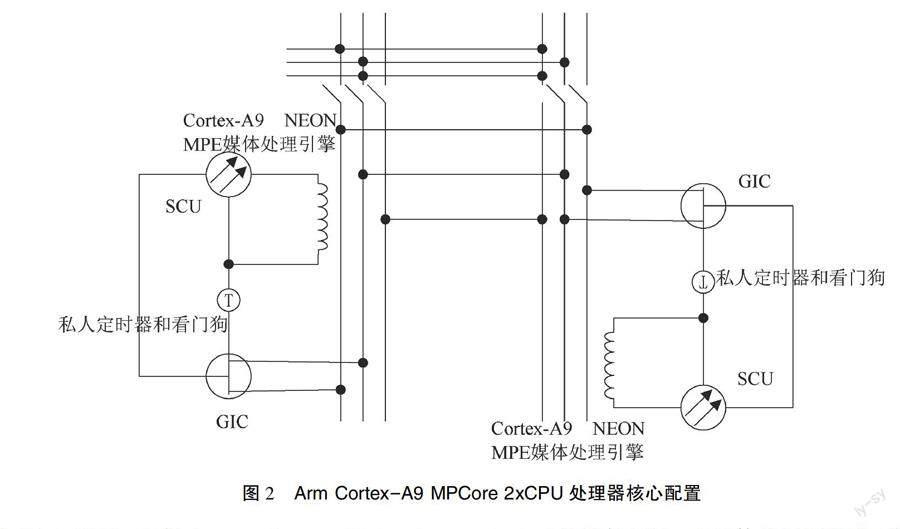

1.3 辅助控制构件设计

以神经网络为基础的系统在运行过程中需要对多个阶段的适应性同时进行计算,这就在一定程度上加大了MCIMX6Q6AVT10AC的运行压力。为了降低由此带来的运行负荷,本文为硬件设置了以对称形式存在的Arm Cortex-A9 MPCore 2xCPU处理器核心配置。具体如图2所示。

如图2所示,在每个Arm Cortex-A9 MPCore 2xCPU处理器核心配置上,分别构建大小为32 KB的一级指令缓存空间及大小为2 KB的一级数据缓存空间,并利用私人定时器和看门狗对Cortex-A9 NEON MPE媒体处理引擎的协同处理频率进行管控。在此基础上,本文为每个核心构建了包含128中断支持的通用中断控制器装置(GIC),同时为G1obal计时器和Snoop控制单元(SCU)分别设置了大小1MB的统一I/D二级缓存空间。在具体的运行阶段,其可以通过4个核共享二级缓存的2个64位主AXI总线接口实现输出。除此之外,本文为MCIMX6Q6AVT10AC搭载了32×64位通用寄存器的NEON寄存器文件,其具体的内存包括96 KB的HAB引导ROM,256 KB的OCRAM内部多媒体/共享快速访问RAM,16 KB的保护非安全RAM。通过这样的方式缓解MCIMX6Q6 AVT10AC在运行期间的压力。

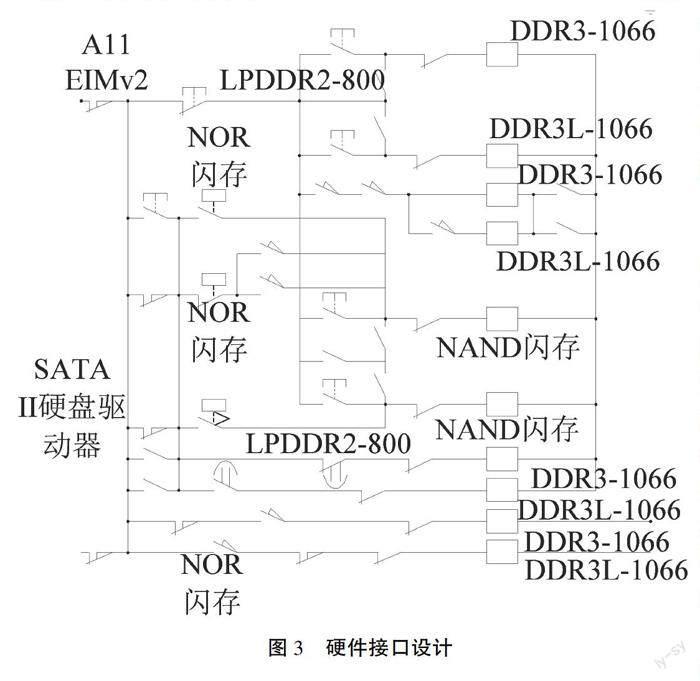

1.4 外部接口设计

本文以MCIMX6Q6AVT10AC为核心设计的硬件具有可配置的属性,因此在设计阶段充分考虑了不同应用环境下对不同类型装置的连接需求。对接口的具体设计如图3所示。

如图3所示,在接口设计上,内存接口包括16位、32位和64位3种模态的DDR3-1066、DDR3L-1066和1/2LPDDR2-800通道,并且将接口设置为DDR交织模式,确保其适用于双32LPDDR2的连接需求。不仅如此,本文在上述基础上还为硬件设计了8位NAND闪存,确保其可以支持原始MLC/SLC、2 KB、4 KB和8 KB页面大小,当并行存在BA-NAND、PBA-NAND、LBA-NARD、OneNANDIM等连接需求时,可以实现最高40位的配置连接。NOR闪存设置为16/32位2种模式,通过将A11 EIMv2引脚安装在其他接口上,使得16/32位PSR AM能够与蜂窝RAM之间建立互动关系。在多个构件配置并行连接于本文设计的硬件之上时,在一定程度上其运行负担会增加。为此,本文在MCIMX6Q6AVT10AC上连接了大小为3.0GTP的SATA II硬盘驱动器。通过这样的方式使得A1l接口的总原始pixe1速率能够达到450Mpixels/sec以上。当4个接口处于并行激活状态时,任意单一并行的24位显示端口速率均可以达到225 Mpixe1/sec。

2 功能测试

为了进一步对本文设计硬件的功能进行分析,进行了试验测试。

2.1 试验测试设计

本文在对设计硬件的实际运行效果进行测试阶段,针对神经网络的运行模式,分别对硬件运行的一致性进行测试。测试环境的设计是以新型域控架构的网关控制器为基础开展的,在具体的结构设置上包括4路以太网100BaseT1接口、1路常规以太网以及6路兼容CAN的CANFD接口,以2路LIN总线和3路可配置为3路数字输入输出支线作为载体。在此基础上,通过在硬件上连接模拟量输入信号和高边驱动输出信号,对硬件的运行情况进行分析。

根据上述设置,测试阶段的装置连接是借助CAN、LIN、以太网等汽车总线实现的,与其他的电子控制单元连接后,以通信协议的一致性规范要求为约束条件,通过路由转发的形式传递不同总线、不同通信速率的数据,以此实现各个单元之间的交互通信。此时,当设计硬件无法满足相关规范要求时,会出现信号质量恶化的问题。本文以Specification Package Revision 2.2A规范包中的具体内容为基准,对硬件的运行情况进行评价。

2.2 测试结果与分析

在测试过程中,本文首先对设计硬件的衰落情况进行分析统计,得到的结果如图4所示。

从图4中可以看出,硬件在运行期间的正峰值衰落和负峰值衰落程度分别为8.94%和8.89%,按照衰落幅值相对于峰值的比例应不高于45%的行业标准对其进行分析,可以明显看出本文设计的硬件远远高于标准值,能够满足规范要求。

在此基础上,本文Master模式下按照33.334MHz的频率向硬件发送特定扰码。其中,扰动信号发生器的运行时钟频率为11.111MHz,干扰信号的峰值为3.20 V。对于硬件峰值失真数据的采集,本文利用示波器以2 GSa/s进行采样,统计了单位周期内10个等分相位峰值信号,得到的测试结果如表1所示。

从表中可以看出,本文设计硬件在运行期间的最大信号失真值仅为9.626mV,最小值为8.269mV,按照相关使用规范定义中对每个周期内相位峰值失真小于15mV的要求对其进行分析,设计硬件满足规范要求。

综合上述测试结果可以看出,本文设计的基于MCIMX6Q6AVT10AC的可配置神经网络硬件能够实现有效稳定。

3 结语

硬件的可靠性直接相关系统能否实现稳定运行,作为系统软件运行逻辑的载体,硬件对系统信号的传输效果是决定相关控制执行质量的关键。本文提出基于MCIMX6Q6AVT10AC的可配置神经网络硬件设计,围绕MCIMX6Q6AVT10AC的属性,实现对硬件的详细设计,实现了硬件在运行期间的峰值衰落情况和信号失真情况能够达到行业相关标准。本研究可以为后续硬件设计提供参考。

参考文献

[1]许庚林,冉峰,郭爱英,等.基于FPGA的可配置卷积结构的神经网络协处理器设计[J].复旦学报(自然科学版),2021(4):482-491.

[2]范博宇,史再峰,王哲,等.一種用于激光焊接参数运算的可配置型BP神经网络计算加速器[J].激光与光电子学进展,2022(2):321-331.

[3]訾晶,张旭欣,王钰,等.基于FPGA的可配置神经网络硬件设计[J].传感器与微系统,2020(12):92-95.

(编辑 王永超)

Hardware design of configurable neural network based on MCIMX6Q6AVT10AC

Zhu Chunyan

(Suzhou Top Institute of Information Technology, Kunshan 215300, China)

Abstract: Current hardware has poor adaptability in different environments, so it is necessary to improve the performance of hardware. This paper proposes the design and research of configurable neural network hardware based on MCIMX6Q6AVT10AC. The ARM microcontroller STM32F429BI of STMicroelectronics is used as the MCIMX6Q6 AVT10AC microprocessor of the hardware. The linear regulator is integrated in the hardware power management, and the voltage level of different regions is generated in the hardware based on the actual pin input/output power state. In order to meet the configurable requirements of MCIMX6Q6AVT10AC as the core hardware, the 16-bit, 32-bit and 64-bit memory interfaces with interleaved mode and auxiliary drivers are set up. The test results show that the positive and negative peak fading degrees of the designed hardware during operation are 8.94% and 8.89%, respectively, and the phase peak distortion is less than 15 mV in each cycle, which can meet the requirements of relevant specifications.Key words: MCIMX6Q6AVT10AC; configurable neural network; linear regulator; interleaving mode; memory interface; auxiliary drive device