基于CORDIC算法的中频多路控守系统设计

龚永龙 杨青华 蔡怀海

摘要:针对无线接收技术向着大带宽、高采样的方向发展,军地的频谱管理设备已经不能滿足日常的训练和执法需求,本文提出了一种基于CORDIC算法的中频多路控守系统设计方法,直接采集超外差接收机的中频输出信号,从而实现多达32路或者64路的窄带信号提取、存储、分析、回放等。作为事后分析取证等,弥补当前设备的不足。文中介绍了CORDIC的基本原理,核心实现基于CORDIC算法的nco和子带变频器,并在Xilinx 平台上验证成功。

关键词: CORDIC;软件无线电;NCO;数字下变频;信号分析

无线电频谱是一种自然资源,由于无线电频谱是有限的,而通信技术极度依赖频谱的使用,传统的短波和超短波频段已经不满足当前通信需求了,未来通信主要依赖超高频的微波频段。而无线电接收技术也向着大带宽、高灵敏度、高采样率的方向发展,更高的速率为信号的实时分析带来了极大的困难。本文提出了一种基于 CORDIC 算法的窄带多路控守系统的设计方法,采用 CORDIC 算法实现多路窄带通信信号控守,设计满足宽带内16路任意频点的控守。

1 CORDIC算法原理

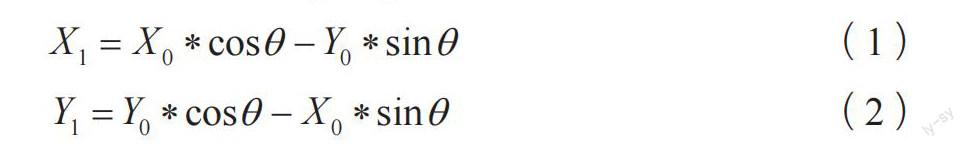

CORDIC 算法是一种数值性计算逼近的方法,其基本思想是用一系列与运算相关的角度不断偏摆从而逼近所需旋转的角度。假设初始向量为(X0,Y0)旋转θ角度之后得到向量(X1,Y1), 此向量有如下关系:

在中频多路控守系统中,采用 CORDIC 算法完成中心 NCO、子信道 NCO 的设计和频率搬移。已知系统的中心频率和宽带范围内各个子信道的中心频率;假如系统输入采样率为fs,中心频率为 fc,n 个子信道的频率为别为f1,f2…fn。

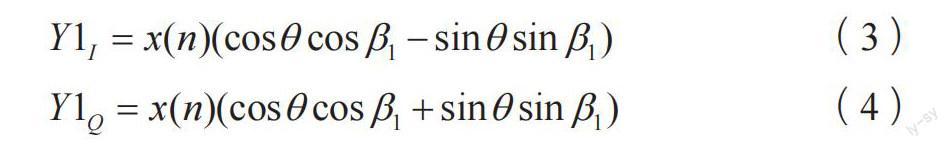

假设中频信号fc 被 AD 采样后为 x(n),与初始 NCO混频相乘,得到基带的 IQ 信号,其中XI=x(n)* cosθ;XQ=x(n)*sinθ;如果将此时的 IQ 信号再次搬移β1的角度,就可以将子带频率f1的频率搬移到零中频的位置,计算为:

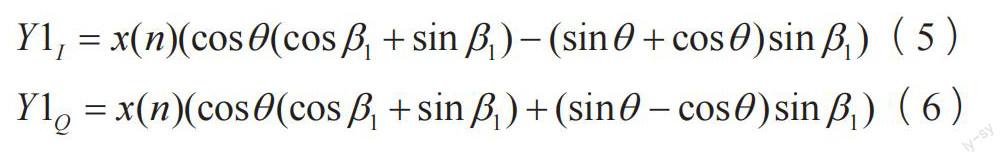

为节省资源,将式(3)和式(4)进行化简组合,每路复数运算由4个乘法器变成3个,得到:

2多路控守FPGA实现方案

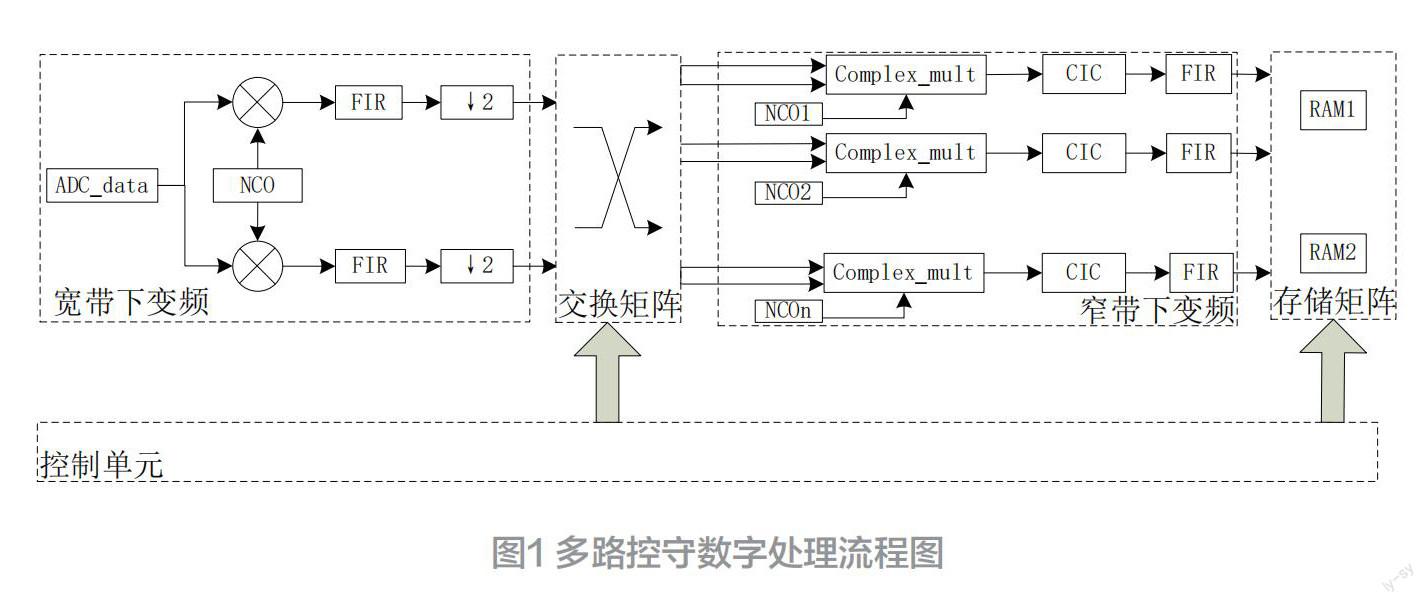

FPGA 内部实现多路窄带控守出自处理流程框图如图1所示。功能单元主要包括宽带下变频器、交换矩阵、窄带下变频器、存储矩阵、控制单元等。

宽带下变频器功能是将输入的 ADC 采样实信号变为零中频 IQ 数据;

交换矩阵是根据要求实现的窄带控守路数及频点,计算数控振荡器 NCO,并输出给窄带下变频器;

窄带下变频器件功能是同时实现64路窄带 IQ 信号输出;

存储矩阵同时将64路窄带信号存储并上传。

2.1宽带下变频器设计

宽带下变频器包括 NCO 单元、乘法器、FIR 滤波器等;

ADC 芯片采样时钟为204.8 MHz, 输入频率范围为(110~170) MHz,ADC 芯片采用 ADI 公司的 ADC9467芯片,最大位宽16 bit,无杂散动态优于75 dBm;

数控振荡器 NCO 生成 sin 与 cos 信号,与 ADC 芯片相乘得到零中频 IQ 信号;为节省芯片的乘法器资源,NCO 设计实现直接使用 ROM 查找表的方式实现;在Matlab中产生采样率为204.8 MHz, 频率为64.8 MHz(超外差接收机为2次混频)的 sin 与 cos 信号,并将数据初始化存储在 FPGA 内 rom 表即可。

乘法器为 AD 信号与 cos 或 sin 信号相乘,实现混频的功能,输出的 I 路和 Q 路信号,信号带宽为24 bit。

FIR 滤波器设计使用的滤波器系数为64阶对称型的的低通滤波器,滤波器Fpass=40 MHz,Apass=0.1 dB ;Fstop=42 MHz,Astop=95 dB;滤波后抽2,将 IQ 数据的采样率降为102.4 MHz,并输出给子信道下变频器控制矩阵,FFT 运算结果满足优于85 dB的无杂散动态范围。

2.2窄带变频器设计

窄带变频器为窄带多路控守系统的核心模块,为实现带内多路任意频点的控守,每个子带变频器都需要1个可配置的子带 NCO 模块、复数乘法器模块、滤波器模块。单路子带变频器的实现框图如下图所示。

ch_nco模块是基于 CORDIC 算法的可配置 NCO 模块,nco值的计算由控制器单元完成。计算公式为:

若子信道的中心频率f1在中心频率fc 的上半部分,则β=f1−fc;

若子信道的中心频率f1在中心频率fc 的下半部分,根据奈奎斯特采样定理,此时的β=fs −(f1−fc);

complex_mult模块为复数乘法器模块,每1路需要消耗3个乘法器资源。

filter_computer_p模块为级联的滤波器,包含了 CIC 和 FIR 滤波器两种,根据输入的ch_bw信号,可选择输出200、100、50、25、15、9、6、1 kHz 等8种带宽的窄带信号。

每1路输出数据格式为16 bit 位宽的 I 和16 bit 位宽的 Q,ch_vld标识当前时钟周期数据有效;

2.3控制单元设计

控制单元主要是完成 DSP 命令解析和子带变频器运算和控制。系统工作过程中,将 DSP 通过Emif接口往 FPGA 下发若干个信道号、每 1 个子信道的中心频率、带宽参数。ch_enable信号分别对应 16 个子带变频器的复位使能信号;ch_nco为对应子带的nco值;ch_bw为各子带变频器输出带宽选择信号。

2.4存储矩阵设计

存储矩阵将64路窄带 IQ 数据存储并上传,传输数据的最大带宽为64路200 kHz, 采样率为带宽的1.28倍;系统工作时钟为102.4 MHz;

64路 IQ 数据进入存储矩阵后,首先将数据根据ch_vld信号锁存;

RAM1与 RAM2两片存储器将数据的进行乒乓存储,保证数据的连续性,存储器容量为128 kBit, 位宽32 bit, 寻址为0-32767,实现每路512点的存储需求;

数据存储格式为地址0-地址63为64路的 I1,Q1;地址64-地址127为64路的 I2Q2;依次存储到 I512Q512;

数据读取上传格式,先取第1路的512点 IQ,地址为0、64、128…,再取第2路的512个点,地址为1、65、129…,依次取出64路。

存 RAM2数据时,RAM1数据通过 SRIOx4接口上传数据到 DSP;存 RAM1数据时,RAM2数据数据上传。

3验证与实现

多路窄带控守系统,使用 FPGA+DSP+ADC 的框架实现; FPGA 芯片使用设计的 Xilinx 公司的 K7系列 XCK7325T;ADC 采集芯片为 ADI 公司的 ADC9467,采样率高达250 MHz,,DSP 芯片采用 TI 公司的 TMS320C6657。FPGA 与 DSP 之间的通信接口包括 EMIF 和 SRIO x4,处理平台的对外接口为千兆以太网。平台组成如图4所示。

系统上电后,首先由应用层软件的宽带信号搜索功能,硬件平台收到指令后,由 FPGA 接收并解析 ADC采样数据,与 NCO(COS,SIN)相乘得到基带的 IQ 信号;并将 IQ 数据进行 FFT 运算,FPGA 并将 FFT 运算后功率谱数据上传;在频谱显示界面可自动或者手动分选要控守的信号频率和分析带宽,并将相应的子带频率与分析带宽下发给硬件平台。

在 FPGA启动多路控守控制模块与 CORDIC 乘法器复数乘法模块,并将对应带宽的数据输出上传。上传后的数据保存在系统本地硬盘中,并使用 Adobe Audition软件验证播放,反复多次存储播放,证明多路控守系统能同时实现64路带宽200 kHz。

4結束语

本文研究了一种基于 CORDIC 算法的可配置的多路窄带控守系统的设计实现,通过在操作终端上文件存储的方式验证能够实现60 MHz 宽带内最多64路的任意频点控守,在工作中由宽带搜索引导多路窄带控守,可对多路窄带信号进行存储、分析;同时所需要的 FPGA内部的乘法器和存储器资源极少。下一步目标优化优链路资源消耗,实现更多通道频点的控守。

参考文献:

[1]张炜,杨虎.基于CORDIC算法的直接数字频率合成器实现方法[J].重庆邮电学院学报(自然科学版),2006,18(5):597-600.

[2]梁杰,孙未.CORDIC算法的优化及硬件实现[J].电子世界,2013(10):1-4.

[3]黄海.基于CORDIC的离散三角变换快速算法及其实现研究[D].哈尔滨:哈尔滨工业大学,2014.

[4]陈婧.改进型CORDIC算法的研究与实现[J].现代电子技术,2011(24):49-55.